MOSFET이란

금속-산화물-반도체 전계효과 트랜지스터(Metal Oxide Semiconductor Field Effect Transistor), 전압제어를 통해 전류원을 생성한다.

공핍형 / 증가형 MOSFET으로 나뉜다.

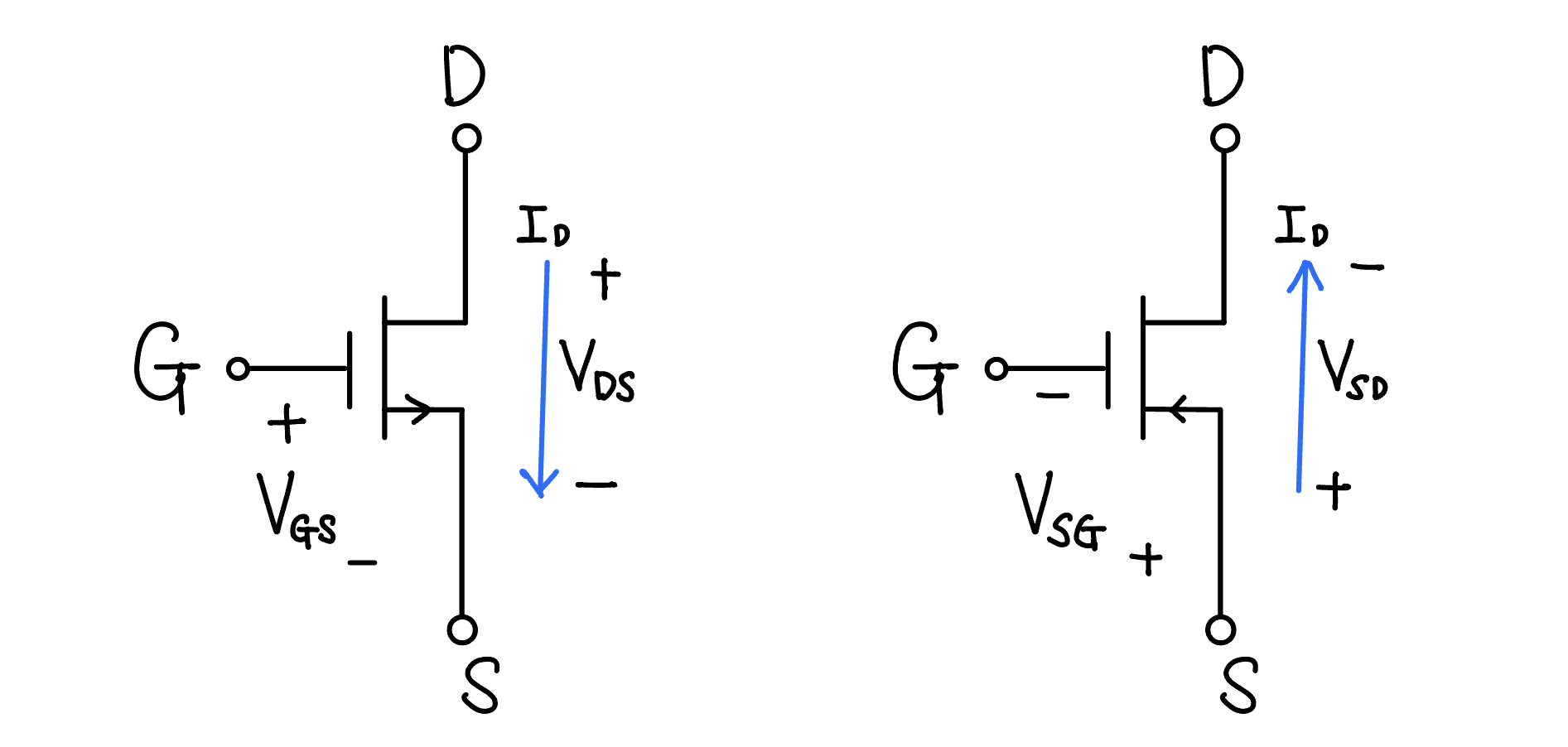

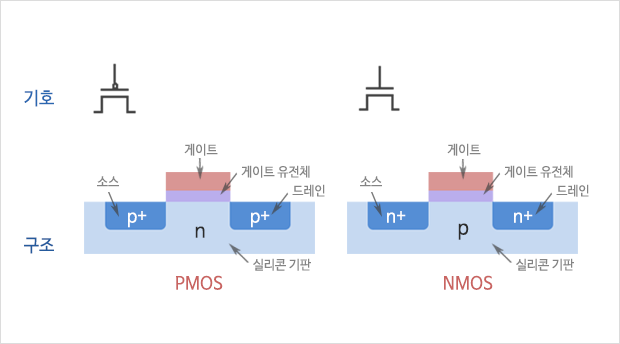

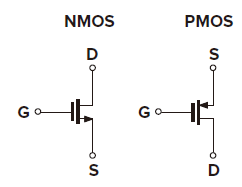

좌 NMOS 우 PMOS

공핍형은 평상시 S-D 사이 채널이 형성되어 전류 흐르다, Gate 닫으면 전류 차단

증가형은 평상시 S-D 채널형성 X, 게이트로 전류를 흐르도록 동작시킴

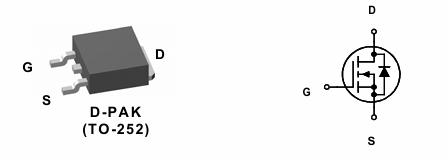

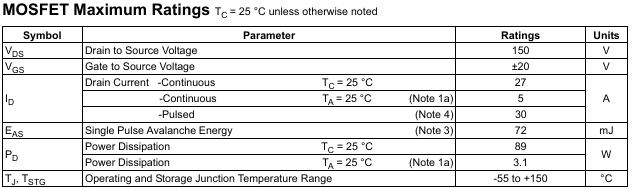

- NMOS Example : FDD86252

증가형 MOSFET (enhancement)

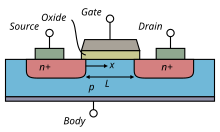

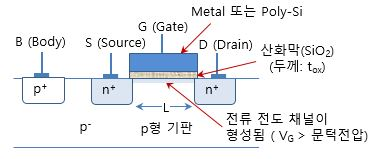

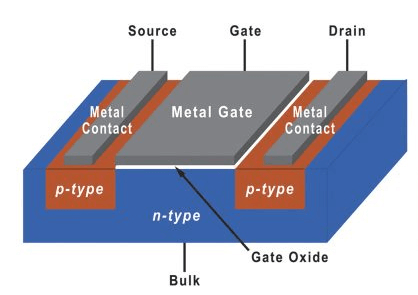

MOSFET 구조

NMOS 구조

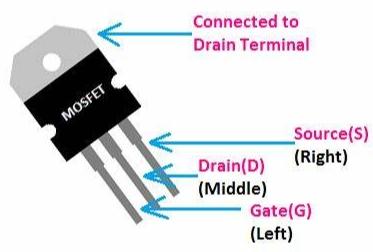

- 소스(S), 게이트(G), 드레인(D) 으로 구성된, pnp 또는 npn 접합 구조

게이트 (Gate)는 소스-드레인 사이 전류를 제어

소스 (source)는 채널을 통하여 흐를 전하 캐리어(N채널 전자, P채널 정공) 공급

드레인 (drain)은 전하 캐리어가 채널을 빠져 나가 소자 밖으로 방출.

- Gate (G) : 전계(Electric Field)를 형성해 채널을 여닫는 전극

Drain (D) : 전류가 빠져나가는 곳

Source (S) : 전류가 들어오는 곳

Body (Bulk) : 기판, 통상적으로 소스에 연결

PMOS 구조

-

정공(h⁺, hole)을 주된 캐리어로 사용하는 FET

게이트 전압이 낮을수록 켜짐, 높은 전압이면 꺼짐 -

정공(h⁺)이 Source → Drain으로 흐르며, 전류는 S → D 방향

하지만 전자 흐름은 Drain → Source 방향으로 이해됨

- N형 기판(N-Substrate) 위에 P형 소스/드레인

게이트는 절연막(SiO₂)으로 전기적으로 절연

게이트 전압이 낮아지면 채널이 형성되어 전류가 흐름

| 조건 | 상태 | 설명 |

|---|---|---|

| (Gate 전압이 Source보다 충분히 낮음) | ON (도통) | 채널 형성됨, 정공 흐름 가능 |

| 또는 | OFF (차단) | 채널 형성 안 됨 |

- 게이트 전압 조건

PMOS는 NMOS와 반대로, 게이트에 음전압을 인가해야 ON

예: Source = +5V일 때, 게이트가 0V면

𝑉𝐺𝑆 = −5V → ON

| 항목 | PMOS |

|---|---|

| 캐리어 | 정공 (hole) |

| 기판 | N형 |

| ON 조건 | (게이트가 더 낮아야 함) |

| 전류 방향 | Source → Drain (정공 흐름) |

| 전도 성능 | NMOS보다 낮음 (정공 이동도↓) |

| 소자 크기 | NMOS보다 커야 같은 전류 확보 가능 |

| 고측 스위칭 | 간단한 드라이버로 사용 가능 |

| 회로 용도 | LDO, CMOS 풀업, 전원 스위치 등 |

NMOS & PMOS 동작원리

NMOS (n-type MOSFET)

전류 흐름 : Source → Drain (전자 흐름 기준은 Drain → Source)

-

동작 조건 :

턴 ON : 𝑉𝐺𝑆 > 𝑉th

턴 OFF : 𝑉𝐺𝑆 < 𝑉th -

회로 해석 예시

Source가 GND일 때, Gate에 3.3V → ON (채널 생성)

Gate가 0V일 때 → OFF

PMOS (p-type MOSFET)

전류 흐름 : Drain → Source

-

동작 조건 :

턴 ON : 𝑉𝐺𝑆 < 𝑉th

턴 OFF : 𝑉𝐺𝑆 > 𝑉th -

회로 해석 예시

Source가 VDD일 때, Gate가 GND → ON

Gate가 VDD와 같으면 → OFF

기본 구조 및 동작 원리

| 항목 | NMOS | PMOS |

|---|---|---|

| 캐리어 | 전자(e⁻) | 정공(h⁺) |

| 구조 | p형 기판에 n형 소스/드레인 | n형 기판에 p형 소스/드레인 |

| ON 조건 | Gate 전압 > Source 전압 | Gate 전압 < Source 전압 |

| OFF 조건 | Gate 전압 ≤ Source 전압 | Gate 전압 ≥ Source 전압 |

| 전류 방향 | Source → Drain (전자 이동) | Source → Drain (정공 이동) |

| 스위칭 속도 | 빠름 (전자 이동이 빠름) | 느림 (정공 이동이 느림) |

요약 비교표

| 구분 | NMOS | PMOS |

|---|---|---|

| 기판 타입 | p형 | n형 |

| Major Carrier | 전자 | 정공 |

| ON 조건 | ||

| 사용 위치 | Low-side | High-side |

| 스위칭 속도 | 빠름 | 느림 |

| 이동도 | 높음 (μₙ) | 낮음 (μₚ) |

| 용도 예 | 인버터 하단, MOSFET 스위치 | 인버터 상단, LDO pass element |

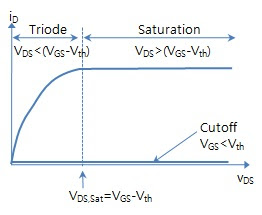

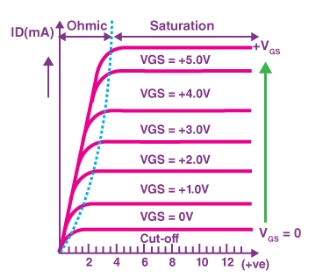

동작영역

문턱전압 Vth (threshold voltage) : 채널을 형성하는 최소 게이트 전압

차단영역 (Vgs < Vth)

- 채널이 형성되지 않는 영역, ID=0. (open)

소스에 있는 전자 중에서 에너지가 높은 일부 전자들이 채널로 들어가서 드레인으로 흐르는 누설전류 존재. (이상적으로는 전류 X)

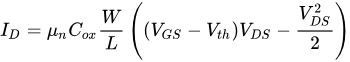

선형 (비포화 영역, Triode) (Vgs-Vth > Vds)

- 게이트가 열려 채널이 형성되어 드레인과 소스사이에 전류가 흐름 (Closed)

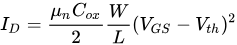

포화영역 (Saturation) (Vgs-Vth <= Vds)

-

핀치오프 현상 발생하여 드레인 전압이 커져도 드레인 전류 일정함.

-

(Pinch-off 현상 : 게이트 전압의 전계와 드레인 전압의 전계가 서로 상쇄되어, 드레인 근처에서 채널이 형성되지 않음 (공핍층). 따라서 전류가 흐르지 않음, 드레인 부근의 강한 전계에 의해, 전자가 빠르게 드레인으로 끌려가는 현상이 발생하여 드레인 전압이 전류에 영향 X)

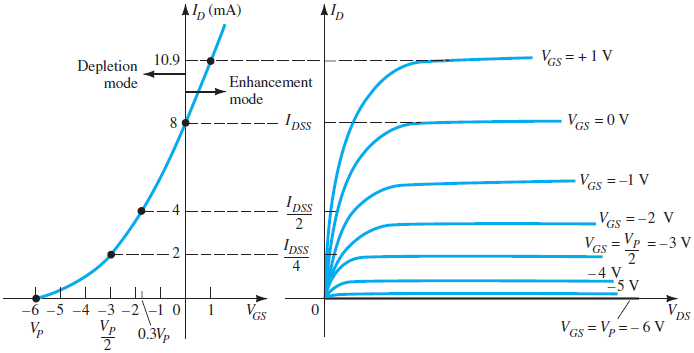

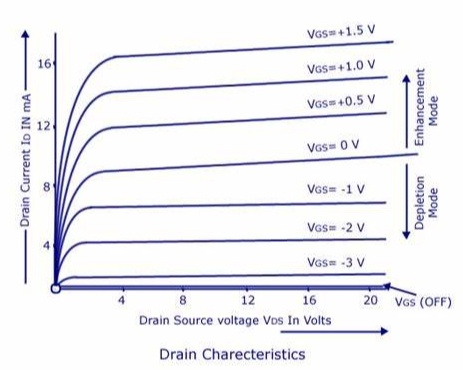

공핍형 MOSFET (Depletion)

공핍형은 소스와 드레인 사이에 있는 채널이 평상시에 형성이 되어 있어서 전류가 흐르다가, 게이트를 닫아주면 전류가 차단되는 형태

Depletion NMOS 특성

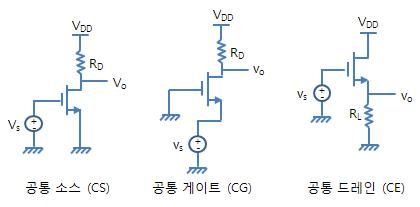

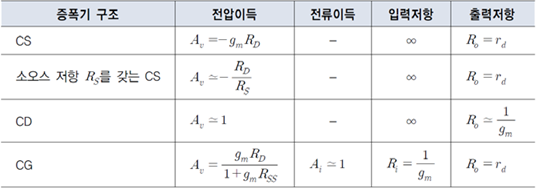

MOSFET 증폭기

| 증폭기 종류 | 공통 단자 | 특징 |

|---|---|---|

| 공통 소스 (Common Source, CS) | 소스 | 전압·전력 증폭에 적합 (가장 일반적) : 높은 전압 이득, 위상 반전 |

| 공통 드레인 (Common Drain, CD) | 드레인 | 버퍼 증폭기 (소스 팔로어) : 낮은 출력 임피던스, 전압 이득 없음 |

| 공통 게이트 (Common Gate, CG) | 게이트 | 고주파 증폭에 적합 : 위상 유지, 낮은 입력 임피던스 |

트랜스 컨덕턴스 gm = dID / dVgs

증폭이득, 전압 → 전류 증폭 능력

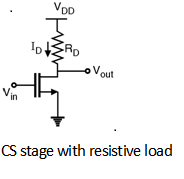

공통 소스 증폭기 (CS: Common Source Amplifier)

-

회로 구성

입력: Gate

출력: Drain

공통 단자: Source (접지) -

특징

높은 전압 이득

위상 반전 있음

가장 널리 쓰이는 증폭기 구조

동작 특성

| 항목 | 설명 |

|---|---|

| 전압 이득 | 큼 (최대 수십 배), |

| 위상 | 180도 반전 |

| 입력 임피던스 | 매우 높음 (게이트는 전류 거의 안 흐름) |

| 출력 임피던스 | 중간 정도 () |

| 주 용도 | 일반적인 전압 증폭기 (오디오, 센서 증폭 등) |

특성표

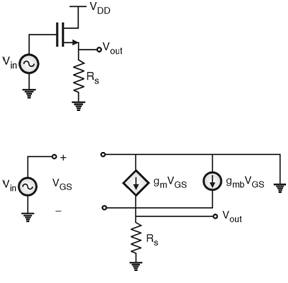

공통 드레인 증폭기 (CD: Common Drain Amplifier, Source Follower)

- 회로 구성

입력: Gate

출력: Source

공통 단자: Drain (접지 또는 전원 연결)

- 특징

전압 이득은 거의 없음

출력 임피던스가 낮아 전류 구동력이 큼

고임피던스 입력 신호를 저임피던스로 전달할 때 유리

동작 특성

| 항목 | 설명 |

|---|---|

| 전압 이득 | 약 1 (, 약간 < 1) |

| 위상 | 무위상 (동상) |

| 입력 임피던스 | 매우 높음 |

| 출력 임피던스 | 매우 낮음 |

| 주 용도 | 버퍼 앰프, 임피던스 매칭 용도 |

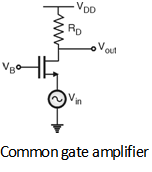

공통 게이트 증폭기 (CG: Common Gate Amplifier)

-

회로 구성

입력: Source

출력: Drain

공통 단자: Gate (고정 바이어스) -

특징

높은 대역폭

고속 회로에 적합

위상 반전 없음

동작 특성

| 항목 | 설명 |

|---|---|

| 전압 이득 | 큼, |

| 위상 | 무위상 (동상) |

| 입력 임피던스 | 매우 낮음 () |

| 출력 임피던스 | 중간 |

| 주 용도 | 고주파 회로, 저임피던스 소스 수신 (예: RF 안테나 전단) |

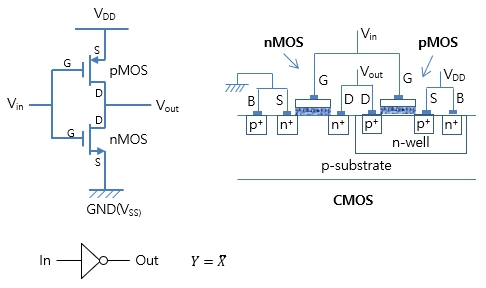

CMOS (Complementary MOS)

- 하나만 켜짐. VDD-GND Path 항상 끊어져 Static power 낮아짐

- noise margin 큼. 항상 VDD-GND 연결 -> 0 or 1

- operating 속도 빠름

CMOS 인버터 회로

-

NMOS

Pull down network, Gate +전압 인가시 ON

Low level : 그대로

High level : VDD-VTH -

PMOS

Pull up network, Gate -전압 인가시 ON

Low level : VTH

High level : 그대로

Ref

https://ko.wikipedia.org/wiki/MOSFET

http://www.ktword.co.kr/test/view/view.php?no=3630

https://mathphysics.tistory.com/m/476

https://gdnn.tistory.com/89

http://www.ktword.co.kr/test/view/view.php?m_temp1=5836&id=1461

https://www.onsemi.com/pdf/datasheet/fdd86252-d.pdf

https://andy-power.blogspot.com/2018/11/n-mosfet-tr.html#google_vignette

https://www.ariat-tech.kr/blog/mosfet-definition,working-principle-and-selection.html

MOSFET 증폭기

http://www.ktword.co.kr/test/view/view.php?no=4574

https://e-circuit.tistory.com/49

https://www.electronics-tutorial.net/Analog-CMOS-Design/MOSFET-Amplifiers/

Becoming an uno online master requires a combination of luck, strategy, and the ability to read your opponents