05. MIPS single-cycle microacrchitecture

MIPS Multi-Cycle Architecture

1. 기본 개념

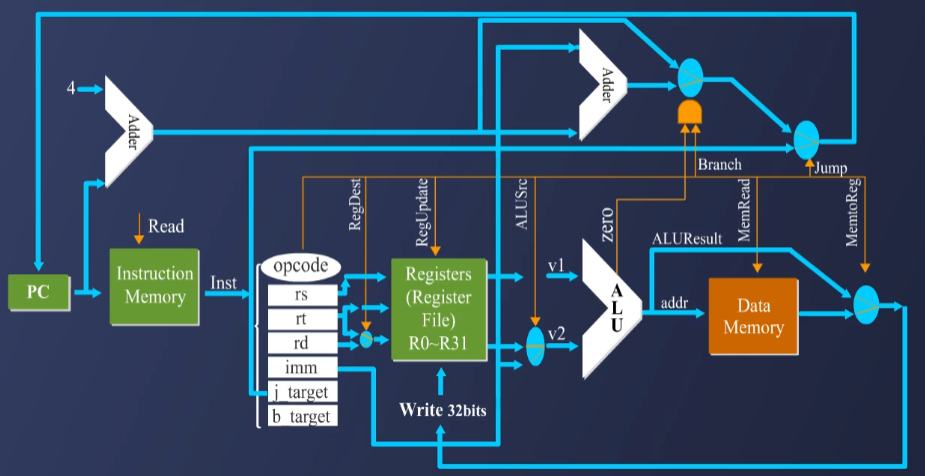

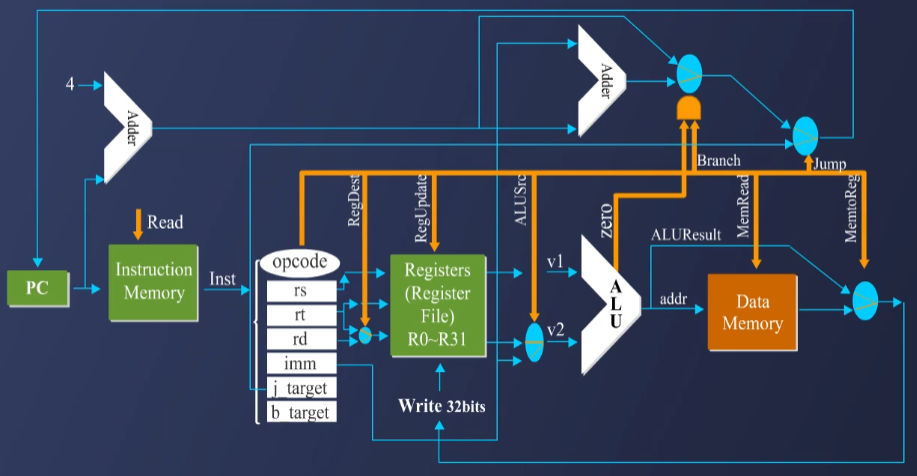

- Datapath / Controlpath:

- 데이터 경로와 제어 경로를 분리하여 구현.

- 데이터 경로는 명령어와 데이터를 처리하며, 제어 경로는 각 단계의 동작을 제어.

- 사진 자료가 포함될 예정으로 자세한 설명은 생략.

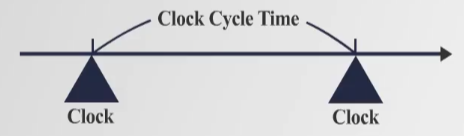

- Clock Cycle Time / Clock:

- Clock:

- 주기적인 하드웨어 이벤트로 모든 하드웨어 컴포넌트에 신호를 전달.

- 작업 시작 및 종료를 정의.

- Clock Cycle Time:

- 클럭 주기의 길이를 의미하며, 명령어 실행에 필요한 시간을 결정.

2. Single-Cycle Microarchitecture

- Clock:

- 특징:

- 모든 명령어가 동일한 클럭 사이클 시간을 사용.

- 명령어가 하나의 클럭 사이클 내에서 실행 완료.

- 실생 시간 공식:

- Execution Time = # of executed instructions * Clock Cycle Time

- 단점:

- 모든 명령어가 동일한 클럭 사이클 시간을 사용하므로 복잡한 명령어도 단순한 명령어와 동일한 시간을 소비.

- 실행 시간이 비효율적일 수 있음.

3. Multi-Cycle Microarchitecture

- 특징:

- 명령어마다 다른 클럭 사이클을 사용.

- 명령어의 복잡도에 따라 필요한 클럭 사이클 수가 다름.

- 실행 시간 공식:

- Execution Time = # of executed instructions * Clock Cycle Time

- 장점:

- 단순한 명령어는 더 적은 클럭 사이클을 사용하여 실행 시간을 단축.

- 복잡한 명령어는 필요한 만큼의 클럭 사이클만 사용.

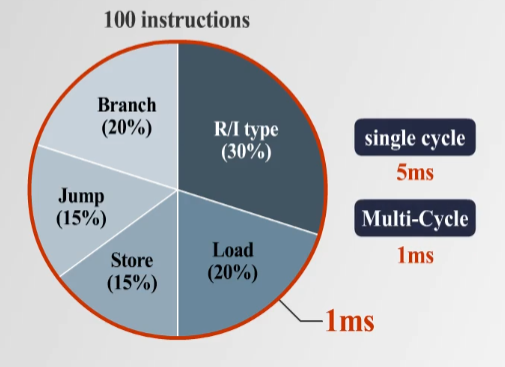

4. 실행 시간 비교

- Single-Cycle Machine:

- 명령어 100개 실행.

- Clock Cycle Time: 5ms

- 실행 시간:

- 100 cycles * 5ms = 500ms

- Multi-Cycle Machine:

- 명령어 1개씩 R-Type, Load, Store, Jump, Branch 실행.

- Clock Cycle Time: 1ms

- 실행 시간:

- (4 + 5 + 4 + 2 + 3) * 1ms = 310ms

- 비교 결과:

- Multi-Cycle Machine이 더 적은 실행 시간을 소모하며 효율적.

Multi-Cycle Microarchitecture

1. Multi-Cycle Microinstructions

- 특징:

- 명령어 실행이 여러 클럭 사이클에 걸쳐 수행됨.

- 부분 실행 상태(Partial Execution State)를 기억하여 실행 진행 상황을 추적.

- 명령어 실행의 각 단계는 독립적으로 진행.

- 명령어 실행 단계:

- Cycle 1: Fetch

- 명령어를 메모리에서 가져옴.

- Cycle 2: Decode & Register Fetch

- 명령어를 해독하고, 필요한 레지스터 값을 읽음.

- Cycle 3: ALU

- ALU 연산 수행 (산술/논리 연산, 주소 계산 등).

- Cycle 4: Memory Access

- 메모리 접근 단계.

- 메모리 읽기 또는 쓰기가 완료되기까지 수백 사이클이 소요될 수 있음.

- Cycle 1: Fetch

2. Multi-Cycle Microarchitecture 특징

- Control Logic과 유사한 동작:

- 하드웨어를 제어하는 신호를 생성.

- 특정 하드웨어(예: ALU, 메모리, 레지스터)를 작업에 맞게 동작시킴.

- 하드웨어 사용 방식:

- 각 클럭 사이클마다 필요한 부분의 하드웨어만 사용.

- 자원을 효율적으로 분배하여 병목 현상을 줄임.

3. Multi-Cycle Architecture의 장점

- 자원 효율성:

- 단일 사이클에서 전체 하드웨어를 사용하는 대신, 필요한 부분만 사용하여 하드웨어 자원의 낭비를 줄임.

- 유연성:

- 명령어의 실행 단계를 분리하여 복잡한 명령어도 효율적으로 처리 가능.

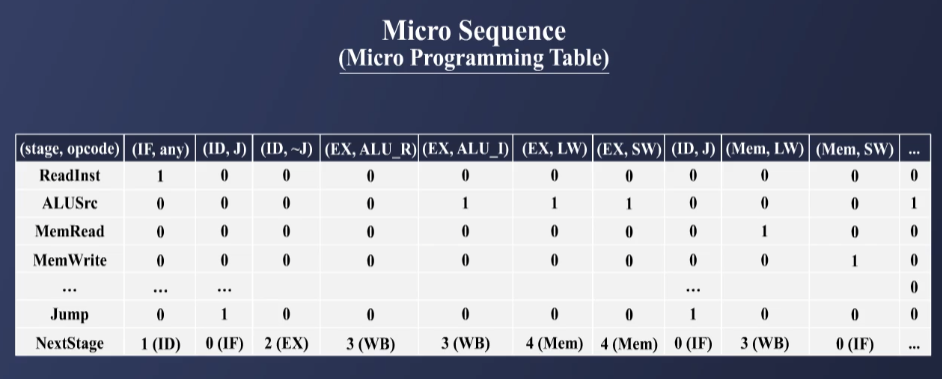

Micro Sequence (Micro Programming Table) 요약

- 구조

- Stage (단계): 명령어 실행 단계 (IF, ID, EX, Mem, WB).

- Control Signals (제어 신호): 하드웨어 동작을 제어하는 신호 (ReadInst, ALUSrc, - MemRead, MemWrite, Jump 등).

- NextStage (다음 단계): 현재 단계가 끝난 후 이동할 다음 단계.

- 주요 제어 신호

- ReadInst: IF 단계에서 명령어를 메모리에서 읽음.

- ALUSrc: EX 단계에서 ALU 입력으로 즉시값(Immediate) 사용 여부를 결정.

- MemRead: Mem 단계에서 메모리 읽기 (Load 명령어).

- MemWrite: Mem 단계에서 메모리 쓰기 (Store 명령어).

- Jump: ID 또는 EX 단계에서 Jump 명령어 실행.

- 실행 흐름

- IF → ID → EX → Mem (필요 시) → WB

- 각 단계에서 필요한 제어 신호만 활성화.

- 의미

- Multi-Cycle Microarchitecture에서 명령어 실행 단계별 제어 신호와 동작을 명확히 정의.

- 하드웨어 자원을 효율적으로 사용.