3-1 예습_컴퓨터 구조

1.컴퓨터 구조_1

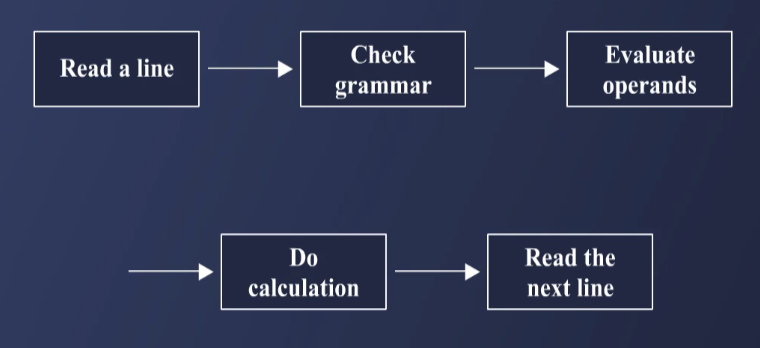

Read a Line:명령어를 한 줄 읽어옴.Check Grammar:OPcode: 연산자를 확인.지원 연산자: +, -, \*, /, M (Move).Operands: 두 개의 피연산자를 확인.형식:operand1, operand2Prefix: R (Register)

2.컴퓨터 구조_2

Definition:명령어는 비트스트림(bitstream) 형태로 이루어져 있음 (0과 1의 조합).이 비트스트림은 머신 코드(machine code)로 변환되어 CPU가 실행하는 명령이 됨.Von Neumann Structure:폰 노이만 구조에서는 명령어(instr

3.컴퓨터 구조_3

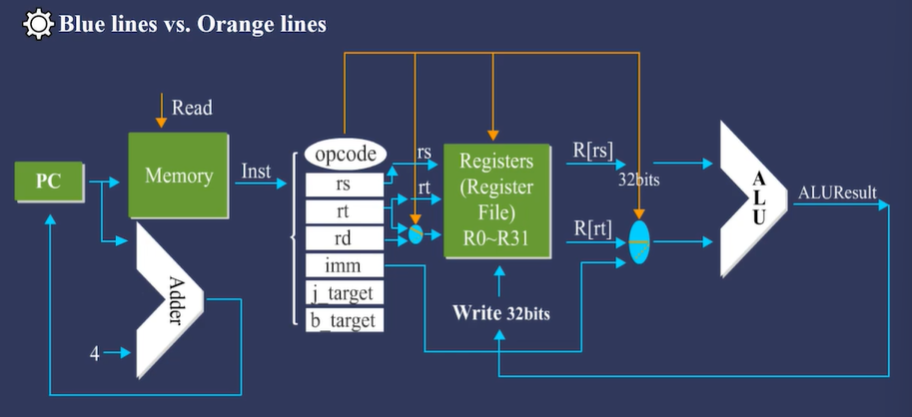

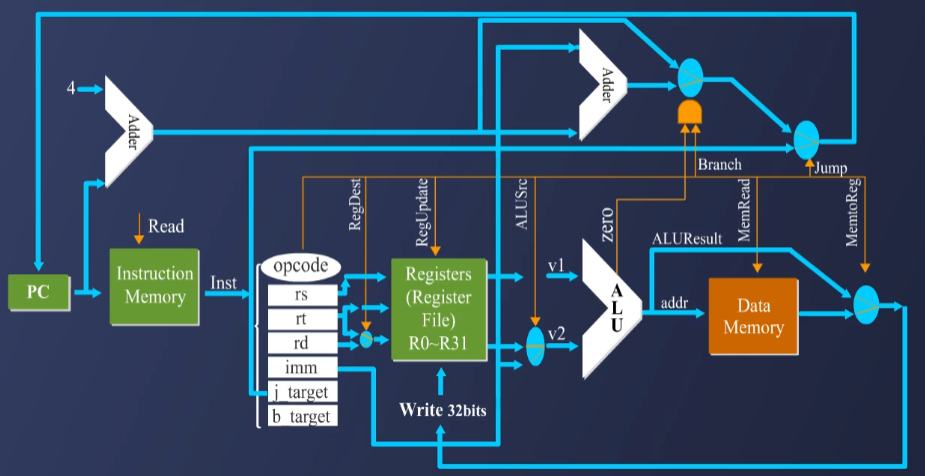

CPU 내부에서 데이터가 흐르는 경로를 나타냄. 명령어, 레지스터 값, ALU 결과 등의 흐름을 포함.주요 구성 요소:Program Counter (PC): 현재 실행 중인 명령어의 메모리 주소를 저장.Instruction Memory: 실행할 명령어를 저장.Regis

4.컴퓨터 구조_4

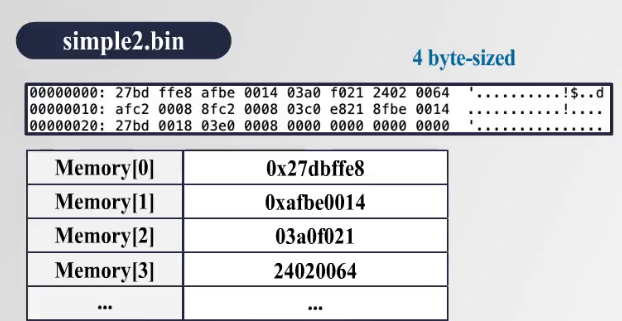

메모리와 레지스터 초기화:PC (Program Counter): 명령어 실행 시작 주소를 나타내는 변수.레지스터: MIPS는 32개의 32비트 레지스터를 사용스택 포인터 (R29):초기값: 0x80000 (스택의 최상단 주소).리턴 주소 (R31):초기값: 0xFFFF

5.컴퓨터 구조_5

Datapath / Controlpath:데이터 경로와 제어 경로를 분리하여 구현.데이터 경로는 명령어와 데이터를 처리하며, 제어 경로는 각 단계의 동작을 제어.사진 자료가 포함될 예정으로 자세한 설명은 생략.Clock Cycle Time / Clock:Clock:주기

6.컴퓨터 구조_6

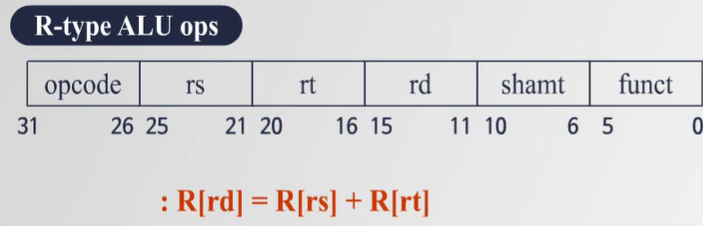

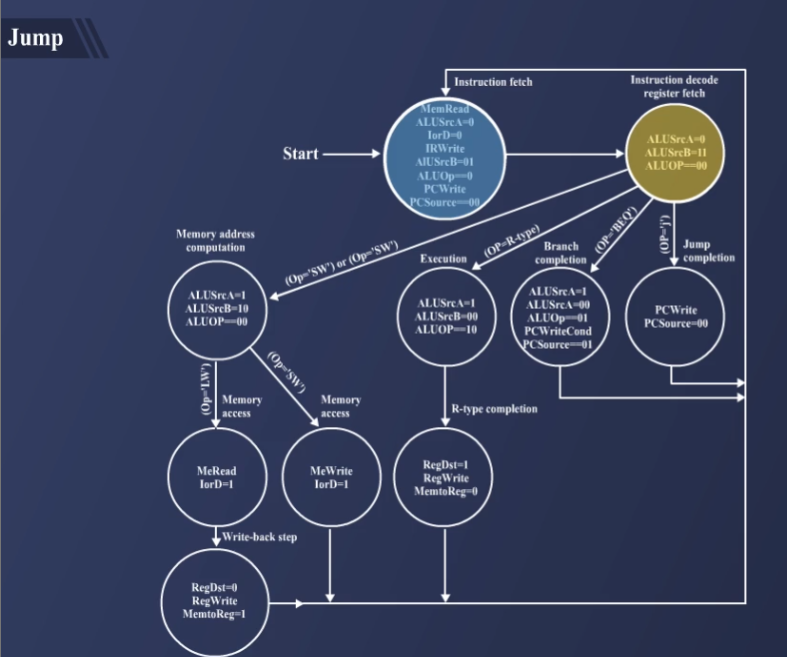

Jump:Instruction Fetch → Instruction Decode → Jump Completion으로 진행.프로그램 카운터(PC)를 갱신하여 제어 흐름을 변경.R-Type ALU:Instruction Fetch → Instruction Decode → Ex

7.컴퓨터 구조_7

08. Pipelined MIPS - latched execution Pipelined Microarchitecture and Instruction-Level Parallelism (ILP) 1. Single Cycle vs Multi Cycle Machines

8.컴퓨터 구조_8

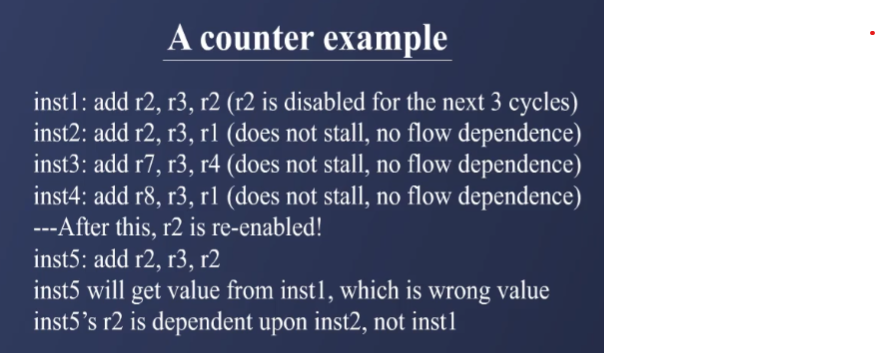

두 개의 명령어가 동일한 레지스터 값을 사용하는 경우 발생.결과 값이 올바른 실행 순서를 따르도록 보장해야 함.RAW (Read After Write) - 진짜 종속성이전 명령어가 값을 쓰기(write) 전에 다음 명령어가 읽기(read)하면 오류 발생.해결 방법: F

9.컴퓨터 구조_9

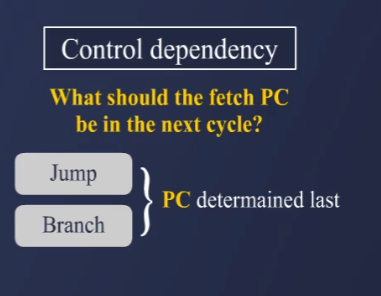

Control Dependency는 Jump, Branch 같은 명령어가 실행될 때 다음 실행될 PC(Program Counter) 값을 예측하기 어려운 문제를 의미합니다.즉, 명령어의 흐름(Control Flow)이 변경될 가능성이 있을 때, 올바른 명령어를 예측하는

10.컴퓨터 구조_10

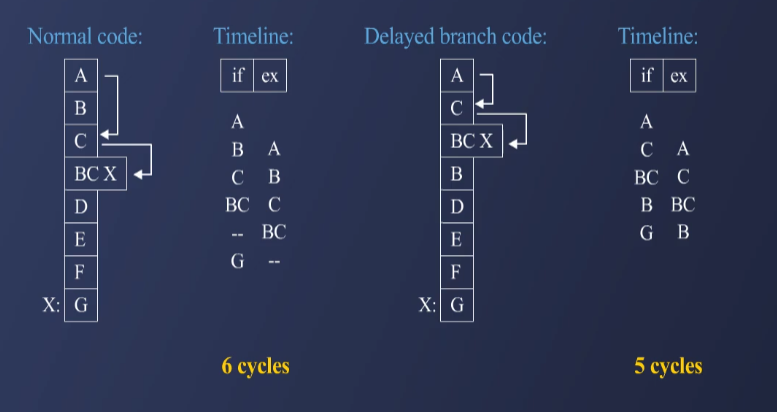

Delayed Branching 기법은 분기 명령어(Branch Instruction)의 실행을 몇 사이클 뒤로 미루는 방식으로, 해당 시간 동안 다른 명령어를 채워넣어 stall을 방지하는 기법이다.분기 명령어 실행 후의 지연 슬롯(Delay Slot)에 반드시 실행