03. Instruction Set Architecture and MIPS ISA

MIPS ISA (Instruction Set Architecture)

Instruction Overview

- Definition:

- 명령어는 비트스트림(bitstream) 형태로 이루어져 있음 (0과 1의 조합).

- 이 비트스트림은 머신 코드(machine code)로 변환되어 CPU가 실행하는 명령이 됨.

- Von Neumann Structure:

- 폰 노이만 구조에서는 명령어(instruction)가 메모리에 저장됨.

- Instruction Representation:

- MIPS는 fixed bitstream 구조를 사용해 고정된 크기의 명령어를 가짐.

- 다른 ISA는 다양한 크기의 명령어를 가질 수 있음.

- 예시:

- 0x27bdffe8이라는 명령어는 컴퓨터가 읽을 때 addi r29, r29, -0x18 (어셈블리 코드)로 해석됨.

MIPS ISA Features

- Simplicity:

- 간단한 구조를 가짐.

- 32개의 범용 레지스터(r0 ~ r31)를 사용.

- Fixed Design:

- 고정된 명령어 크기.

- 명령어 내 Opcode(연산 코드)의 위치도 고정.

Instruction Types in MIPS

-

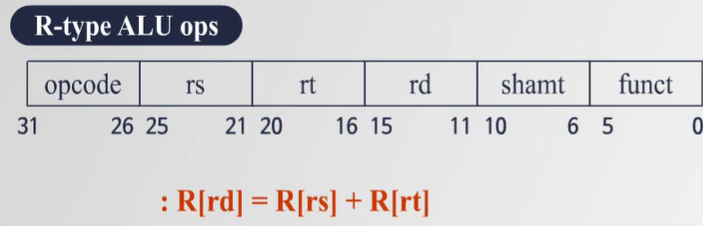

R-Type (Register Type):

- ALU 연산에 사용.

- 레지스터 간 연산 수행.

-

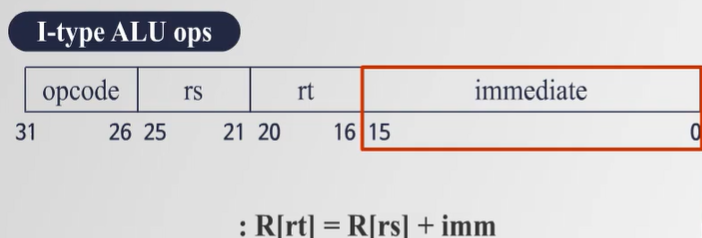

I-Type (Immediate Type):

-

ALU Ops: 즉시 값(immediate)을 사용하는 연산.

-

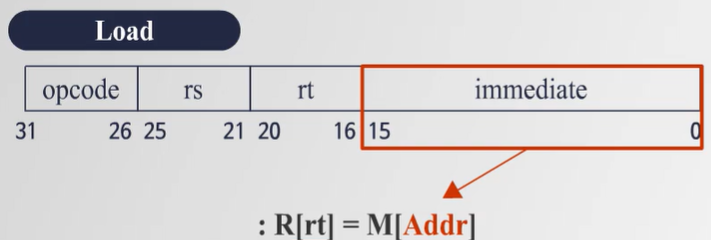

Load: 데이터를 메모리에서 레지스터로 로드.

-

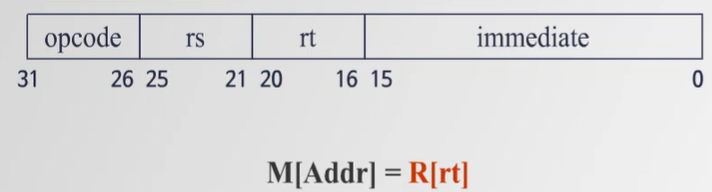

Store: 데이터를 레지스터에서 메모리로 저장(레지스터 값은 변경되지 않음).

-

-

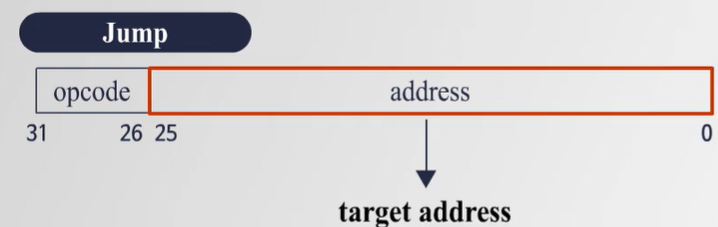

J-Type (Jump Type):

- 프로그램 흐름을 변경하는 점프(jump) 명령어.

-

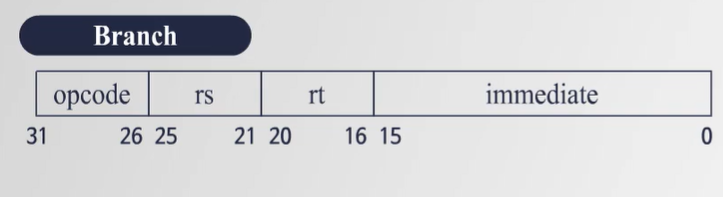

Branch:

- 특정 조건이 충족되었을 때 명령어 흐름을 분기(branch).

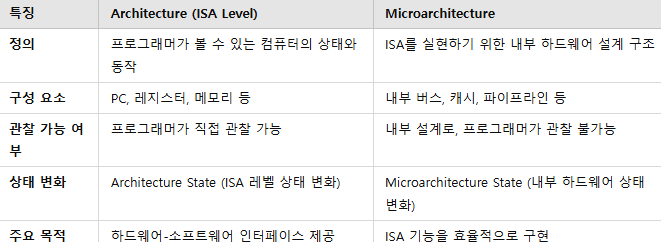

Architecture vs Microarchitecture

1. Architecture (ISA Level)

- Definition:

- ISA (Instruction Set Architecture)는 프로그래머가 볼 수 있는 컴퓨터의 상태와 동작을 정의.

- 컴퓨터의 하드웨어-소프트웨어 인터페이스 역할.

- Key Features:

- Programmer's Visible State: 프로그래머가 직접 접근하거나 제어할 수 있는 상태.

- PC (Program Counter): 현재 실행 중인 명령어의 메모리 주소를 저장.

- Registers: CPU의 레지스터 파일에 포함된 r0 ~ r31 (32개 레지스터).

- Memory: 프로그램 데이터 및 명령어가 저장되는 공간.

- Programmer's Visible State: 프로그래머가 직접 접근하거나 제어할 수 있는 상태.

- Architecture State:

- ISA 레벨의 상태 변화를 관찰 가능.

- 프로그래머가 볼 수 있는 컴퓨터의 구조는 ISA 레벨에 해당.

2. Microarchitecture

- Definition:

- 컴퓨터 내부의 하드웨어 구현 구조를 나타냄.

- ISA에 정의된 기능을 어떻게 구현할지에 대한 내부적인 설계.

- Key Features:

- Internal Hardware Structure:

- 하드웨어 구성 요소 간의 연결과 상호작용 방식을 정의.

- Internal Hardware Structure:

- Microarchitecture State:

- ISA 수준에서 관찰할 수 없는 내부 상태와 동작.

- 예: 파이프라인 레지스터, 캐시 메모리, 내부 버스.

- Hardware Implementation:

- ISA의 명령어와 동작을 실현하기 위한 내부 설계 방식.

Internal Implementation of Microarchitecture

-

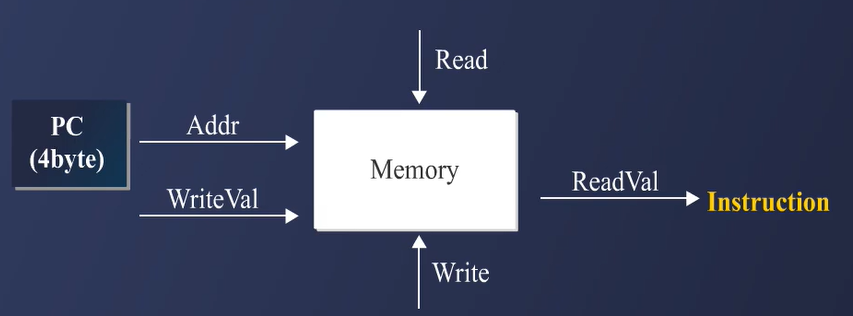

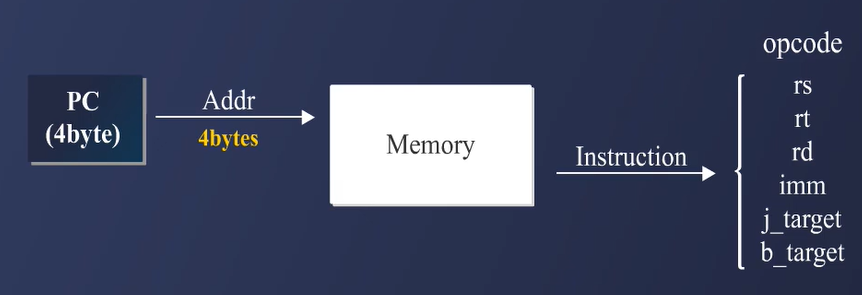

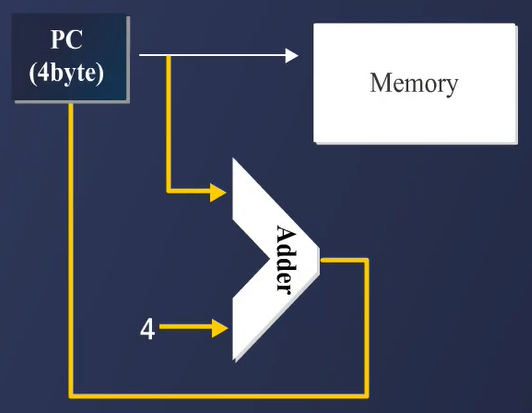

Program Counter (PC):

- 4바이트 크기의 레지스터로, 명령어의 주소를 저장.

-

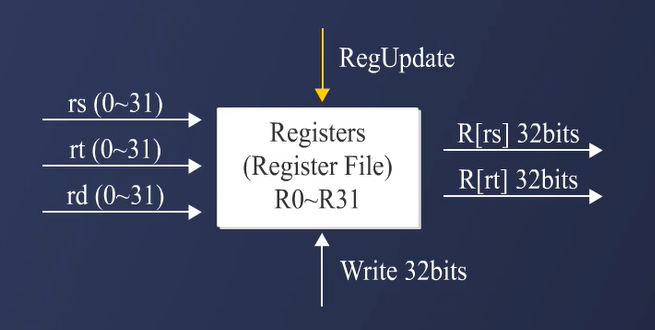

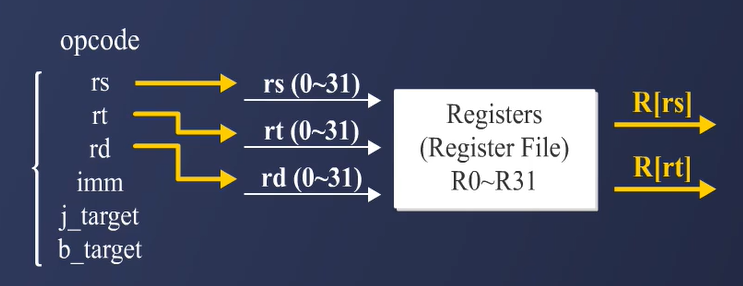

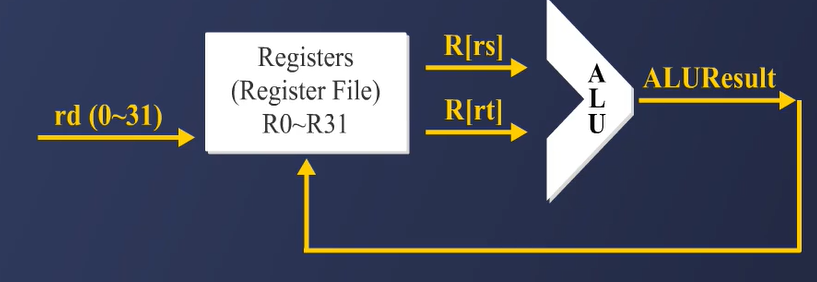

Registers (Register File):

- 32개의 범용 레지스터(r0 ~ r31).

- 명칭 및 기능:

- rs: 소스 레지스터.

- rt: 타겟 레지스터.

- rd: 결과값을 저장하는 레지스터.

- 각 레지스터는 32비트 크기로 구성됨.

- 표현 방식: R[rs], R[rt] 등.

-

Memory:

- 명령어와 데이터를 저장하며, CPU와 상호작용.

Single-Cycle MIPS CPU Simulator

프로젝트 개요

- 목적:

- Single-cycle MIPS 프로세서를 시뮬레이션하여 MIPS 바이너리 프로그램 실행.

- 각 클럭 사이클마다 아키텍처 상태 변화를 출력.

- 외(Exception)를 안정적으로 처리.

MIPS CPU 시뮬레이터 주요 기능

- 메모리와 프로그램 로딩

- 메모리 구현: 큰 배열과 같은 데이터 구조로 표현.

- 바이너리 로딩: MIPS 바이너리 프로그램을 메모리에 로드하여 실행 준비.

- 레지스터 초기화

- r0 ~ r28: 초기값 0.

- sp(r29): Stack Pointer, 초기값 0x8000.

- ra(r31): Return Address 레지스터.

- 프로그램은 주소 0x0에서 시작.

- 명령어 실행 단계

- Fetch → Decode → Execution → Load/Store → Write Back.

- 명령어를 메모리에서 가져와 연산하고 결과를 레지스터에 기록.

- Single-Cycle 시뮬레이션

- 모든 실행 단계가 한 클럭 사이클 안에 완료.

- 클럭 카운트는 명령어 실행이 완료된 후 증가.

실행 및 출력 요구 사항

- 실행 흐름:

- 프로그램 시작 주소(0x0)에서 첫 명령어를 실행.

- 상태 출력:

- 각 사이클 종료 시 이전 상태와 달라진 아키텍처 상태를 출력.

- 최종 출력:

- 프로그램 실행 종료 후 계산된 최종 결과 출력.