The Central Processing Unit (CPU)

operator (or instruction)을 해석하여 실행하는 장치로 컴퓨터의 두뇌에 해당한다.

- ALU, Register, Control Unit(or Execution Unit)으로 구성된다.

(이들 3가지만으로 구성된 CPU의 핵심구성요소를 core라고 부르며, CPU는 이 외에도 cache memory, internal bus 등을 포함하고 있음)

참고 : Core

각종 연산을 하는 CPU의 핵심요소이다.

- ALU, Register, Control Unit을 가르킨다.

참고 : Microprocessor

MPU(Micro Processor Unit), Micro-processor라는 용어가 혼용된다.

과거 CPU는 여러개의 칩으로 만들어졌으나 현재는 대부분 one-chip으로 구현되기 때문에 micro-processor(하나의 칩으로 구현된 CPU)와 혼용되어 사용됨. (CPU는 인텔이, MPU는 모토로라가 사용하던 용어)

프로세서(instruction을 처리하는 logic circuit) 중 디바이스의 중심이 되는 것을 cpu라고 부르고, 보조적 역할의 processor는 co-processor라고 부른다. (그래픽카드가 일종의 co-processor)

참고 : Micro Controller Unit (MCU)

CPU의 기능을 하는 핵심 장치와 그 주변 장치(memory and IO port)들을 포함하고 있는 통합형 칩셋을 말한다. 보통 고성능의 연산이 필요하지 않으면서 제어 기능이 필요한 분야에서 사용된다.

MCU 하나 만으로도 LED나 motor등의 다른 부품들을 control할 수 있다.

밥솥 등과 같은 전자제품들의 제어를 위한 부품으로 사용되기 때문에 컴퓨터에서 사용되는 Microprocessor에 비해 매우 낮은 연산능력의 저가의 제품이 대부분이다.

Arithmetic and Logic Unit (ALU)

instruction에 따라 데이터에 대해 산술 연산 (arithmetic operation, 덧셈, 뺄셈, 나눗셈, 곱셈 등)과 논리 연산 (logic operation, AND, OR, XOR)을 수행하는 소자

Control Unit

storage에서 main memory로 data를 load하는 명령어, main memory에서 storage로 data를 save하는 명령어, 특정 address로부터 instruction을 로딩하는 명령어 등에 따라 명령을 내리는 장치

-

Program counter가 가르키는 address에서 수행할 명령어를 fetch하고

-

fetch된 instruction을 decode하여 execute (실행)한다.

instruction에 따라, memory와 ALU, I/O device에 제어 신호를 보내고 해당 장치들로부터 신호를 받아 다음 처리를 제어한다.

Random logic으로 구현할 수 있지만 microcode (microinstruction을 지원하는 memory (=writable ROM 이용)로 구현된 방식) 방식으로 구현되는 경우가 많다.

microcode로 구현된 traffic control은 다음과 같은 memory로 만들어진다.

-

instruction의 opcode, mode, counter 등의 조합을 address로 삼고

-

해당

address(실제로는 특정 instruction)에 해당하는 적절한 signal을 출력하는 memory -

control에 사용되는 여러 signal들 각각을 하나의 state라고 보고 해당 state에 address를 할당한 일종의 state-machine이다.

control unit을 만들기 위해 여러 microcoded block이 사용될 수 있고, 하나의 microcoded block을 만들기 위해 nanocoded block들이 사용될 수 있다.

Register

주로 CPU내에서 data를 저장하고 있는 memory를 가르킨다. 가장 빠른 memory이며 CPU의 구성요소이다.

condition code register: overflow, underflowprogram counter (pc): 다음 수행할 instruction이 저장된 메모리 위치를 가르킨다.accumulator: ALU의 operation의 result가 저장되는 register이다.address extension register: 주소확장레지스터, MSB를 포함하는 상위주소 부분을 지정하는 데에 사용된다.index register: relative addressing에서 사용되는 레지스터. 현재 address에 더해질 값을 가지고 있다.indirect address register: memory에서 읽어들인(fetched) indirect address를 저장하고 있는 register이다.instruction register: memory로부터 fetch된 instruction을 저장하고 있는 register이다.

Arithmetic and Logic Unit, Shifter, and Control Unit

Arithmetic and Logic Unit

arithmetic and logical operation (연산) 이 실제 수행되는 장치이다.

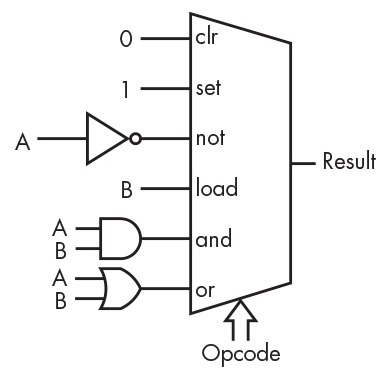

뭔가 신비해 보이지만 selector와 combinatorial logic circuit (gate)로 구성된다

- shift operation은 shift register로 data flow control은 control unit에서 이루어진다.

operation을 구성하는 micro-operation은 크게 register-transfer, arithmetic op, logical op, shift 등의 4가지로 나누어지는데 ALU는 이중 arithmetic operation과 logical operation을 담당한다고 볼 수 있다. (register에 저장된 data들에 대해 이루어지는 기본적인 operation들을 micro-operation이라고 함)

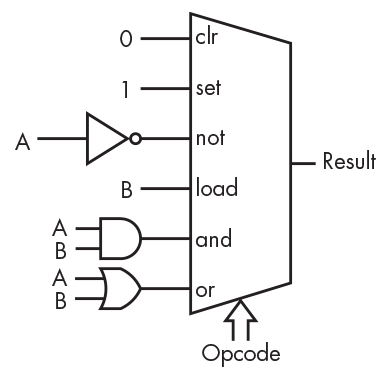

- Control unit에서 오는 control signal (opcode)에 따라 data를 가져와서 연산을 수행한다.

- Accumulator와

condition code register등에 연산결과와 status가 저장된다.

- 위 그림에서 status register가 바로 condition code register이다.

- ALU 제어 신호는 달리 말하면

opcode(operation code)로 연산의 종류를 의미한다. - 상단의 register 에서 들어오는 data를

operand(피연산자) 라고 부른다.

ALU's opcodes (Simple Version)

ALU가 수행하는 opcode들을 나타낸 표이다. (example)

| opcode | mnemonic | description |

|---|---|---|

| 0000 | clr | operand에 상관없이 result를 0으로 |

| 0001 | set | result를 1로 |

| 0010 | not | operand A의 각 bit에 not연산 |

| 0011 | neg | operand A의 two's complement -A를 result로 |

| 0100 | shl | Shift A left by the low 4 bits of B |

| 0101 | shr | Shift A right by the low 4 bits of B |

| 0110 | Unused | |

| 0111 | Unused | |

| 1000 | load | pass operand B to the result |

| 1001 and | bitwise A AND B | |

| 1010 | or | bitwise A OR B |

| 1011 | xor | bitwise A XOR B |

| 1100 | add | A + B |

| 1101 | sub | A - B |

| 1110 | cmp | Set condition codes based on B-A (compare) |

| 1111 | Unused |

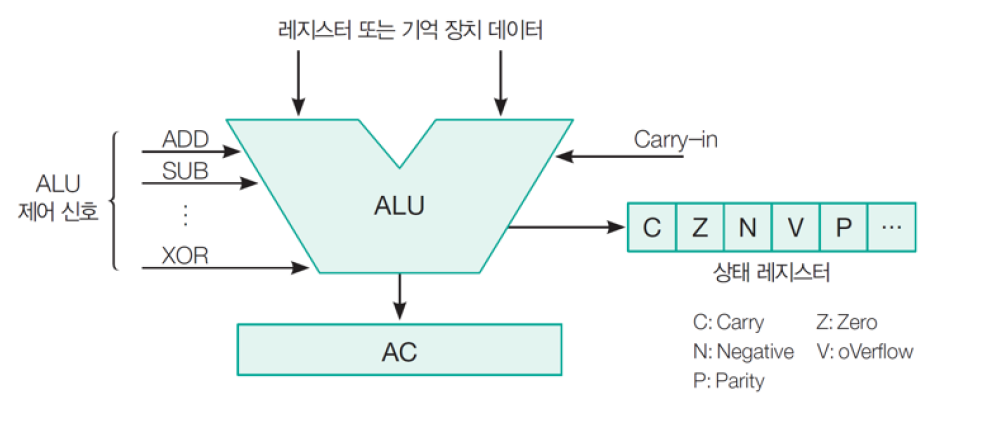

Shift Registers

shift연산을 담당한다.

Sequential Shift Register

flip-flop들로 구성한 shift register이다.

- 1bit를 shift하는데 1 clk가 필요 : 매우 느림.

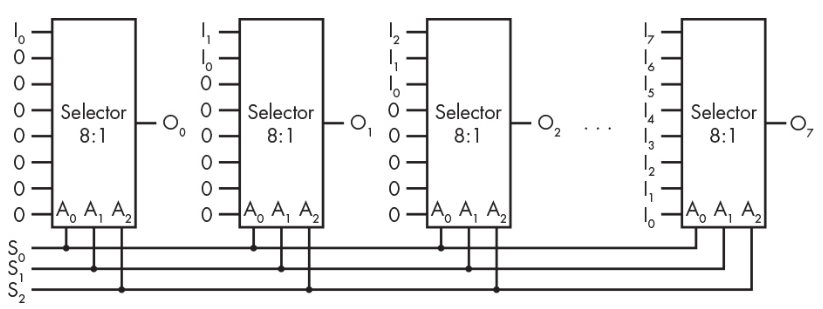

Barrel Shifter

selector(or MUX) 기반의 shift register이다.

shifter를 만드는데 들어가는 기본 구성요소 selector 등은 EDA에서 component로 제공된다. 즉, selector에 해당하는 chip들을 배선으로 연결하여 만드는 것이 아닌 "EDA에서 컴포넌트로 제공되는 블럭들을 조합하여 하나의 chip으로 설계" 하여 만드는게 일반적이다.

이는 마치 programming이 여러 function과 class들을 조합하는 것과 비슷하다.

Control Unit (or Execution Unit)

명령을 fetch하고 decode하며, 해당 명령을 수행하기 위한 여러 제어 신호를 보내는 소자로 실제적으로 ALU에게 필요한 연산과 데이터를 제공하고 결과값을 올바른 메모리 장소로 보내는 일들을 담당한다.

Instruction Sets

Instruction

컴퓨터가 수행해야할 명령을 나타내는 bit pattern이다. CPU에서 control unit이 이를 해석하여 이에 해당하는 제어신호를 보내게 된다.

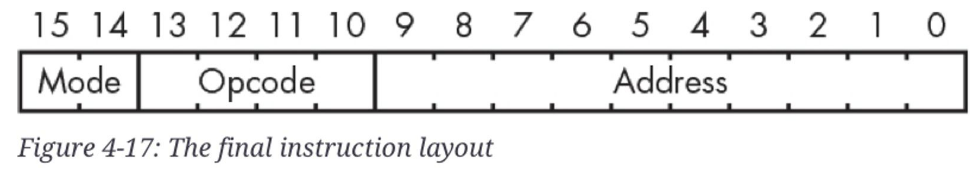

- 일반적으로 instruction은 mode, operation code (opcode), address로 구성된다. (Single-address instruction layout)

mode

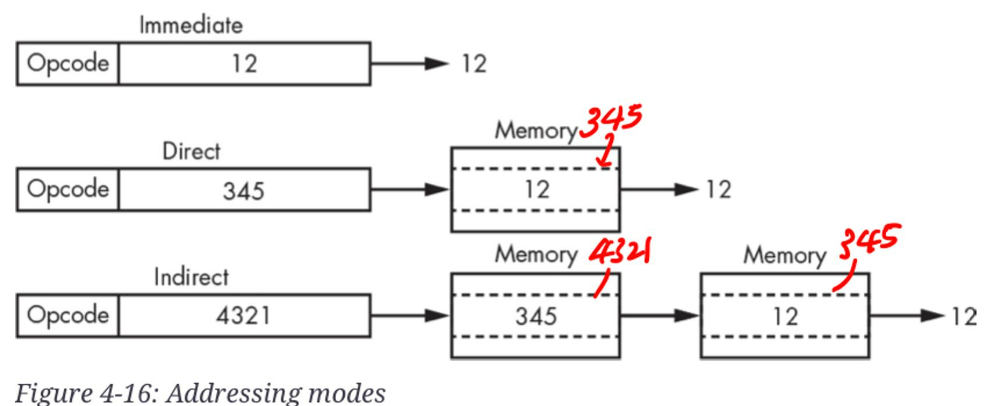

addressing mode를 가르킴. 간단히 말하면 3가지의 다른 addressing mode가 존재한다.

opcode

수행할 명령어를 나타내는 code이다.

address

현재 수행할 instruction과 관련된 data들이 놓인 memory location 혹은 data 그 자체, 또는 memory location이 놓여있는 memory location. (addressing mode에 따라 다름)

Single-address instruction layout은 ALU에서의 결과가 accumulator에 저장되고 해당 accumulator를 operand로 사용하는 형태이다.

- 한번에 하나의 memory location에 접근하면 되며 적은 크기의 instruction으로 수행가능하다는 장점을 가진다.

Addressing Mode (주소지정 모드)

여기서 다루는 addressing mode는 absolute addressing에 해당한다. 후에 다루는

relative addressing도 존재한다.

instruction에서 memory locatio을 가르키는 방법은 다음과 같은 3가지로 나뉜다.

immediate mode addressing

instruction에 address가 아닌 실제 값이 들어가 있는 경우이다.

작은 크기(bit)의 상수값을 이용하는 경우 사용되며 가장 속도가 빠른 방식이다.

direct addressing

instruction에 포함된 address가 reference하는 곳(memory location)에 instruction이 사용할 value(값)이 있다.

indirect addressing

instruction에 포함된 address가 가르키는 곳에 또 address가 들어 있다.

즉, instruction에 포함된 address가 reference하고 있는 memory location에 가서 값을 가져오는게 아니고, 해당 memory location의 값이 또 address이기 때문에 다시 해당 address가 reference하고 있는 memory location으로 가서 값을 가져온다.

instruction의 크기를 늘리지 않고도 보다 큰 용량의 memory로 확장할 수 있다.

단, 2번에 걸쳐 memory에 접근하므로 가장 느리다.

absolute addressing은 주소 0을 기준으로 address를 나타내지만,

relative addressing은 현재 주소를 기반으로 상대적인 값을 통해 address를 나타낸다.

Condition Code Instructions.

condition code register를 직접 다루는 instruction을 가르킨다.

cca instruction

- Condition Code register → Accumulator

- condition code register의 저장된 값을 accumulator로 copy

acc instruction

- Accumulator → Condition Code register

Branching (분기, 분기명령)

일반적으로 하나의 instruction이 수행되고 나면 PC register가 가르키고 있는 instruction을 수행하게 되고 해당 다음 instruction을 수행하기 전 PC는 하나가 증가하게 된다. 이 같은 경우, 메모리에 저장된 instruction들을 순서대로 수행하게 된다.

하지만 프로그램이 항상 순서대로만 수행되는 게 아닌 특정 조건에 따라 다른 순서로 수행해야 하는 경우도 있기 때문에 이를 위한 branching 명령어가 존재한다.

이들은 PC register의 값을 직접 변경하여 instruction들의 수행순서를 바꾸게 한다. 대표적인 Branch instruction의 종류와 이에 해당하는 조건은 다음과 같다.

| Code | Mnemonic | Description |

|---|---|---|

| 000 | bra | branch always. |

| 001 | bov | branch if the O (overflow) condition code bit is set. |

| 010 | beq | branch if the Z (zero) condition code bit is set. |

| 011 | bne | branch if the Z condition code bit is not set. |

| 100 | blt | branch if N (negative) is set and Z is clear. |

| 101 | ble | branch if N or Z is set. |

| 110 | bgt | branch if N is clear and Z is clear. |

| 111 | bge | branch if N is clear or Z is set. |

- condition code register의 해당하는 bit에 대한 조건을 만족하면 branching한다.

위에서 살펴본 것처럼 조건에 의해서 branching하지 않고 program counter register의 값을 명시적으로 그냥 바꾸는 등의 동작을 수행하는 instruction도 존재한다.

pca: 현재 program counter register의 값을 accumulator로 copyapc: 현재 accumulator의 값을 program counter register로 copy

Final Instruction Set

16bit 기준 single address instruction layout은 다음과 같다.

| Opcode | Direct (00) | Indirect (01) | Immediate (10) | None (11) |

|---|---|---|---|---|

| 0000 | load | load | load | |

| 0001 | and | and | and | set |

| 0010 | or | or | or | not |

| 0011 | xor | xor | xor | neg |

| 0100 | add | add | add | shl |

| 0101 | sub | sub | sub | shr |

| 0110 | cmp | cmp | cmp | acc |

| 0111 | store | store | cca | |

| 1000 | bra | bra | bra | apc |

| 1001 | bov | bov | bov | pca |

| 1010 | beq | beq | beq | |

| 1011 | bne | bne | bne | |

| 1100 | blt | blt | blt | |

| 1101 | ble | ble | ble | |

| 1110 | bgt | bgt | bgt | |

| 1111 | bge | bge | bge |

shl,shr는 operation에서 사용하지 않는 하위 4비트를 이용하여 얼마만큼 쉬프트할지를 지정한다.

우리가 만드는 program은 결국 위와 같은 instruction들의 list이다.

-

사람이 알기 쉬운 high level programming language로 프로그래밍을 하여 작성된 source code 는 위에 나열된 instruction들의 list로 변경된다.

-

해당 instruction의 list는 정해진 bit size의 bit-pattern들의 묶음이다.

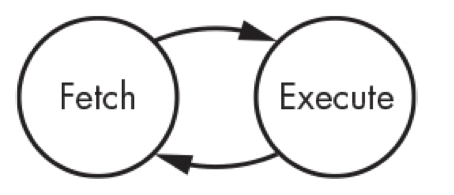

Fetch and Execute

instruction의 수행은 다음과 같은 fetch-execute cycle로 구성된다.

Fetch

memory에서 instruction을 register (정확히는 instruction register)로 가져오는 것을 의미한다.

-

stored program computer에서는 memory에 처리해야 하는 instruction들의 list가 저장되어 있다.

-

Program Counter register (← PC register)가 reference하고 있는

memory location(=다음에 수행되어야할 instruction이 저장된 memory location)에 있는 instruction을 instruction register로 가져오는 것을 fetch라고 한다.

- PC에 저장된 주소가 address bus를 통해 memory로 주어지고

- address bus를 통해 전달된 address에 해당하는 memory location에 저장된 값이

- data bus를 통해 instruction register로 저장된다.

- 이 값이 사실 insturction이다.

Execute

fetch된 instruction이 해당 instruction의 내용에 따라 memory에서 값을 읽어오는 등의 여러 작업이 이루어지며 이에 따라 해당 instruction이 수행된다. 이 단계를 Execution cycle이라고 부른다.

이같이 fetch된 insturction을 수행하기 위해 memory에 접근하는 등의 작업을 하는 동안 instruction이 저장되어 있는 공간이 바로 instruction register이다.

하나의 instruction을 수행하기 위한 fetching-execution cycle은 여러 단계가 필요하기 때문에 현재 단계가 무엇인지를 나타내는 counter가 필요하다.

Control Unit(or Execution Unit)은

- 해당 counter, opcode 그리고 mode들에 할당된 bit를 읽어들여

- 현재 필요한 제어 signal을 필요한 component들에게 전달한다.

이같은 signal들의 흐름을 제어하는 것을 signal traffic control이라고 부른다.

Control Unit에서의 traffic control은 random logic을 통해 이루어지거나 memory를 기반으로 하는 microcode로 구현된다. 결국 control unit은 여러 state를 가지는 일종의 state-machine이며 이 때문에 memory기반의 state machine으로 구현가능하다.

Traffic Control

- Random logic기반의 traffic control은 RISC에서 보다 많이 이용된다.

- Microcode 기반의 traffic control (Micro-ROM방식이라고도 불림)은 CISC에서 보다 많이 이용된다.

reference

mkdocs