▶️ 혼공학습단 ▶️ 도서 정보 ▶️ 심화자료 ▶️ 유튜브 강의

기본 미션

p. 125 확인 문제 2번

플래그 레지스터연산 결과 혹은 CPU 상태에 대한 부가 정보를 저장하는 레지스터A status register, flag register, or condition code register (CCR) is a collection of status flag bits for a processor.

The status register is a hardware register that contains information about the state of the processor. Individual bits are implicitly or explicitly read and/or written by the machine code instructions executing on the processor. The status register lets an instruction take action contingent on the outcome of a previous instruction.

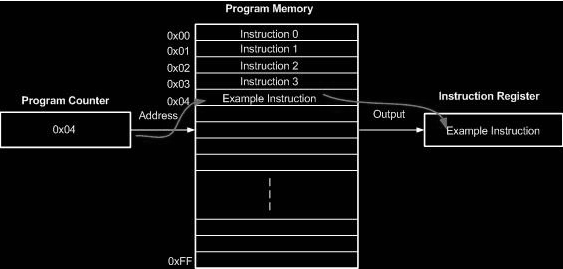

프로그램 카운터메모리에서 가져올 명령어의 주소를 저장하는 레지스터The program counter (PC) is a processor register that indicates where a computer is in its program sequence.

Usually, the PC is incremented after fetching an instruction, and holds the memory address of ("points to") the next instruction that would be executed.

범용 레지스터데이터와 주소를 모두 저장할 수 있는 레지스터General-purpose registers (GPRs) can store both data and addresses, i.e., they are combined data/address registers; in some architectures, the register file is unified so that the GPRs can store floating-point numbers as well.

명령어 레지스터해석할 명령어를 저장하는 레지스터In computing, the instruction register (IR) or current instruction register (CIR) is the part of a CPU's control unit that holds the instruction currently being executed or decoded.

p. 155 확인 문제 4번

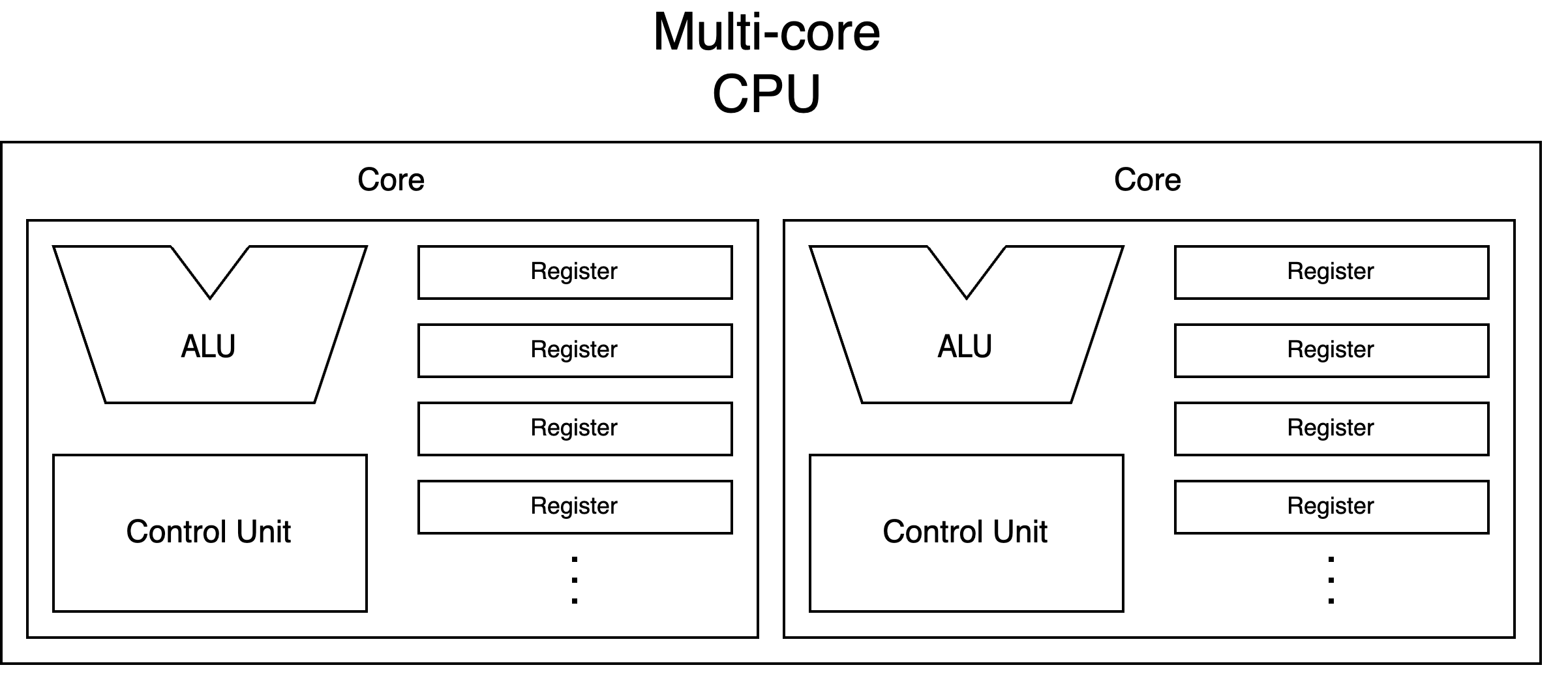

멀티코어 CPU 코어가 두 개 이상 있는 CPU

코어 CPU 내에서 명령어를 처리하는 부품

A multi-core processor is a microprocessor on a single integrated circuit with two or more separate processing units, called cores (for example, dual-core or quad-core), each of which reads and executes program instructions.

ㄴ> draw.io Online diagram software

선택 미션

코어/멀티코어

A processor core is a processing unit that reads instructions to perform specific actions. Instructions are chained together so that, when run in real-time, they make up your computer experience. Literally, everything you do on your computer has to be processed by your processor.

Multiprocessing is the use of two or more central processing units (CPUs) within a single computer system. The term also refers to the ability of a system to support more than one processor or the ability to allocate tasks between them.

A multi-core processor is an integrated circuit (IC) to which two or more processors have been attached for enhanced performance, reduced power consumption, and more efficient simultaneous processing of multiple tasks.

스레드/멀티스레드

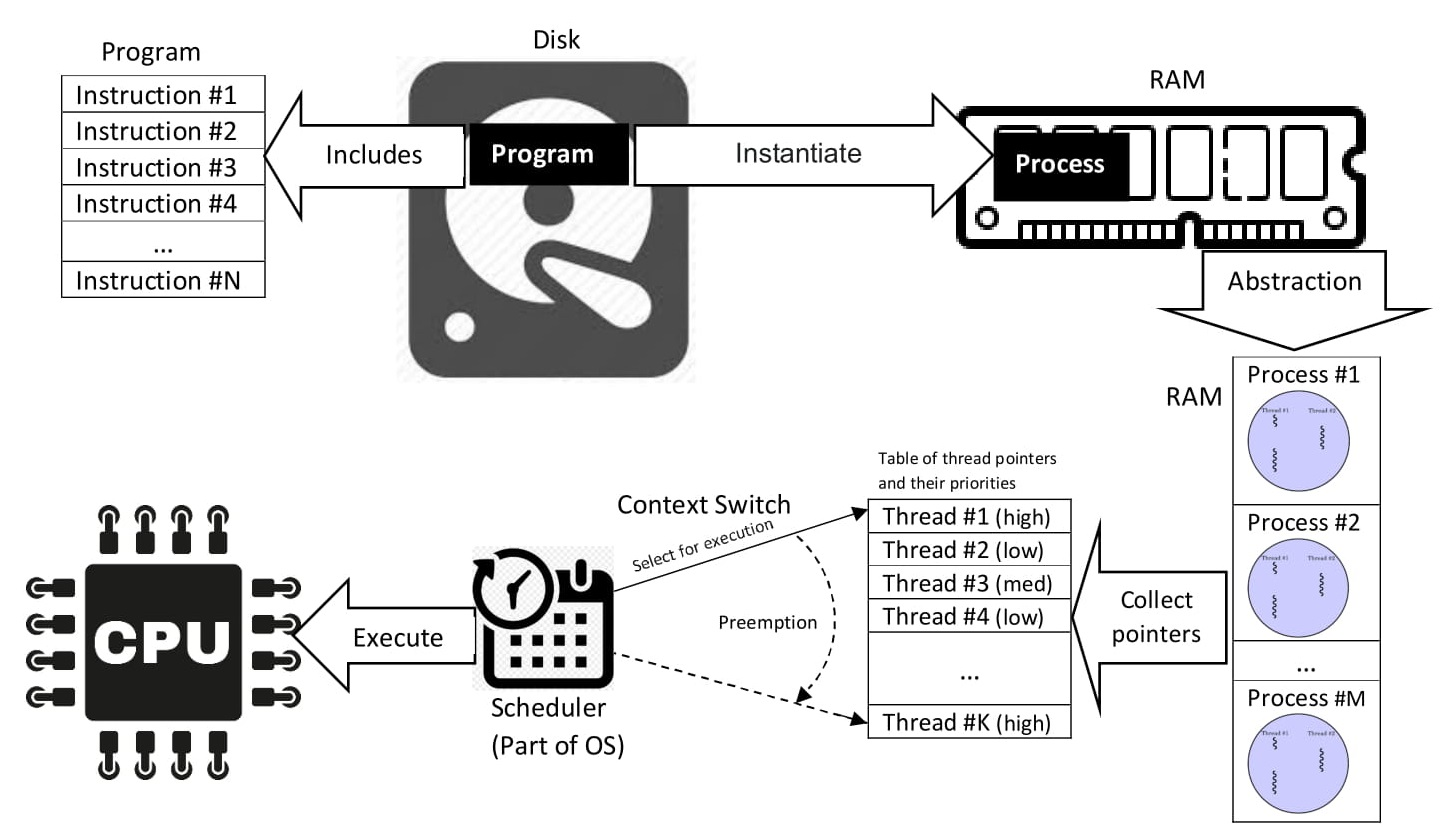

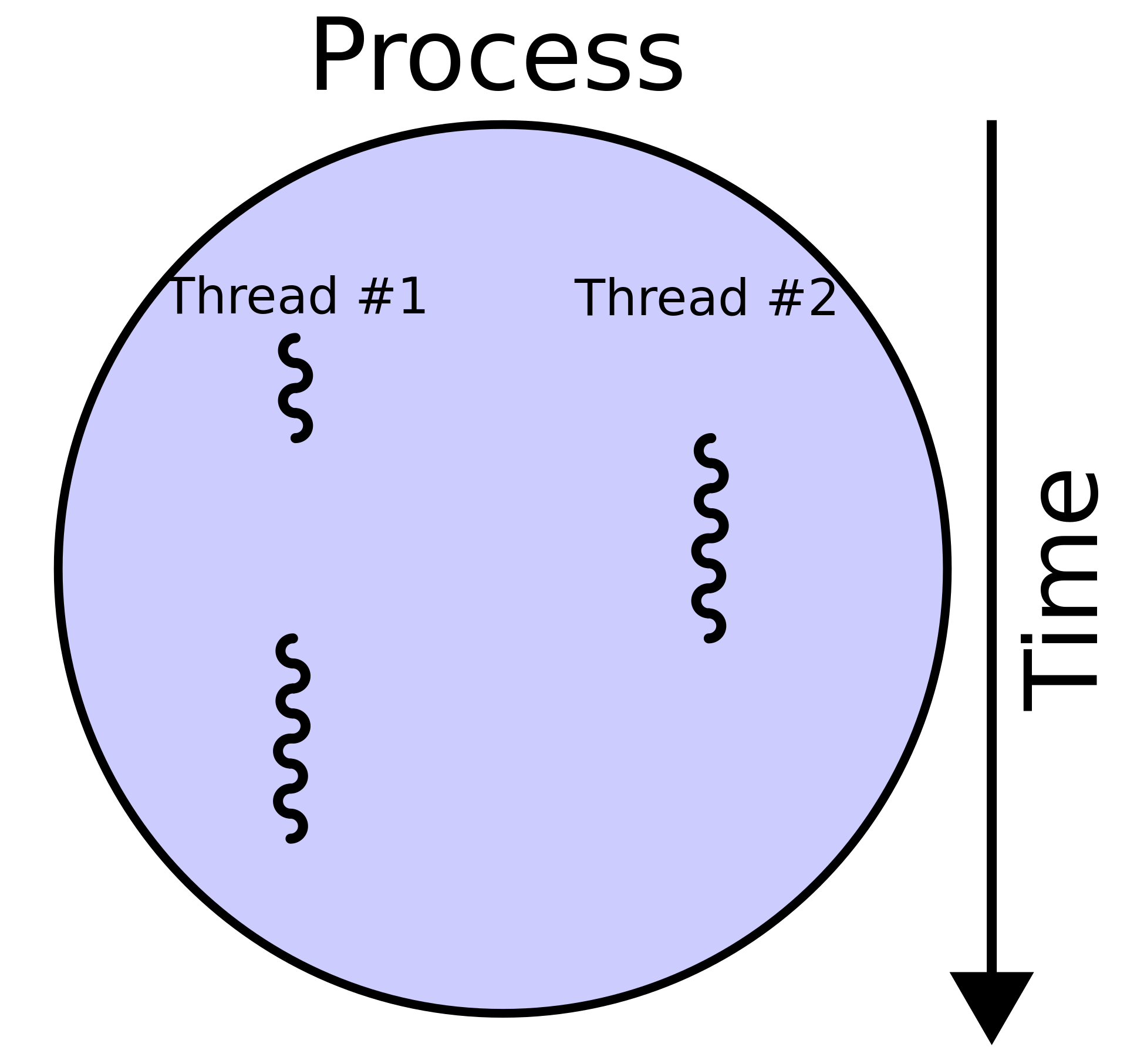

In computer science, a thread of execution is the smallest sequence of programmed instructions that can be managed independently by a scheduler, which is typically a part of the operating system.

In computer architecture, multithreading is the ability of a central processing unit (CPU) (or a single core in a multi-core processor) to provide multiple threads of execution concurrently, supported by the operating system.

This approach differs from multiprocessing. In a multithreaded application, the threads share the resources of a single or multiple cores, which include the computing units, the CPU caches, and the translation lookaside buffer (TLB).

[Chapter 04 ~ 05] 용어 정리

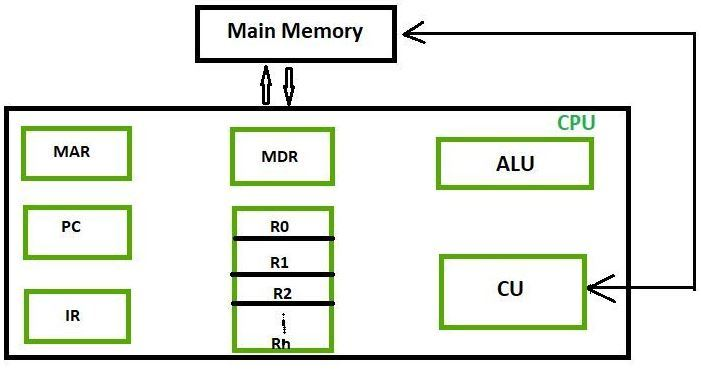

CPU

Central Processing Unit

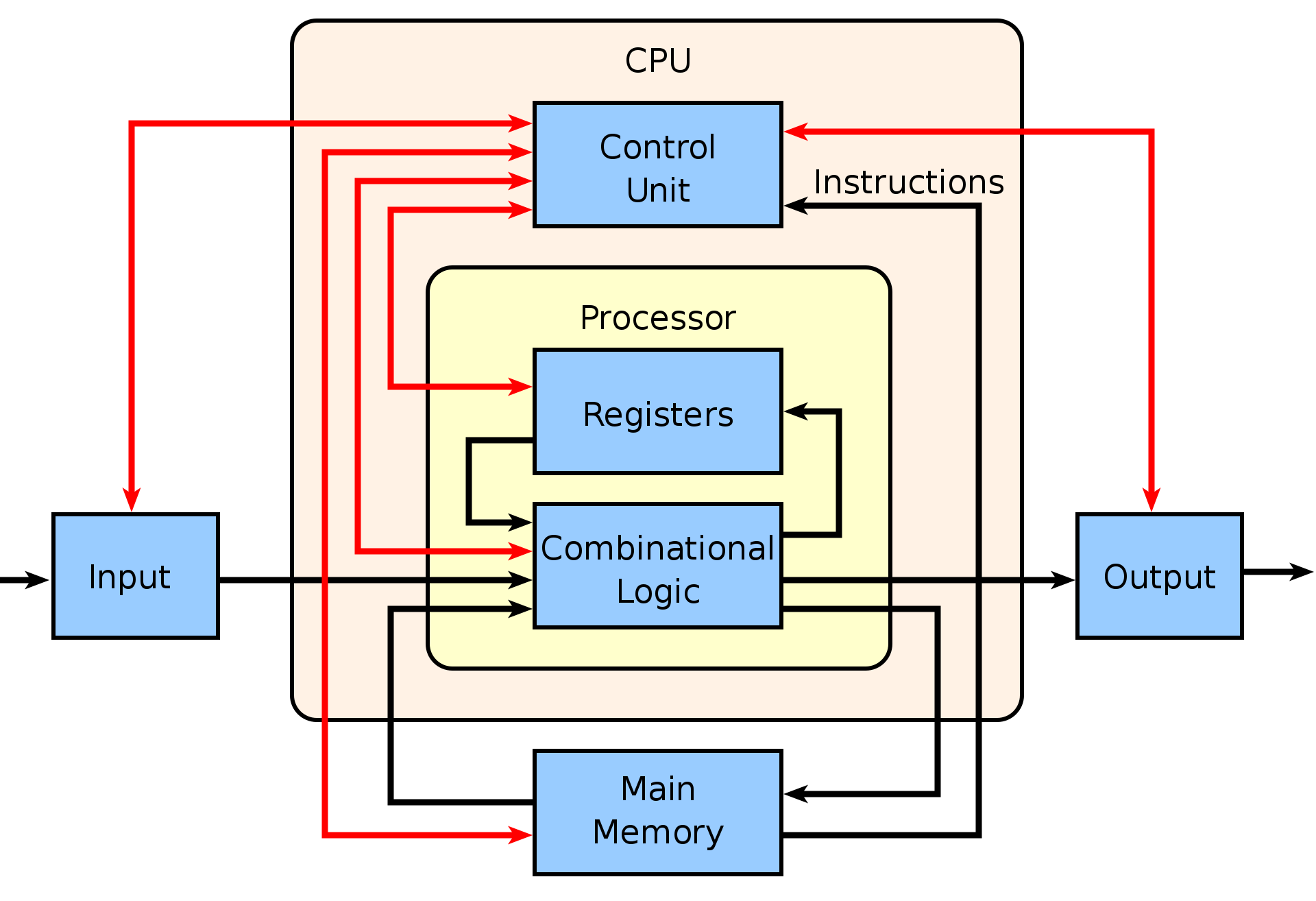

A central processing unit (CPU)—also called a central processor or main processor—is the most important processor in a given computer. Its electronic circuitry executes instructions of a computer program, such as arithmetic, logic, controlling, and input/output (I/O) operations. This role contrasts with that of external components, such as main memory and I/O circuitry, and specialized coprocessors such as graphics processing units (GPUs).

CPU - Central Processing Unit - inevitably referred to as the "brains" of the computers. The CPU does the active "running" of code, manipulating data, while the other components have a more passive role, such as storing data. When we say that a computer can "add two numbers, a billion times a second" .. that's the CPU. When you hit the Run button, the CPU ultimately "runs" your code.

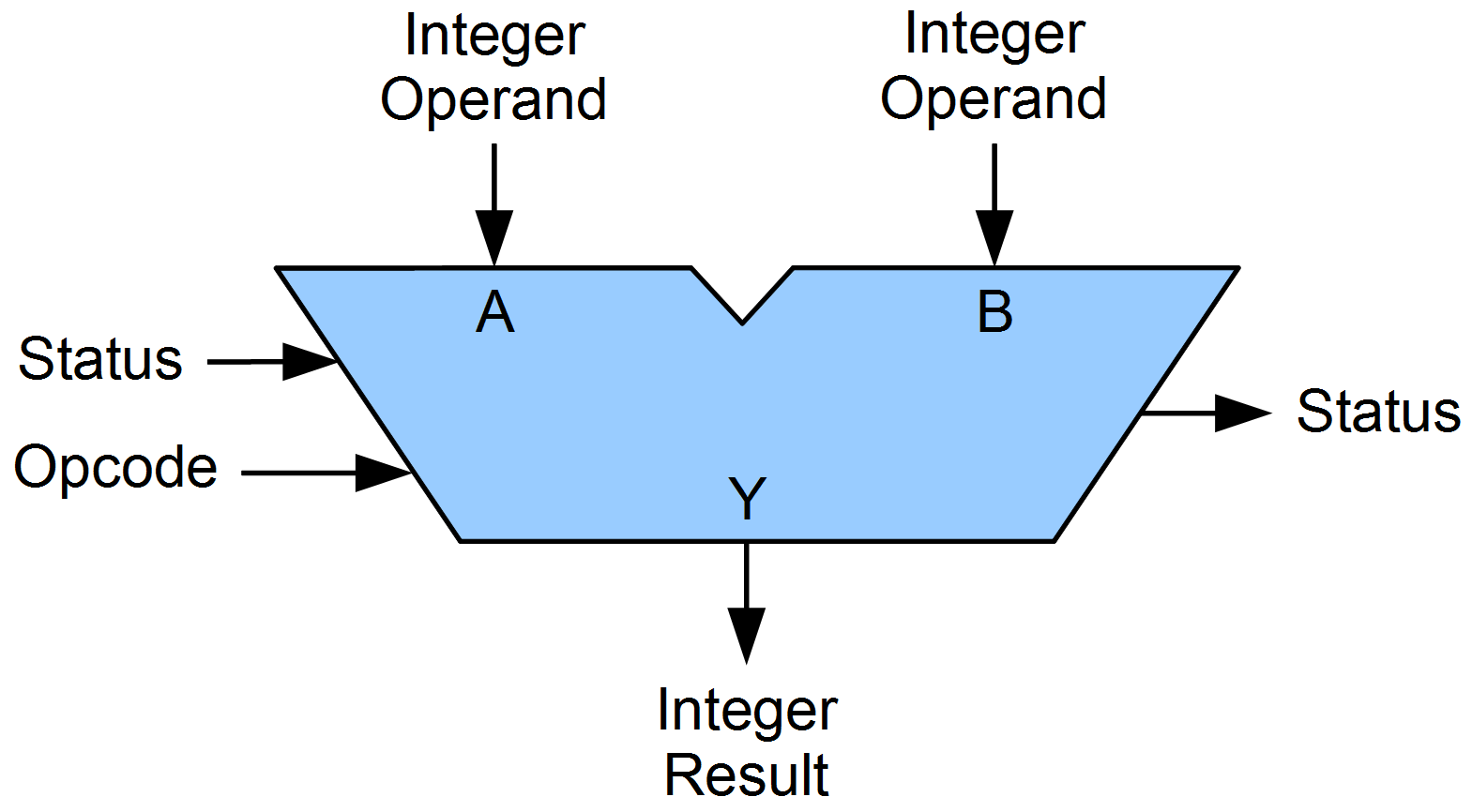

ALU

In computing, an arithmetic logic unit (ALU) is a combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers.

This is in contrast to a floating-point unit (FPU), which operates on floating point numbers. It is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units (GPUs).

Overflow

Status register

A status register, flag register, or condition code register (CCR) is a collection of status flag bits for a processor.

The status register is a hardware register that contains information about the state of the processor.

Individual bits are implicitly or explicitly read and/or written by the machine code instructions executing on the processor. The status register lets an instruction take action contingent on the outcome of a previous instruction.

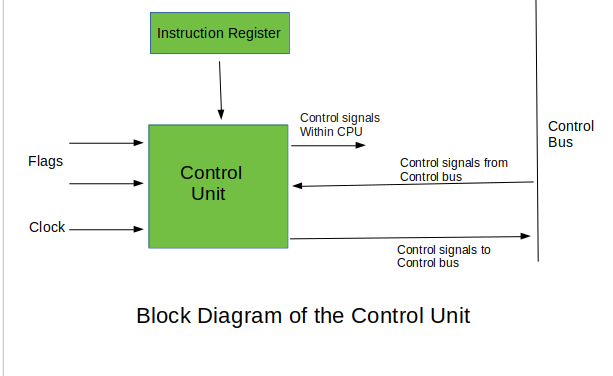

Control unit (제어장치)

The control unit (CU) is a component of a computer's central processing unit (CPU) that directs the operation of the processor.

A CU typically uses a binary decoder to convert coded instructions into timing and control signals that direct the operation of the other units (memory, arithmetic logic unit and input and output devices, etc.).

Most computer resources are managed by the CU. It directs the flow of data between the CPU and the other devices. John von Neumann included the control unit as part of the Von Neumann architecture.

In modern computer designs, the control unit is typically an internal part of the CPU with its overall role and operation unchanged since its introduction.

Clock

What is clock speed?

Clock speed is the number of times a second that a circuit operates and is most associated with the central processing unit (CPU). It is measured in hertz, or cycles per second. The higher the clock speed, the more processing power -- all other things being equal. Clock speed is also known as clock rate, core clock or clock frequency.

Registers

A processor register is a quickly accessible location available to a computer's processor. Registers usually consist of a small amount of fast storage, although some registers have specific hardware functions, and may be read-only or write-only.

Program Counter (PC)

There is a register in a PC (program counter) processor that contains the address of the next instruction to be executed from memory.

It is a 16 bit register and is also called instruction counter, instruction pointer, and instruction address register (IAR).

Instruction Register (IR, 명령어 레지스터)

In the context of computer hardware, an instruction register is an element in the central processing unit (CPU) of a computer or other device that holds programming instructions that will be executed at the beginning of the next clock cycle as instructed by other parts.

Memory Address Register (MAR, 메모리 주소 레지스터)

It holds the address of the location to be accessed from memory.

MAR and MDR (Memory Data Register) together facilitate the communication of the CPU and the main memory.

Memory Buffer Register (MBR, 메모리 버퍼 레지스터)

Memory Data Registers (MDR) = Memory Buffer Register (MBR)

It contains data to be written into or to be read out from the addressed location.

- General Purpose Registers (범용 레지스터)

A register serves as a quick memory for accepting, storing, and sending data and instructions that the CPU will need right away.

Flag register

The FLAGS register is the status register that contains the current state of an x86 CPU. The size and meanings of the flag bits are architecture dependent. It usually reflects the result of arithmetic operations as well as information about restrictions placed on the CPU operation at the current time.

Stack pointer

As a core component of the stack data structure, the stack pointer serves as a reference point that determines the top of the stack’s current position in memory.

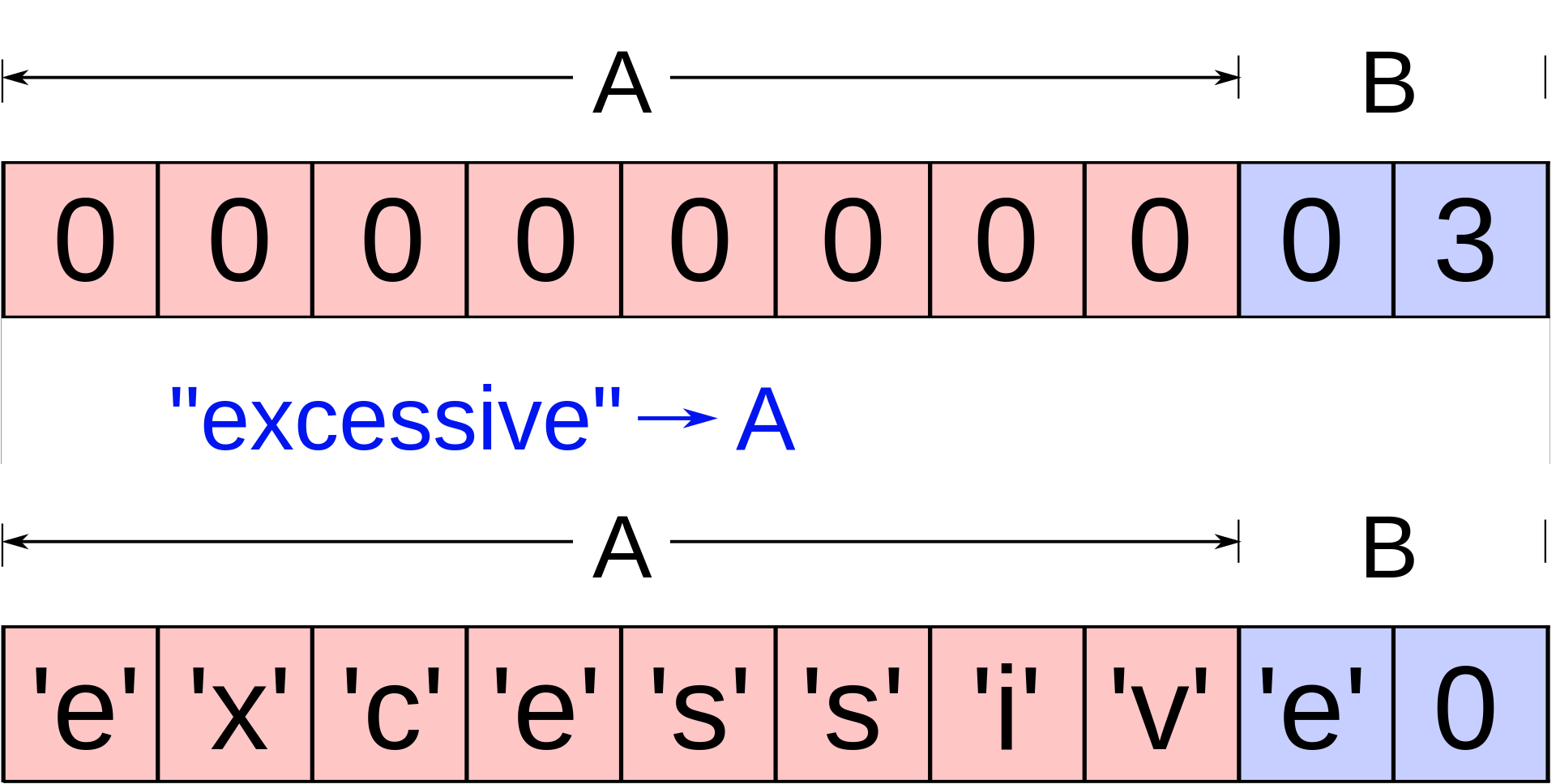

Stack addressing mode (스택 주소 지정 방식)

Stack addressing mode uses the top of the stack implicitly for the location of the operand.

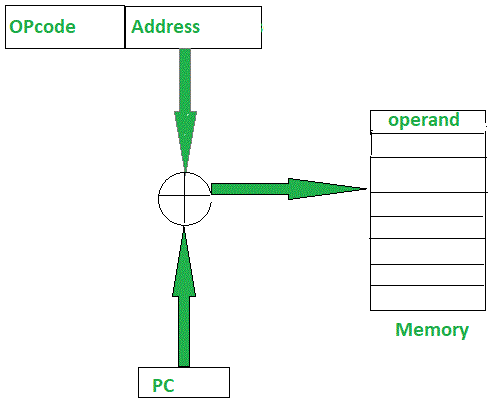

Displacement addressing mode (변위 주소 지정 방식)

Displacement addressing mode provides an address and a displacement value which, when added together gives the address of the operand.

Relative addressing mode (상대 주소 지정 방식)

The PC-relative addressing mode can be used to load a register with a value stored in program memory a short distance away from the current instruction. It can be seen as a special case of the "base plus offset" addressing mode, one that selects the program counter (PC) as the "base register".

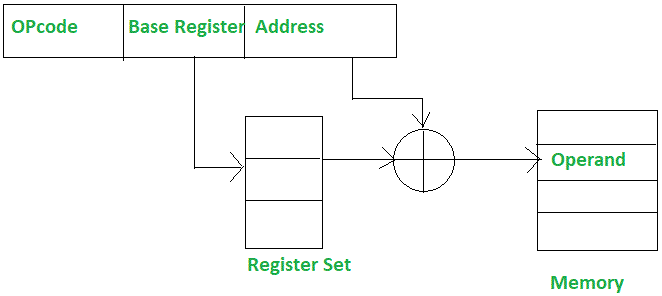

Base-register addressing mode (베이스 레지스터 주소 지정 방식)

Base register addressing mode is used to implement inter segment transfer of control. In this mode effective address is obtained by adding base register value to address field value.

Instruction cycle

The instruction cycle (also known as the fetch–decode–execute cycle, or simply the fetch-execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process instructions. It is composed of three main stages: the fetch stage, the decode stage, and the execute stage.

Fetch cycle (인출 사이클)Fetch stage: The next instruction is fetched from the memory address that is currently stored in the program counter and stored into the instruction register. At the end of the fetch operation, the PC points to the next instruction that will be read at the next cycle.

Indirect cyle (간접 사이클)In the case of a memory instruction (direct or indirect), the execution phase will be during the next clock pulse. If the instruction has an indirect address, the effective address is read from main memory, and any required data is fetched from main memory to be processed and then placed into data registers. If the instruction is direct, nothing is done during this clock pulse.

Execution cycle (실행 사이클)Execute stage: The control unit of the CPU passes the decoded information as a sequence of control signals to the relevant functional units of the CPU to perform the actions required by the instruction, such as reading values from registers, passing them to the ALU to perform mathematical or logic functions on them, and writing the result back to a register. If the ALU is involved, it sends a condition signal back to the CU. The result generated by the operation is stored in the main memory or sent to an output device. Based on the feedback from the ALU, the PC may be updated to a different address from which the next instruction will be fetched.

Repeat cycleIn addition, on most processors interrupts can occur. This will cause the CPU to jump to an interrupt service routine, execute that and then return. In some cases an instruction can be interrupted in the middle, the instruction will have no effect, but will be re-executed after return from the interrupt.

Interrupt

In digital computers, an interrupt (sometimes referred to as a trap) is a request for the processor to interrupt currently executing code (when permitted), so that the event can be processed in a timely manner. If the request is accepted, the processor will suspend its current activities, save its state, and execute a function called an interrupt handler (or an interrupt service routine, ISR) to deal with the event.

| Synchronous interrupt (동기 인터럽트) | Asynchronous interrupt (비동기 인터럽트) |

|---|---|

| Exception (예외) | Hardware interrupts (하드웨어 인터럽트) |

| A software interrupt is requested by the processor itself upon executing particular instructions or when certain conditions are met. | A hardware interrupt is a condition related to the state of the hardware that may be signaled by an external hardware device. |

Hardware interrupts

| Maskable interrupts | Non-maskable interrupts (NMIs) |

|---|---|

| Signals which are affected by the mask are called maskable interrupts. | Some interrupt signals are not affected by the interrupt mask and therefore cannot be disabled. |

Interrupt handler

In computer systems programming, an interrupt handler, also known as an interrupt service routine or ISR, is a special block of code associated with a specific interrupt condition. Interrupt handlers are initiated by hardware interrupts, software interrupt instructions, or software exceptions, and are used for implementing device drivers or transitions between protected modes of operation, such as system calls.

Clock

A circuit in a processor that generates a regular sequence of electronic pulses used to synchronise operations of the processor's components. The time between pulses is the cycle time and the number of pulses per second is the clock rate (or frequency).

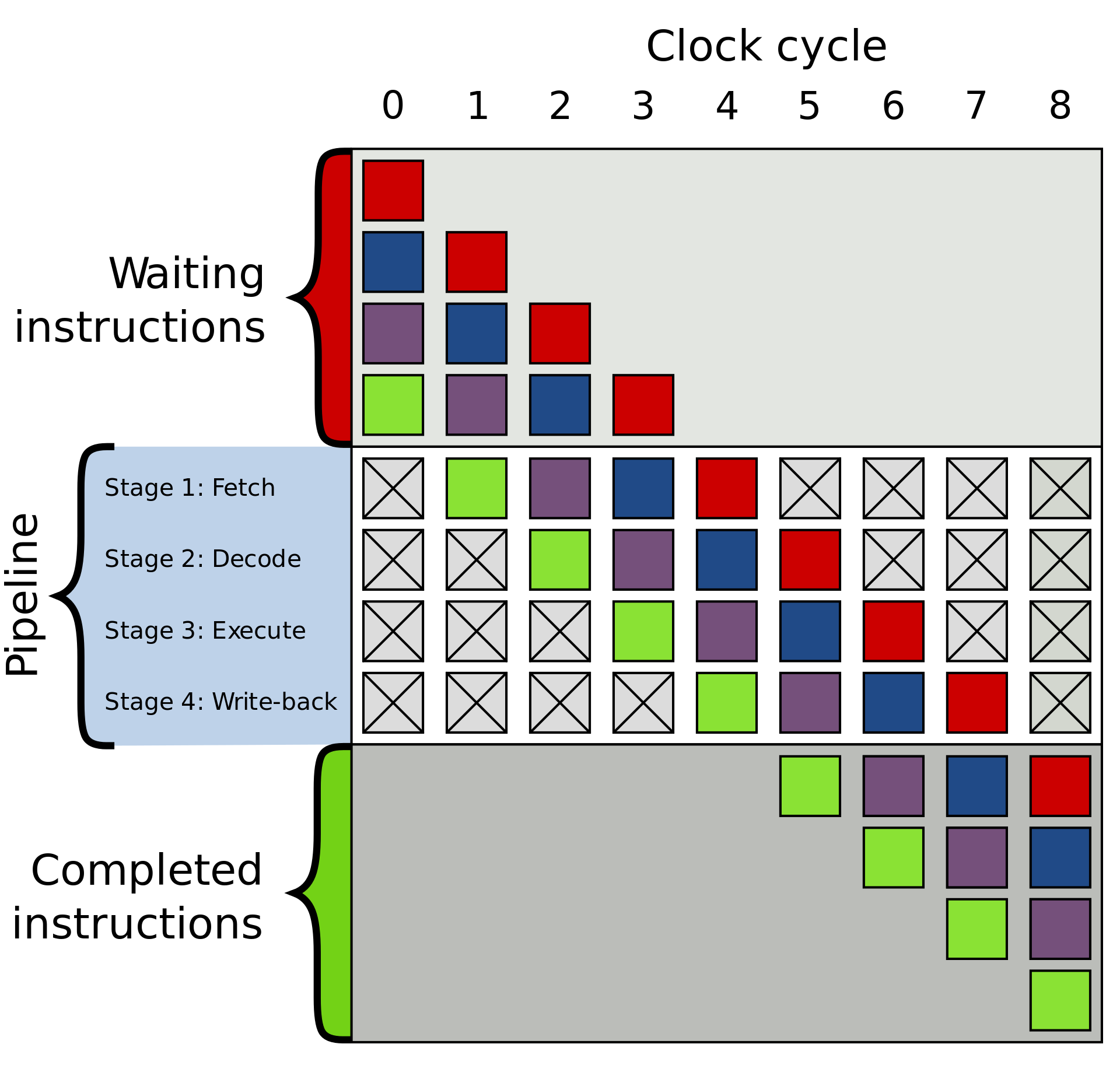

Pipelining

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow in the instruction pipeline.

OoOE

In computer engineering, out-of-order execution (or more formally dynamic execution) is a paradigm used in high-performance central processing units to make use of instruction cycles that would otherwise be wasted.

In this paradigm, a processor executes instructions in an order governed by the availability of input data and execution units, rather than by their original order in a program.

In doing so, the processor can avoid being idle while waiting for the preceding instruction to complete and can, in the meantime, process the next instructions that are able to run immediately and independently.

ISA

In computer science, an instruction set architecture (ISA) is an abstract model of a computer. A device that executes instructions described by that ISA, such as a central processing unit (CPU), is called an implementation.

CISC vs RISC

The primary goal of

CISCarchitecture is to complete a task in as few lines of assembly as possible. This is achieved by building processor hardware that is capable of understanding and executing a series of operations.

RISCprocessors only use simple instructions that can be executed within one clock cycle.

The Overall RISC Advantage

Today, the Intel x86 is arguable the only chip which retains CISC architecture. This is primarily due to advancements in other areas of computer technology. The price of RAM has decreased dramatically. In 1977, 1MB of DRAM cost about $5,000. By 1994, the same amount of memory cost only $6 (when adjusted for inflation). Compiler technology has also become more sophisticated, so that the RISC use of RAM and emphasis on software has become ideal.

혼공컴운

| # | 진도 | 기본 미션 | 선택 미션 | ☑️ |

|---|---|---|---|---|

| 1주차 (1/2 ~ 1/7) | Chapter 01 ~ 03 | p. 51의 확인 문제 3번, p. 65의 확인 문제 3번 풀고 인증하기 | p. 100의 스택과 큐의 개념을 정리하기 | ☑️ |

| 2주차 (1/8 ~ 1/14) | Chapter 04 ~ 05 | p. 125의 확인 문제 2번, p. 155의 확인 문제 4번 풀고 인증하기 | Ch.05(05-1) 코어와 스레드, 멀티 코어와 멀티 스레드의 개념을 정리하기 | ☑️ |

| 3주차 (1/15 ~ 1/21) | Chapter 06 ~ 08 | p. 185의 확인 문제 3번, p. 205의 확인 문제 1번 풀고 인증하기 | Ch.07(07-1) RAID의 정의와 종류를 간단히 정리해 보기 | |

| 4주차 (1/22 ~ 1/28) | Chapter 09 ~ 11 | p. 304의 확인 문제 1번 풀고 인증하기 | Ch.11(11-2) 준비 큐에 A,B,C,D 순으로 삽입되었다고 가정했을 때, 선입 선처리 스케줄링 알고리즘을 적용하면 어떤 프로세스 순서대로 CPU를 할당받는지 풀어보기 | |

| 5주차 (1/29 ~ 2/4) | Chapter 12 ~ 13 | p. 363의 확인 문제 1번 풀고 인증하기 | Ch.12(12-1) 임계 구역, 상호 배제 개념을 정리하기 | |

| 6주차 (2/5 ~ 2/12) | Chapter 14 ~ 15 | p. 400의 확인 문제 1번 풀고 인증하기 | Ch.14(14-3) 프로세스가 사용할 수 있는 프레임이 3개 있고, 페이지 참조열이 '2313523423' 일 때 LRU 페이지 교체 알고리즘으로 이 페이지를 참조한다면 몇 번의 페이지 폴트가 발생하는지 풀어보기 |