컴퓨터 시스템의 일반적인 구조

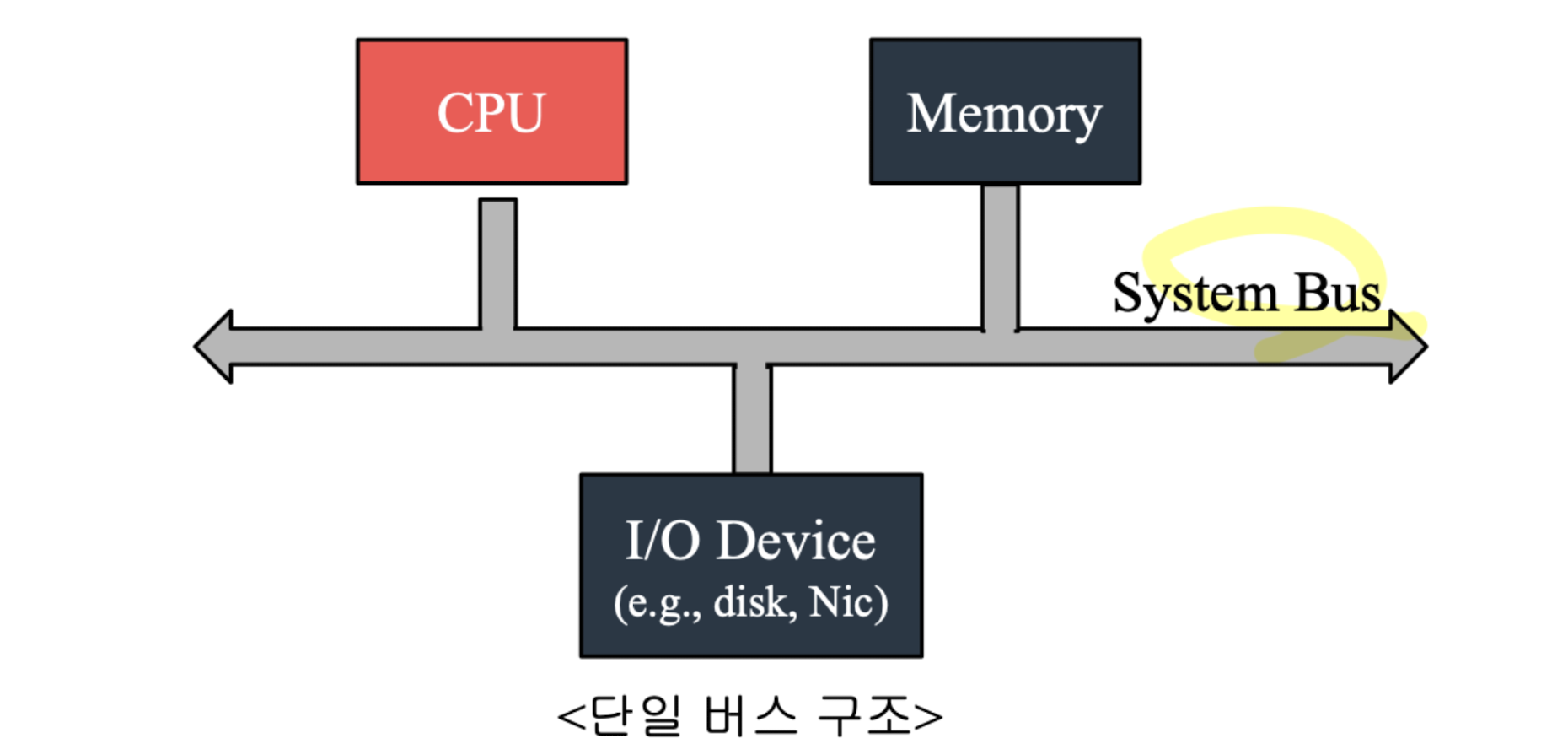

단일 Bus 구조

Bus

- CPU, RAM, I/O 장치 간 데이터가 전송되는 경로

- Data 버스, Address 버스

단일 Bus

- 하나의 시스템 버스에 여러가지 모듈이 연결

- CPU, Memory, I/O의 속도가 비슷했던 초창기에 발생

- CPU, Memory, I/O의 속도 격차 증가 -> 병목 현상 발생

Bottleneck

-

같은 버스에 연결된 디바이스들 사이의 속도 차이로 인해 발생

-

CPU > Memory >>> I/O 순으로 속도의 격차가 발생

-

빠른 디바이스가 처리하는 양 만큼을 느린 디바이스가 처리하지 못함

-> 전체 시스템 속도는 느린 디바이스의 속도로 제한 됨 -

E.g., CPU는 초당 5단위의 일을 처리할 수 있는데, 메모리가 초당 3단위의 일만을 전달해 줄 수 있다고 할 때, 전제 시스템 속도는 메모리의 속도로 제한된다.

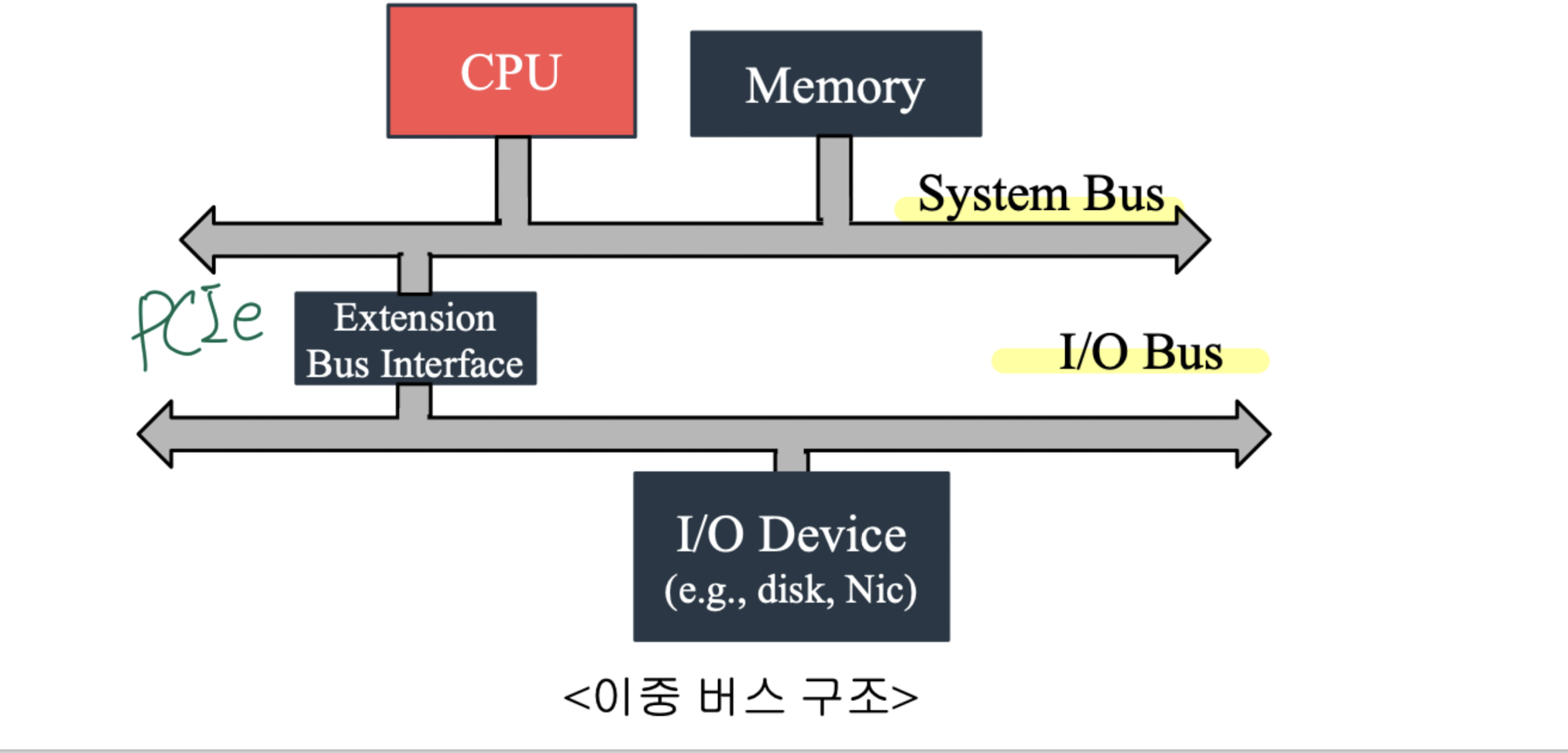

계층적 Bus 구조

세분화된 버스 채용

- CPU Local Bus, Memory Bus, PCI Bus, etc.

이중 버스

- CPU와 I/O 속도 격차로 인한 병목 현상 해결하고자 함

- 빠른 CPU와 메모리는 시스템 버스에 연결

- I/O 장치는 I/O 버스에 연결

I/O Device Basic Concepts

Event Handling Mechanisms

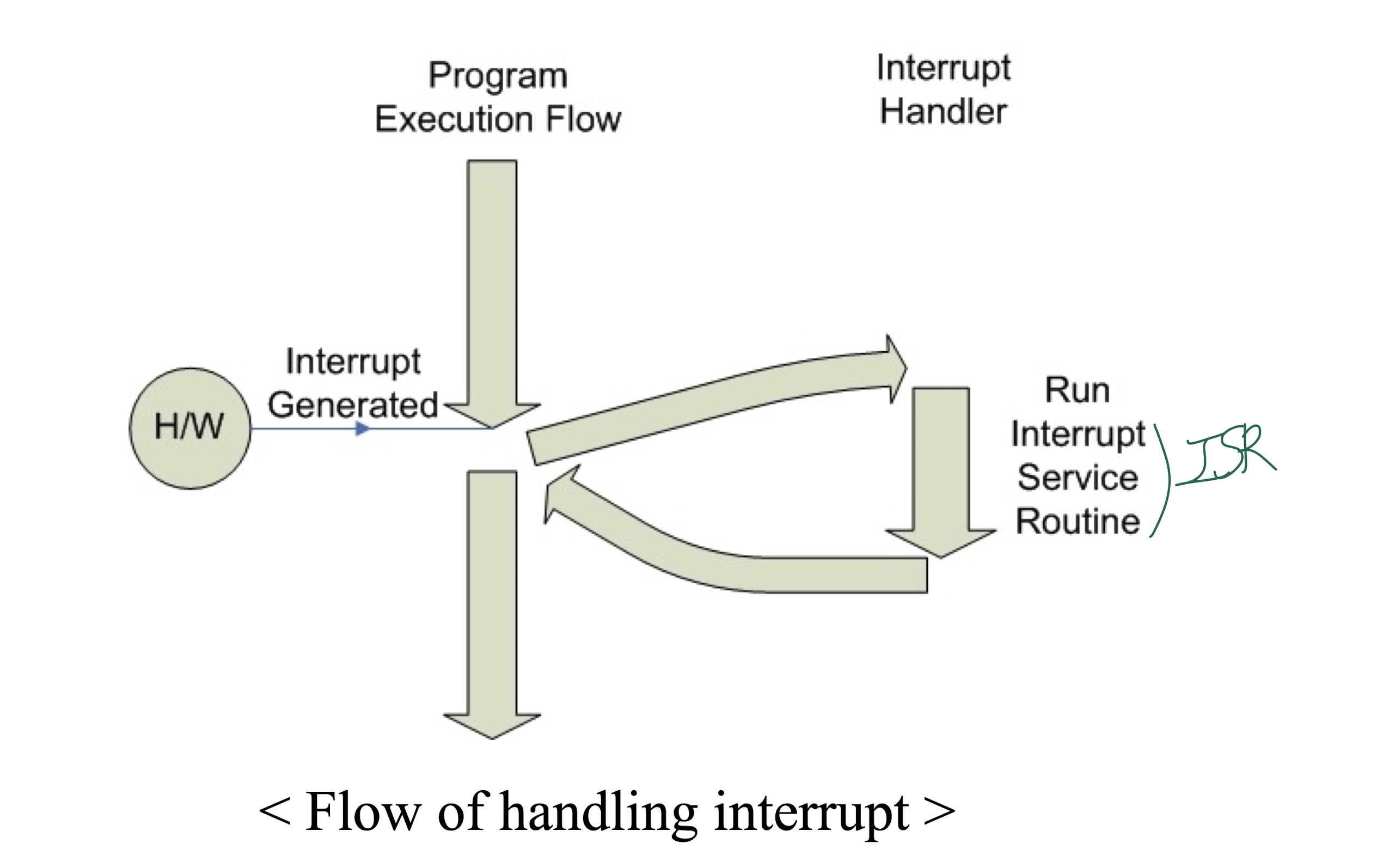

Interrupt

비동기적 이벤트를 처리하기 위한 기법

- E.g., 네트워크 패킷 도착 이벤트, I/O 요청

참고

비동기적이란, 프로그램 내에서 예측 불가함을 의미한다.

Interrupt 처리 순서

- Interrupt Disable

- 현재 실행 상태 (State)를 저장

- ISR(Interrupt Service Routine)로 점프

- 저장한 실행 상태 (State)를 복원

- 인터럽트로 중단된 지점부터 다시 시작

Interrupt에는 우선 순위가 있으며, H/W 장치마다 다르게 설정됨

Note

- ISR은 짧아야 함 (너무 길면 다른 Interrupt 들이 처리되지 못함)

- Time Sharing은 Timer Interrupt의 도움으로 가능하게 된 기술임

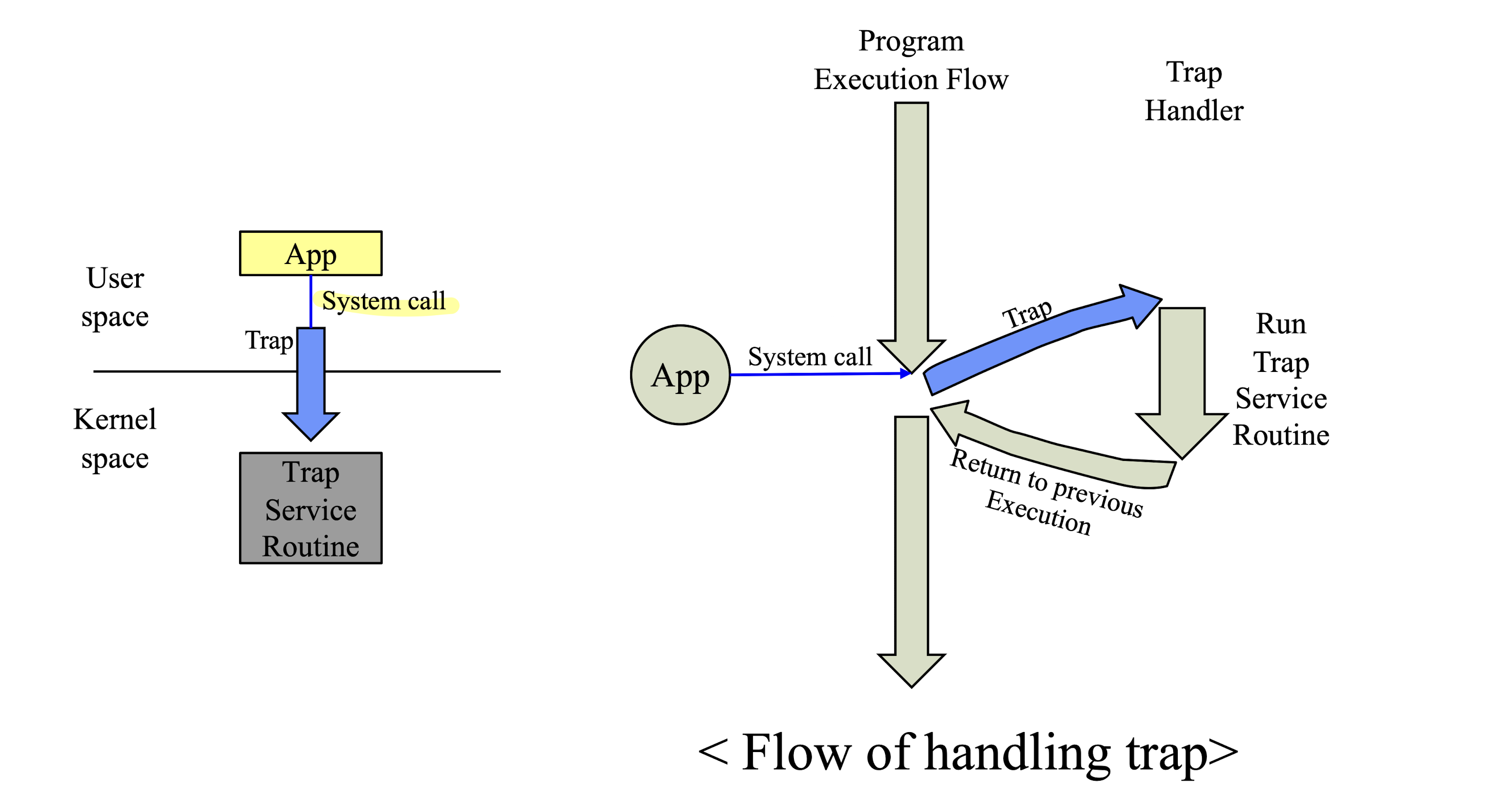

Trap

동기적 이벤트를 처리하기 위한 기법

-

E.g., Divide by Zero와 같은 프로그램 에러에 의해 발생

-

Trap handler에 의해 처리

-

Trap Service Routine이 있기 때문에 Interrupt와 유사하지만,

Interrupt와 달리 실행 상태(state)를 저장/복원 하지 않음

Intel x86

Interrupt

- Hardware Interrupt

- Generated externally by the chipset, and it is signaled by latching onto the #INTP pin of the CPU

- Software Interrupt

- Signaled by software running on a CPU to indicate that it needs the kernel's attention (e.g., System call)

Exception (Trap)

- Occurred when the processor detects an error condition while executing an instruction

- Type of exceptions

- Fault

- Trap

- Abort

XV6 - Interrupt & Exception

-

Hardware Interrupt

- Handled by interrupt vectors defined in vector.S

IRQ_TIMER, IRQ_KBD, IRQ_IDE

- Handled by interrupt vectors defined in vector.S

-

Software Interrupt

- When a user calls a system call, it triggers a software interrupt (T_SYSCALL)

-

Both interrupts are handled by using trap mechanism in XV6

I/O 처리 기법

Device Registers

- 보통 하드웨어 장치는 4종류의 Register를 가짐

- Control Register, Status Register, Input Register Output Register

- Register들은 메인 메모리의 일부 영역에 Mapping

- Mapping된 영역의 주소만 알면, CPU에서 접근 가능

I/O Controller

- High-Level의 I/O 요청을 Low-level Machine Specific Instruction으로 해석하는 회로

- 장치와 직접 상호작용

Polling

Loop 안에서 특정 이벤트의 도착 여부를 확인하면서 기다리는 방법

Interrupt Handler를 등록하는 방식과 반대되는 개념

Controller나 장치가 매우 빠른 경우, Polling은 Event 처리 기법으로 적당함

이벤트 도착 시간이 길 경우, Polling은 CPU Time을 낭비

- 컴퓨터 시스템에서 CPU Time은 매우 귀중한 자원

Polling은 흔히 Programmed I/O로 알려진 방식

참고

- CPU가 Polling의 주최, I/O는 Polling 당하는..

- 장치가 매우 빠른 경우 Event 처리 기법으로 적당하지만, 실제로는 대부분 느리기에 Polling은 그렇게 효율적이지는 못함.

Direct Memory Access (DMA)

Polling이 비효율적이라서, DMA를 도입함.

Polling을 사용할 경우, 모든 I/O 연산은 CPU에 의해 진행

전송할 데이터가 클 경우, CPU를 Polling을 위해 I/O Device의 상태 확인 및 버스에 데이터를 쓰는 행위(PIO)에 사용하는 것은 낭비

DMA Controller라는 프로세서 사용

- CPU와 DMA Controller 간의 통신으로 I/O를 수행

- CPU가 DMA Controller에게 I/O를 요청하면,

DMA Controller는 CPU를 대신하여 I/O Device와 Main Memory 사이의 데이터 전송을 수행- CPU는 I/O 시간 동안 다른 일을 수행할 수 있음

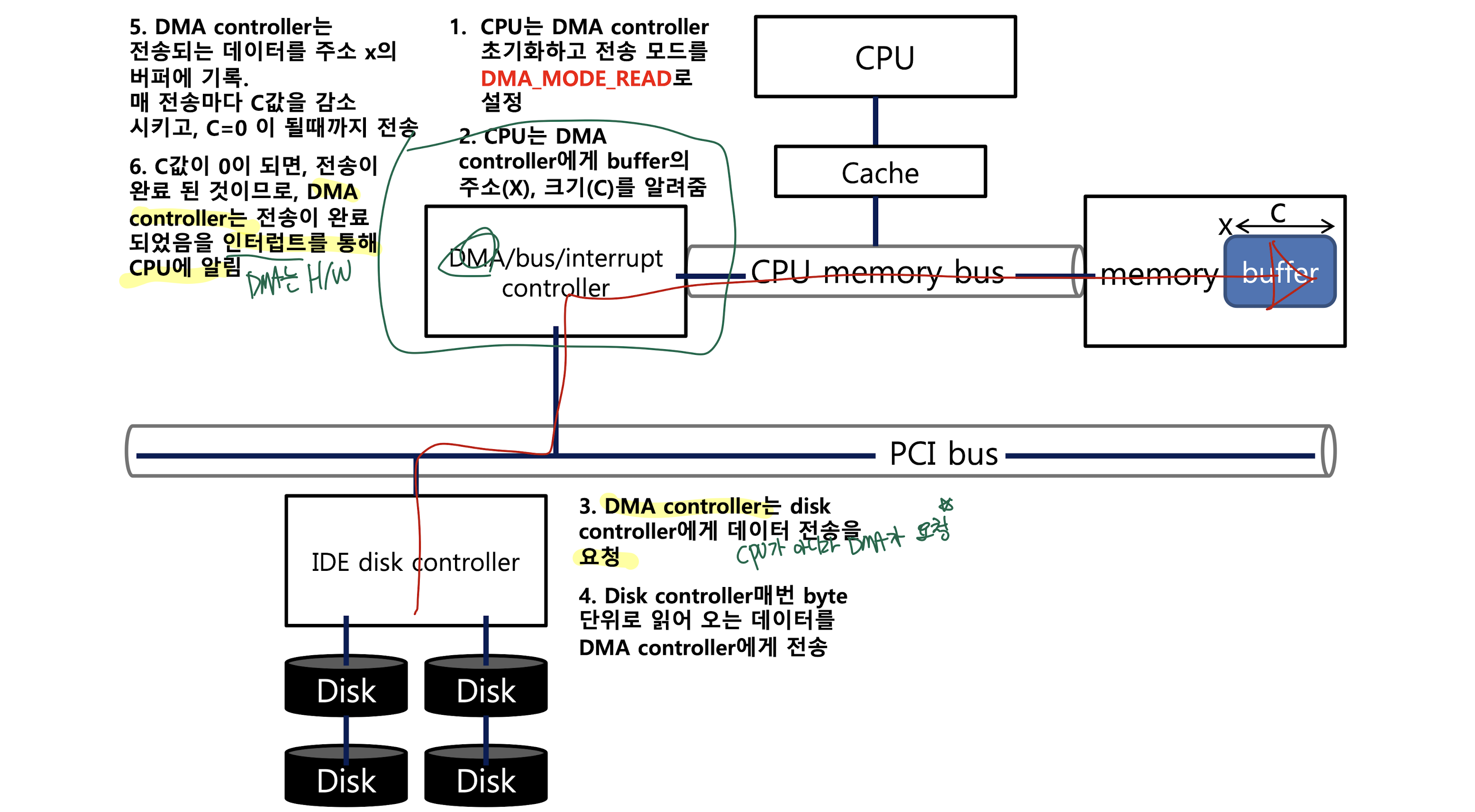

DMA - Read

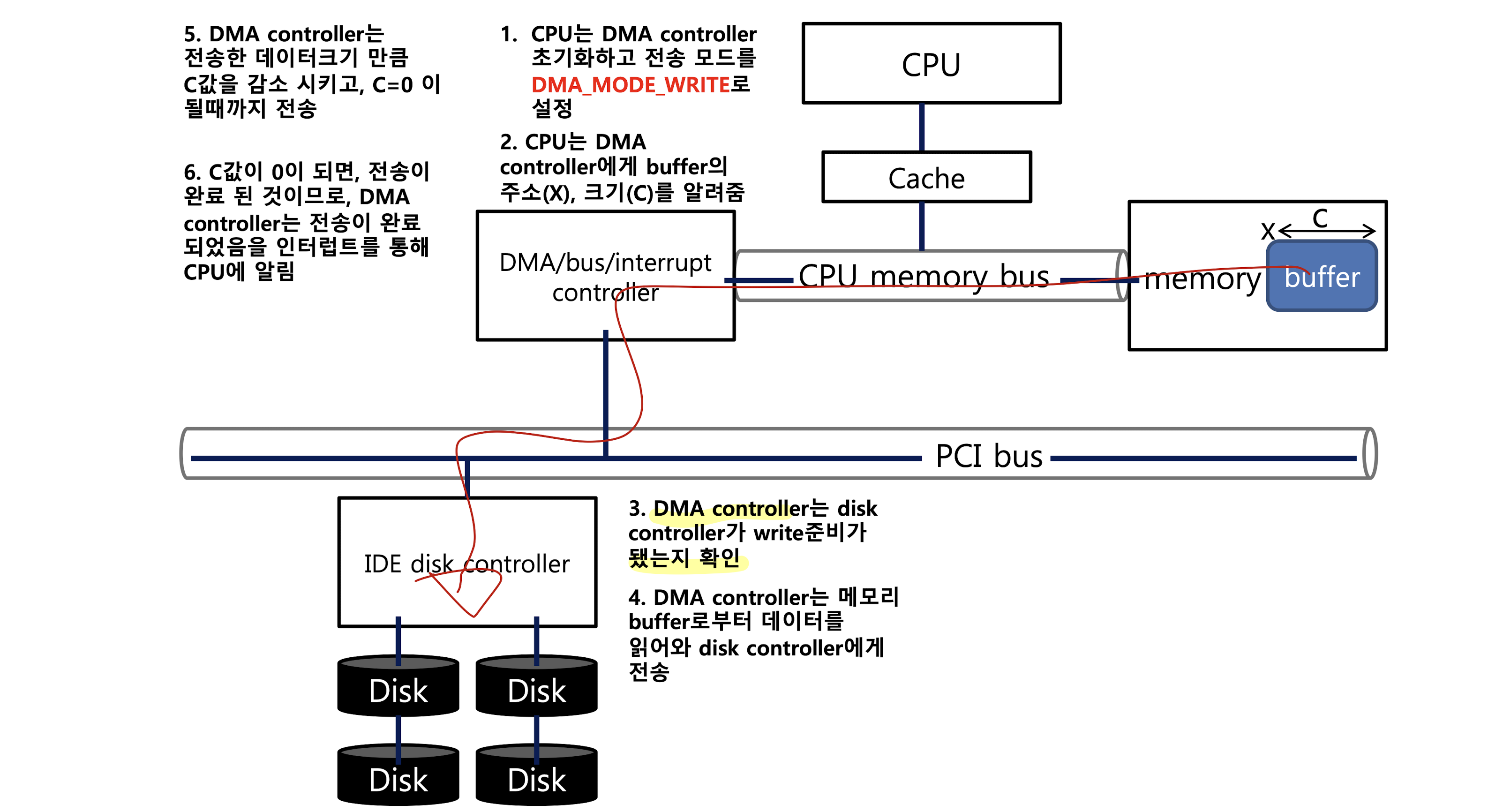

DMA - Write

DMA vs Polling

DMA - 추가적인 Hardware가 필요하다.

성능 - DMA를 최대한 활용하기 위해서는 적당한 Parallelism이 필요

Ex) Smartphone Camera Pixel을 읽어 들이려고 할 때 DMA가 필요한가?

- YES. Pixel을 CPU가 읽으면 한 세월 걸림...

I/O Device Access 기법

I/O Instruction

Controller는 보통 1개 혹은 그 이상의 Register를 가짐

- Data, Control Signal을 처리하기 위함

CPU는 Controller의 Register의 Bit Pattern을 읽고 씀으로써 장치와 통신함

- 이러한 기능을 수행하기 위한 명령어들이 제공됨

Memory Mapped I/O

Device Register들을 Memory 공간에 Mapping하여 사용

- Device Register가 Memory 주소에 Mapping이 되면, Register들은 주소 공간의 일부로 여겨짐

CPU는 일반적인 명령어를 사용하여 I/O 작업을 수행

운영체제에서 필요한 H/W 요점

컴퓨터 시스템의 전체적인 구성

- 버스

I/O Event Mechanisms

-

Interrupt

-

Trap

I/O Handling Mechanisms

-

Polling

-

DMA

요약 및 정리

CPU가 매우 빨라서 일을 다 시키면... 과부화...

생산적으로, 효율적으로 일을 시키면서 과부화를 줄이려면 어떻게 해야할까.

=> Interrupt / Trap & Polling, DMA를 이용하자.