Memory Management

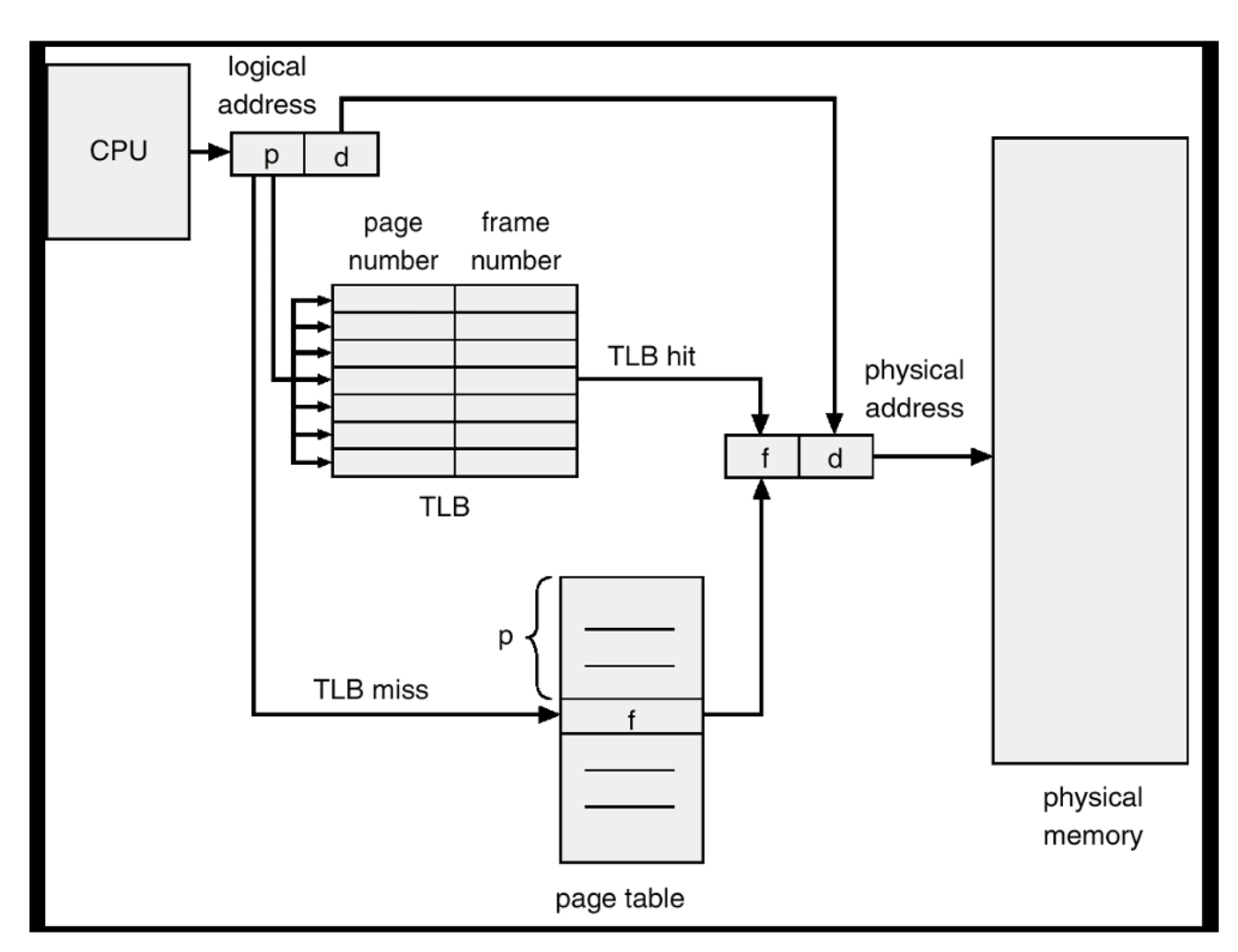

TLB

- Translation Lookaside Buffer

- 페이징 방법: 데이터 접근을 위해서 (1). 페이지 테이블 (2). 물리 메모리 데이터 접근 등 두 번 필요 → 메모리 접근 속도 저하

- MMU에서의 TLB 사용: (1). 페이지 테이블 이용 변환 주소를 TLB에 저장 (2). TLB 캐시 히트 가능(TLB=레지스터) (3). TLB hit ratio: 원하는 주소를 찾을 수 있는 확률. 높을 수록 메모리 접근 속도 높다는 뜻 (4). TLB miss ratio: 1 - TLB hit ratio. 미스한 경우 페이지 테이블을 통해 물리 메모리의 데이터 주소를 알아내서 다시 테이블에 기록해야 함

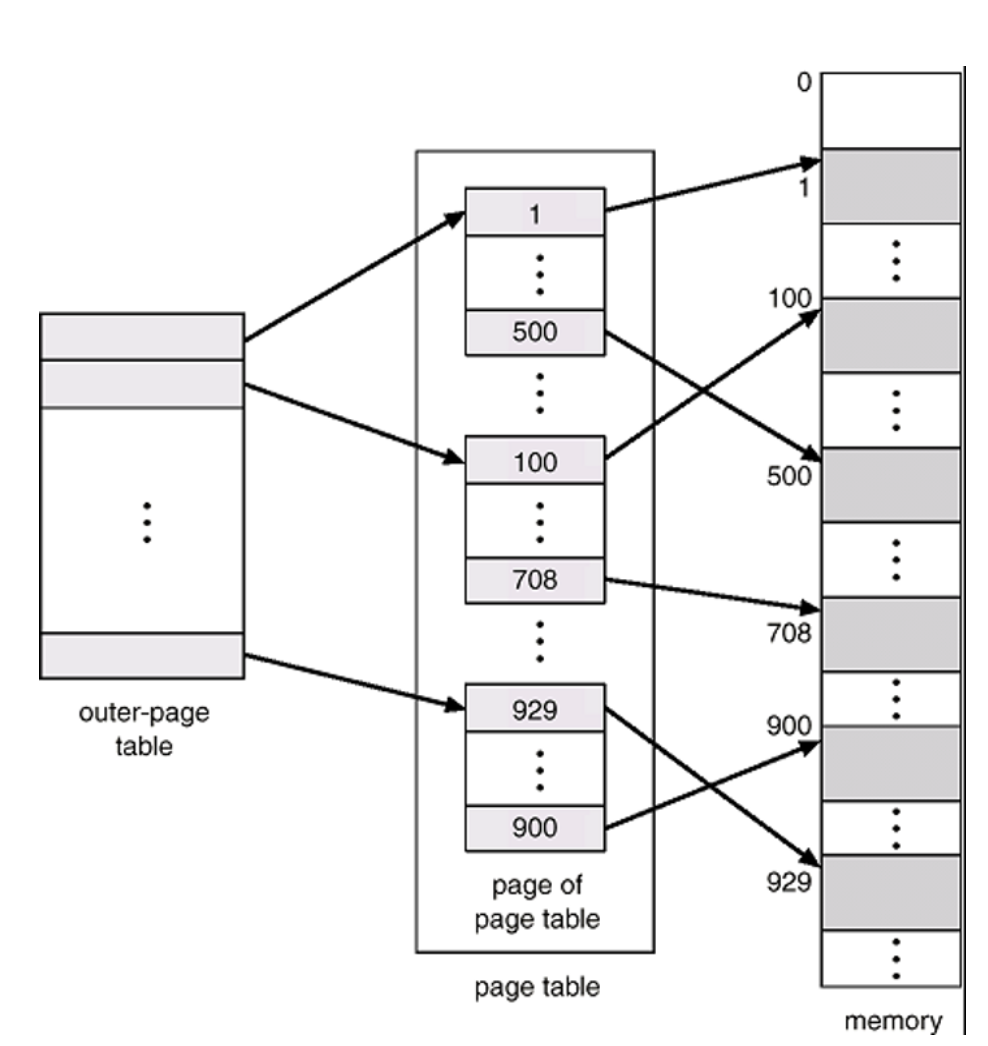

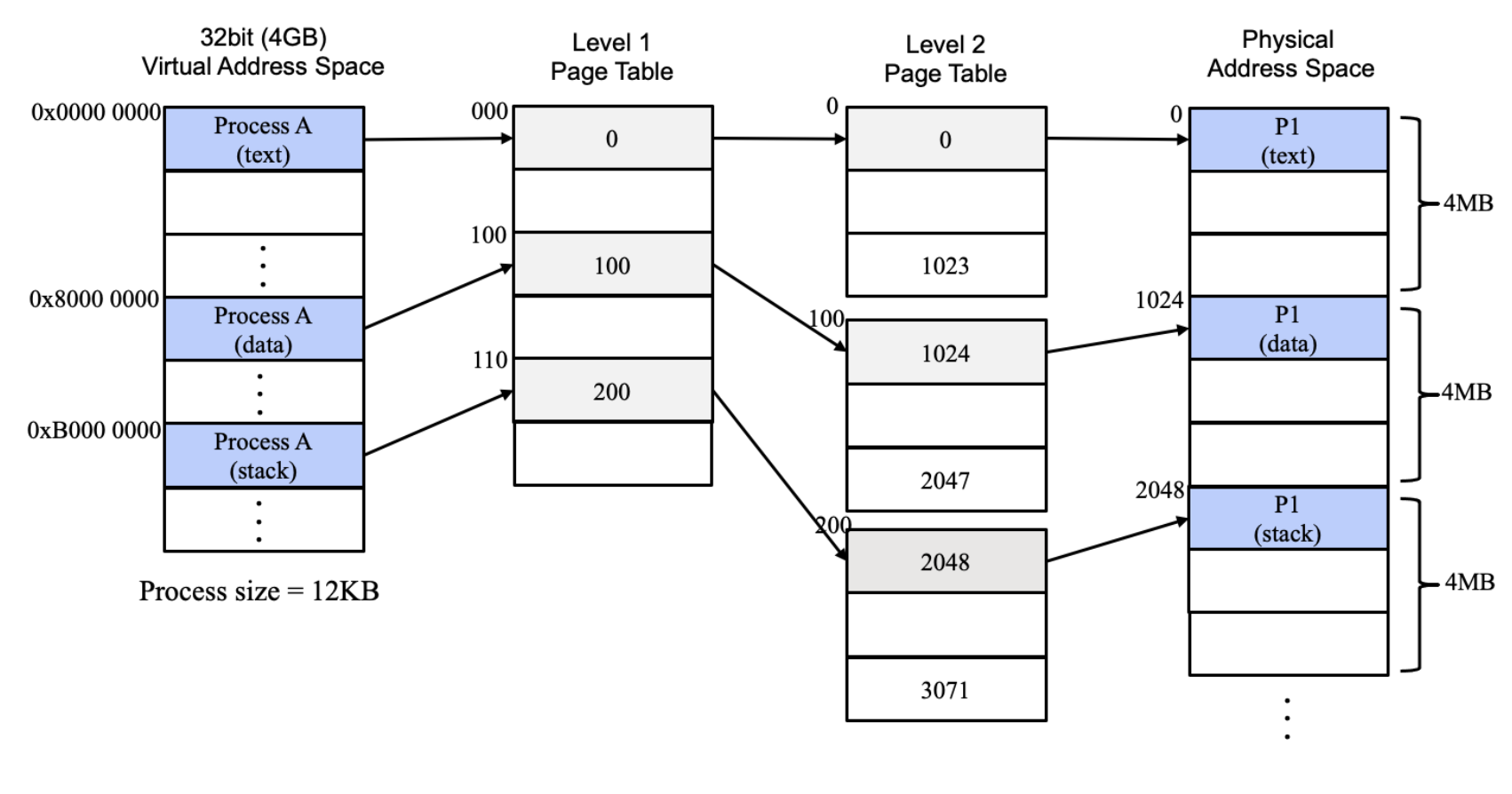

Multi-level Page Table

-

sparse한 페이지 테이블은 오버 헤드 큼.

-

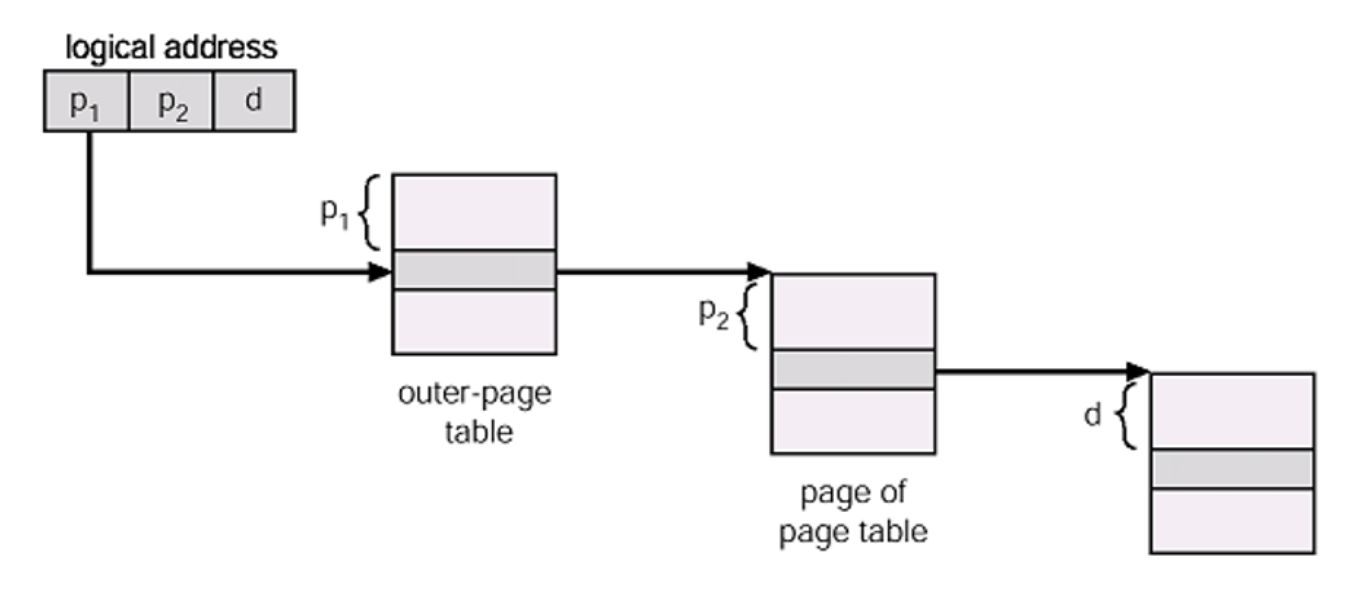

Outter, Inner 페이지를 통해 각각 10비트씩 나누는

2-level page table→ 20비트 페이지 번호를 10비트 두 개로 나누고, 이 두 개는 11비트로 표현할 수 있음

-

페이지 테이블을 찾아가는

Table Walking→ 페이지 테이블 시작 주소에서 P1 이동, P2 이동, d 오프셋 이동한 실제 피지컬 메모리 데이터 X 도착 -

32비트 컴퓨터의 경우 2 level 페이지 테이블 기법을 통해 매우 쉽게 오버헤드를 줄일 수 있음

-

64비트 컴퓨터의 경우 42비트 P1, 10비트 P2, 12비트 오프셋 비트로 사용하게 되는 2 level 페이지 테이블 기법이 적용되기 때문에 그렇게 효율적이지 않음(2^42 비트 크기는 매우 비효율적)

64비트에 적합한 용도로 레벨을 늘리게 되면 outter 페이지가 여러 개로 늘어나게 된다! 하지만 페이지 레벨이 많을 때 생기는 시간 부담을 감수해야 한다.

- 페이지 개수가 많아지면 페이지 용량은 감소하지만 페이지 테이블을 탐색하는 워킹 시간은 증가. 비효율적

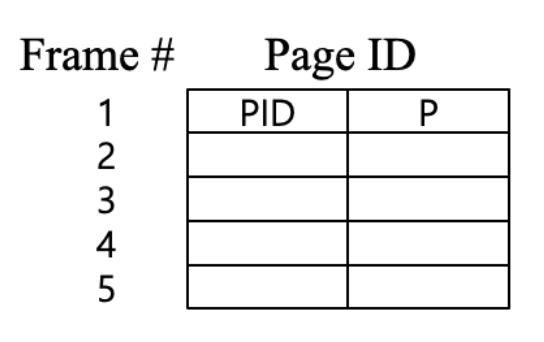

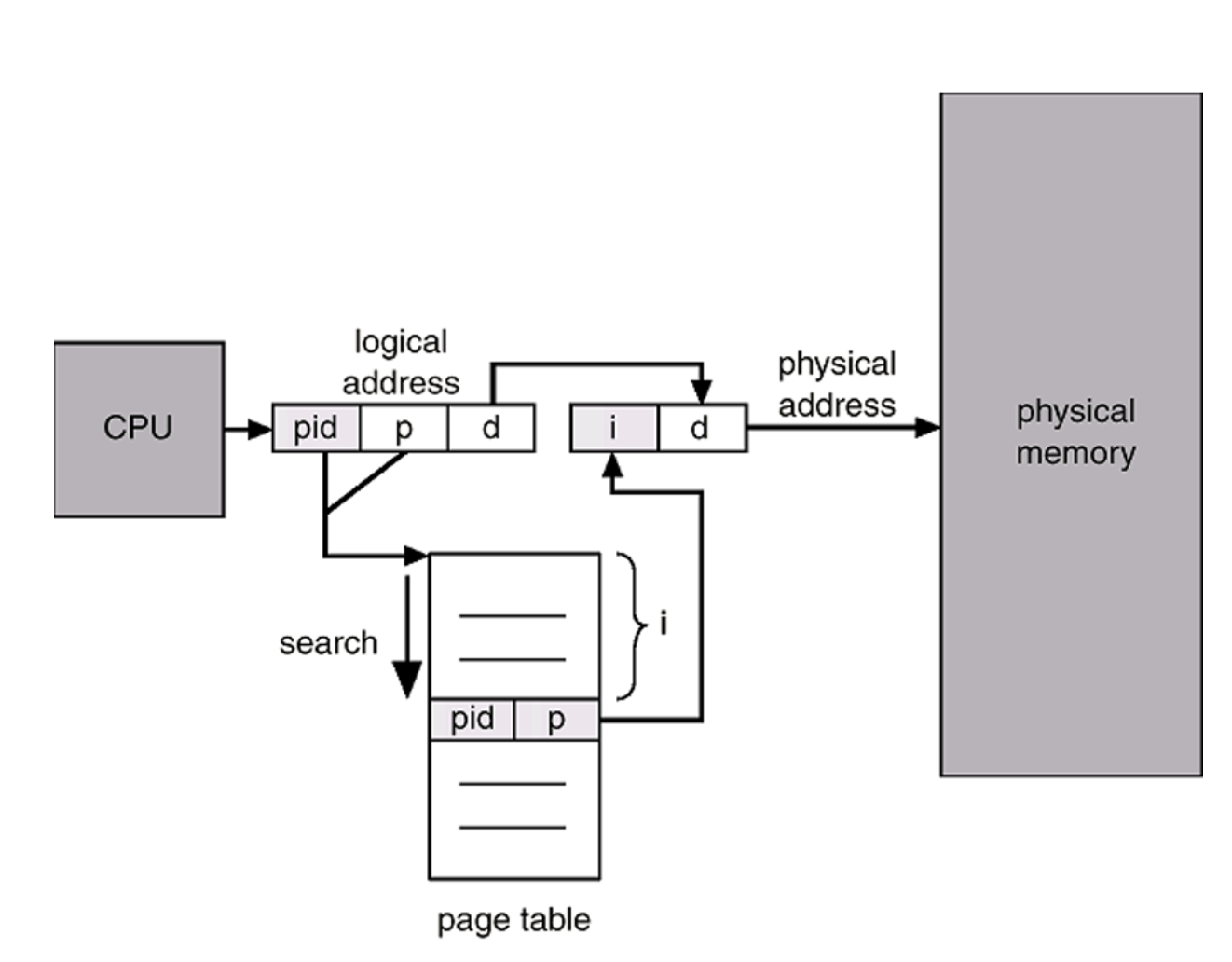

Inverted Page Table

- 모든 물리 메모리는 가상 메모리 페이지에 등록되어 있을 확률이 높음

- 물리 메모리를 일종의 인덱스로 사용하는 방법

모든 가상 메모리가 모든 물리 메모리에 할당되어 있지 않기 때문이다!

- PID, P를 함께 사용하는 까닭: 페이지 번호(P)는 모든 프로세스가 공통적으로 가지기 때문에 PID를 통해 식별자로 사용한다.

- CPU 참조하는 주소 + PID 조합을 통해 페이지 테이블 내에서 페이지 ID를 검색한다. 페이지 ID를 발견하면 해당 프레임 번호를 가상 주소 공간으로 매핑한다.

- 시스템 전체 - 페이지 테이블 하나만 존재. PID, 페이지 번호를 통해 물리 프레임을 검색해야 함

- 작은 용량의 페이지 테이블이지만 검색하는 데 시간이 오래 걸리는 단점(해쉬 테이블을 통해 오버헤드 줄일 수 있음)

PID, P를 통해 페이지 테이블을 검색하고, 오프셋 d를 더해 물리 메모리 주소로 곧바로 찾아간다!

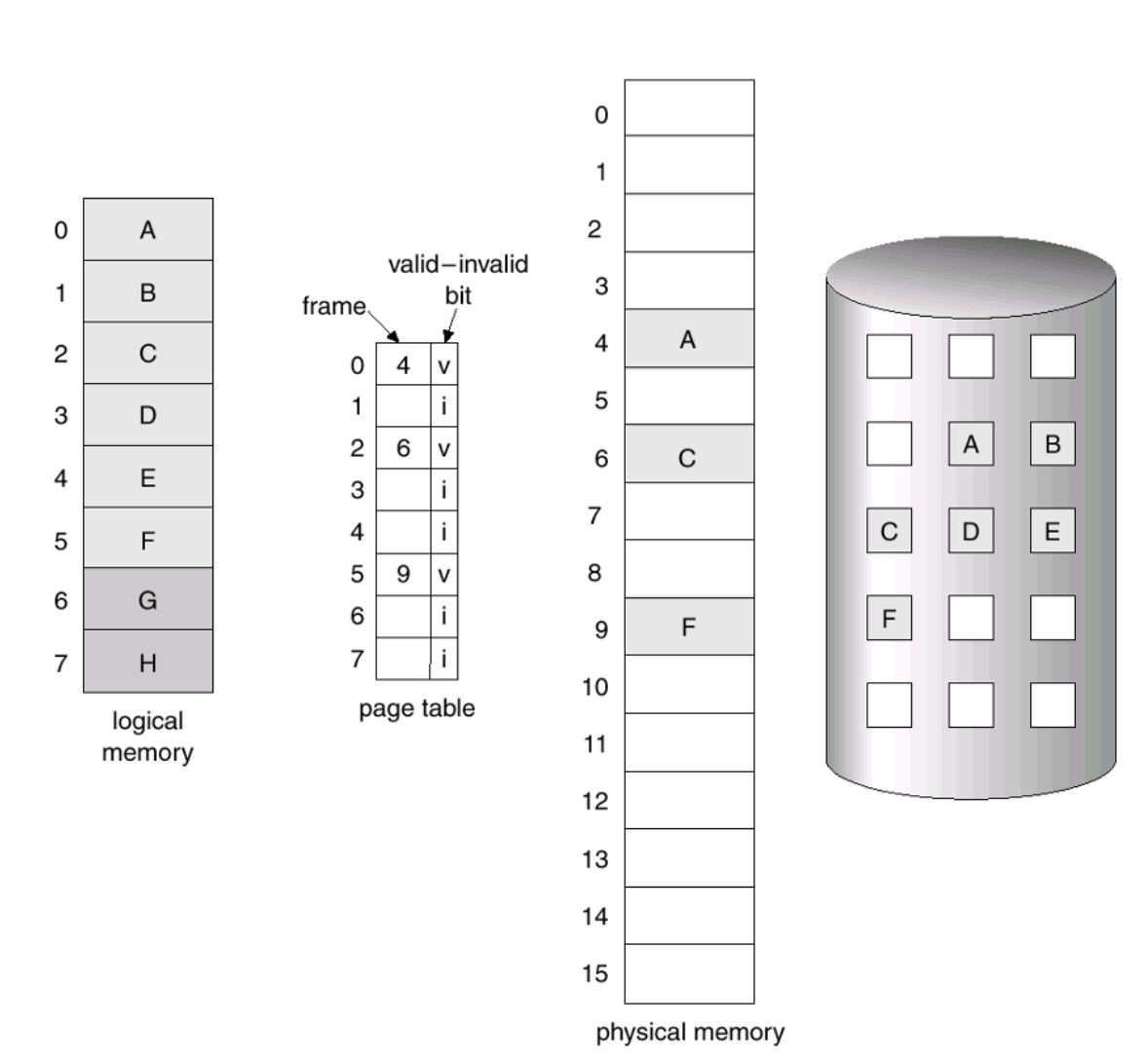

Demand Paging

- 프로세스 실행을 위한 모든 페에지를 메모리에 올리지 않고 필요한 페이지 요청이 있을 때 메모리에 올리는 방법

- 메모리와 세컨더리 스토리지 사이에서 필요한 페이지를 이동시키는 방법: valid/invalid page(피지컬 메모리에 매핑되어 있는지, 즉 현재 사용 여부를 체크하는 플래그 비트)

- E.g.) 4, 6, 9번 할당 → 피지컬 메모리에 할당받은 상태. 다른 페이지는 Invalid 비트로 표시되어 있기 때문에 이를 요청(demand)할 때

swap-in될 것!

- 장점: 프로세스 실행을 위한 피지컬 메모리 할당 시간이 줄어든다. 프로세스 전체 메모리를 피지컬 메모리에 올리지 않기 때문에 메모리 부담이 감소한다. 프로그램을 시작할 때 올려야 하는 메모리 양도 적어지기 때문에 시작하는 데 소요되는 시간이 감소한다.

- 단점: (1). 참조 페이지가 valid한 경우: 정상 참조 가능 (2). 참조 페이지가 invalid한 경우: 정상 참조 불가능. 페이지 폴트 발생

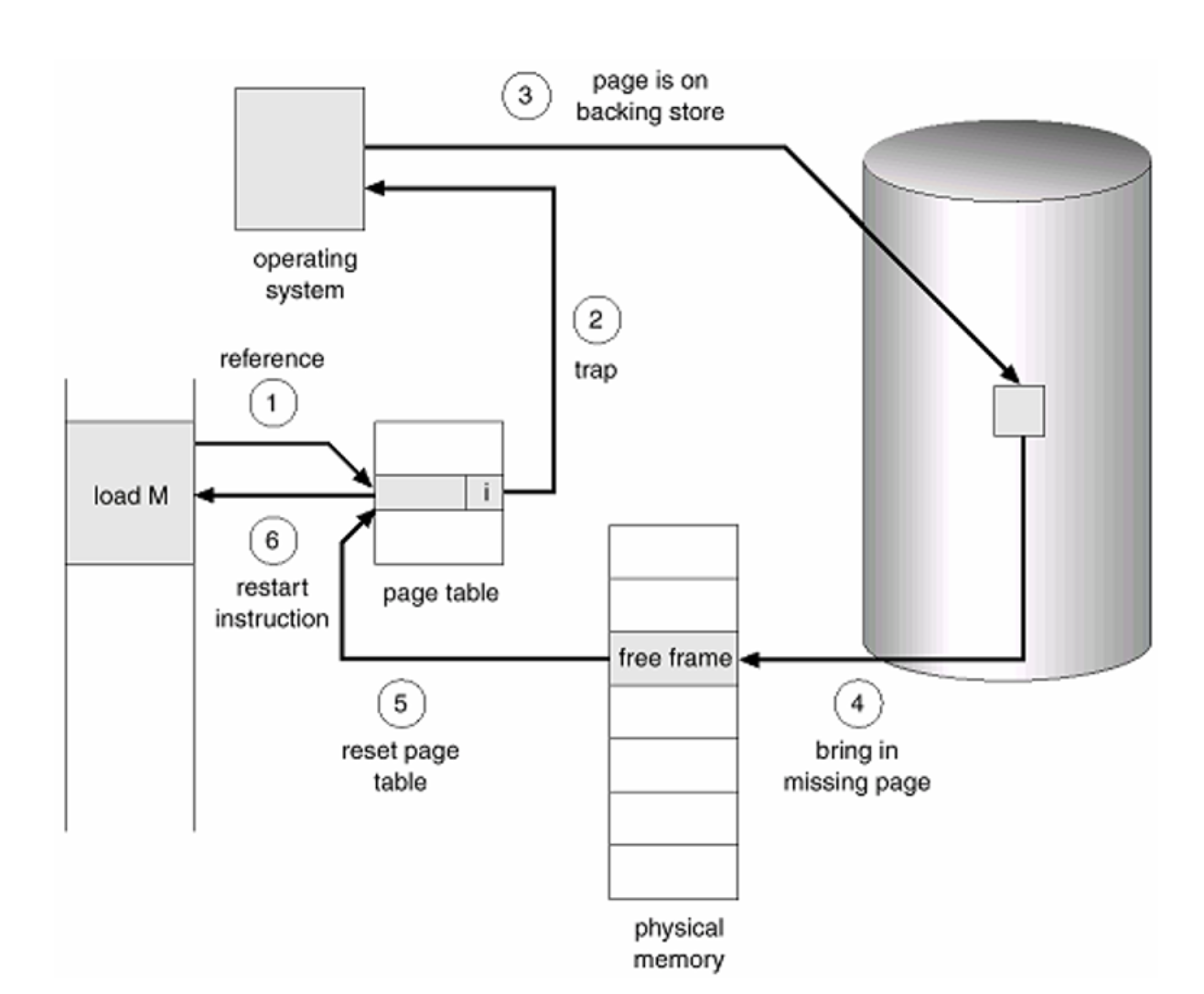

Page Fault

- 프로세스가 페이지를 참조했을 때 페이지가 할당받은 프레임이 없는 경우

- 페이지 폴트: 프레임을 새로 할당받아야 하는 경우이므로 페이지 폴트 핸들러 실행

- 새로운 프레임을 할당받기

Baking store(storage)에서 페이지 내용을 다시 프레임에 가져오기- 페이지 테이블 재구성하기

- 프로세스 작업을 재시작하기

- 트랩: 페이지 폴트는 동기적 이벤트이기 때문에 트랩 핸들러 호출 → OS가 세컨더리 스토리지에 존재하는 페이지를 프리 프레임(현재 페이지가 할당되어 있지 않은 피지컬 메모리의 한 부분)에 적재한다.

페이지 폴트의 개수는 프로그램 성능과 직결! 프레임의 개수와 페이지 폴트의 발생 빈도는 일반적으로 반비례. 프레임이 많다면 찾아야 할 가상 주소의 페이지가 할당될 가능성이 높기 때문이다!

Summary

- 메모리 관리: 피지컬 메모리는 한정. 여러 개의 프로그래밍을 멀티 프로그래밍하기 위해 효율적으로 사용해야 한다. 따라서 가상 메모리를 사용하게 되고, MMU를 통해 효율적으로 관리 + 페이지 테이블을 통해 캐시할 수 있다.

- 페이지 테이블: 주소 공간을 일정 크기로 나누어 버추얼/피지컬 메모리를 매핑할 때 사용하는 자료 구조. TLB를 통해 캐시 가능

- Demand Paging: 필요한 페이지만 그때마다 메모리에 적재해서 사용하는 방법. 요청한 페이지가 메모리에 존재하지 않는다면 페이지 폴트 발생