Memory Management

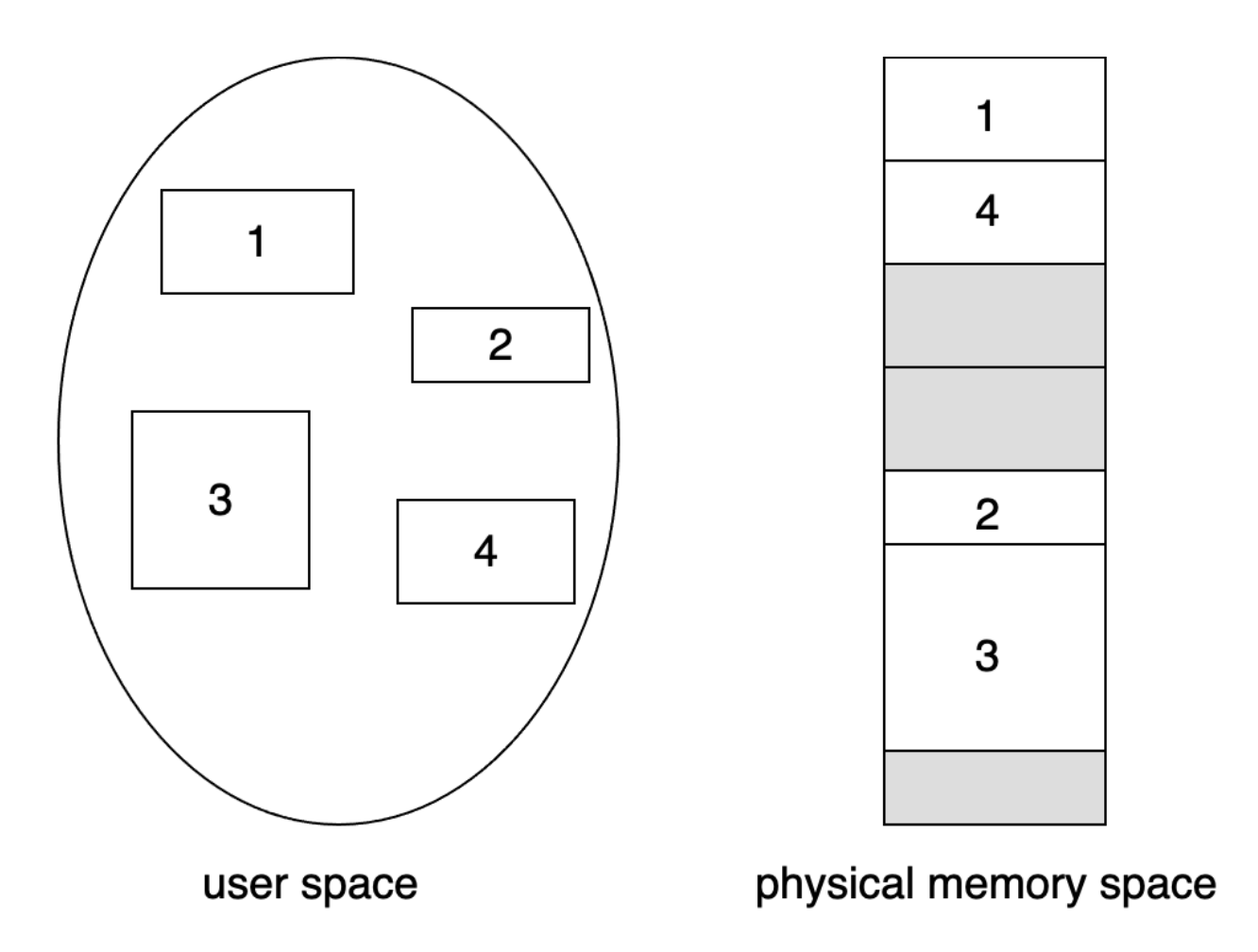

Segmentation

- 메모리 관리 방법: 메모리의 유저 뷰를 지원

- 프로그램은 세그먼트의 집합

- 세그먼트: 메인 프로그램, 프로듀서, 함수, 메소드, 오브젝트, 로컬 변수, 글로벌 변수, 일반 블록, 스택, 심볼 테이블, 배열 등

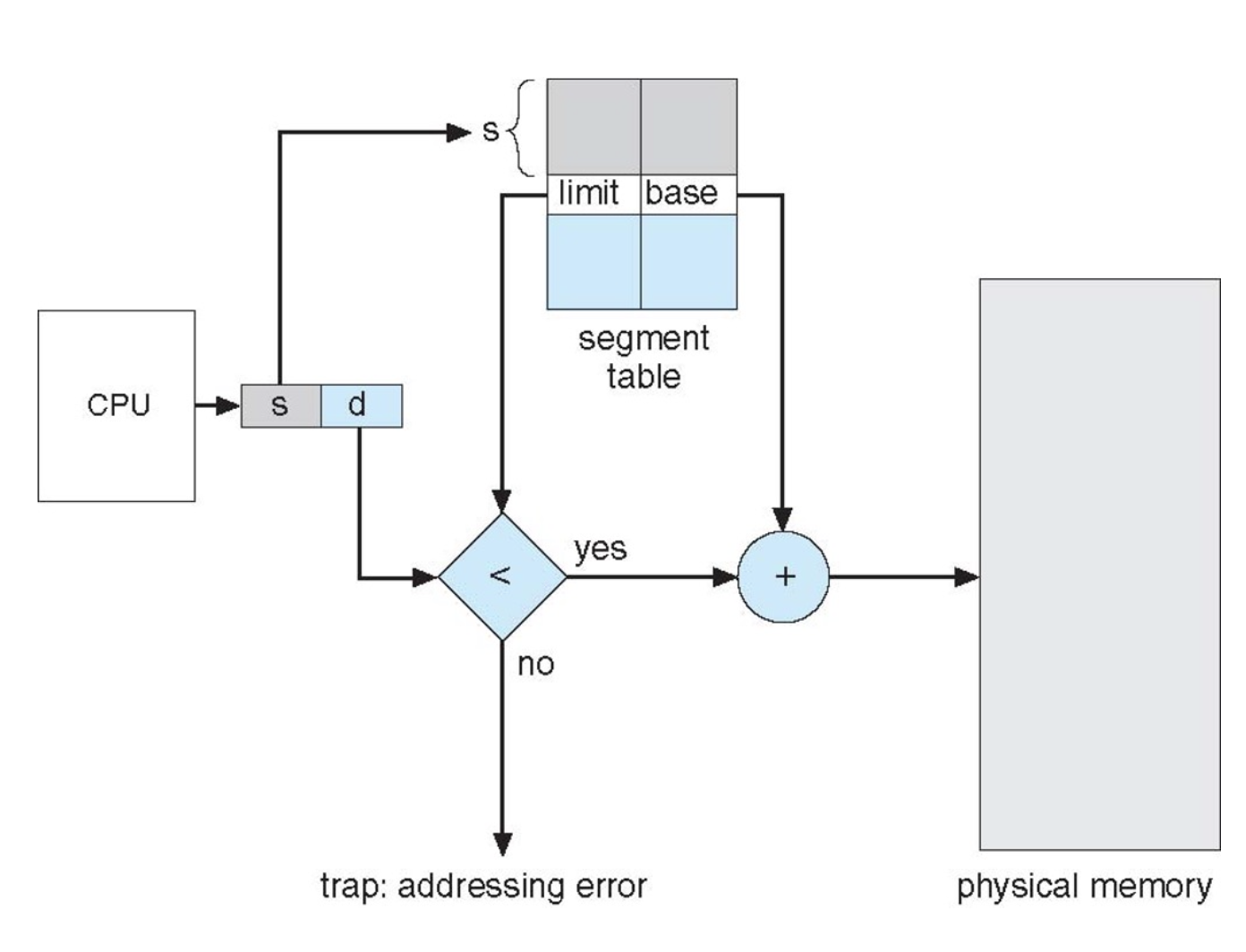

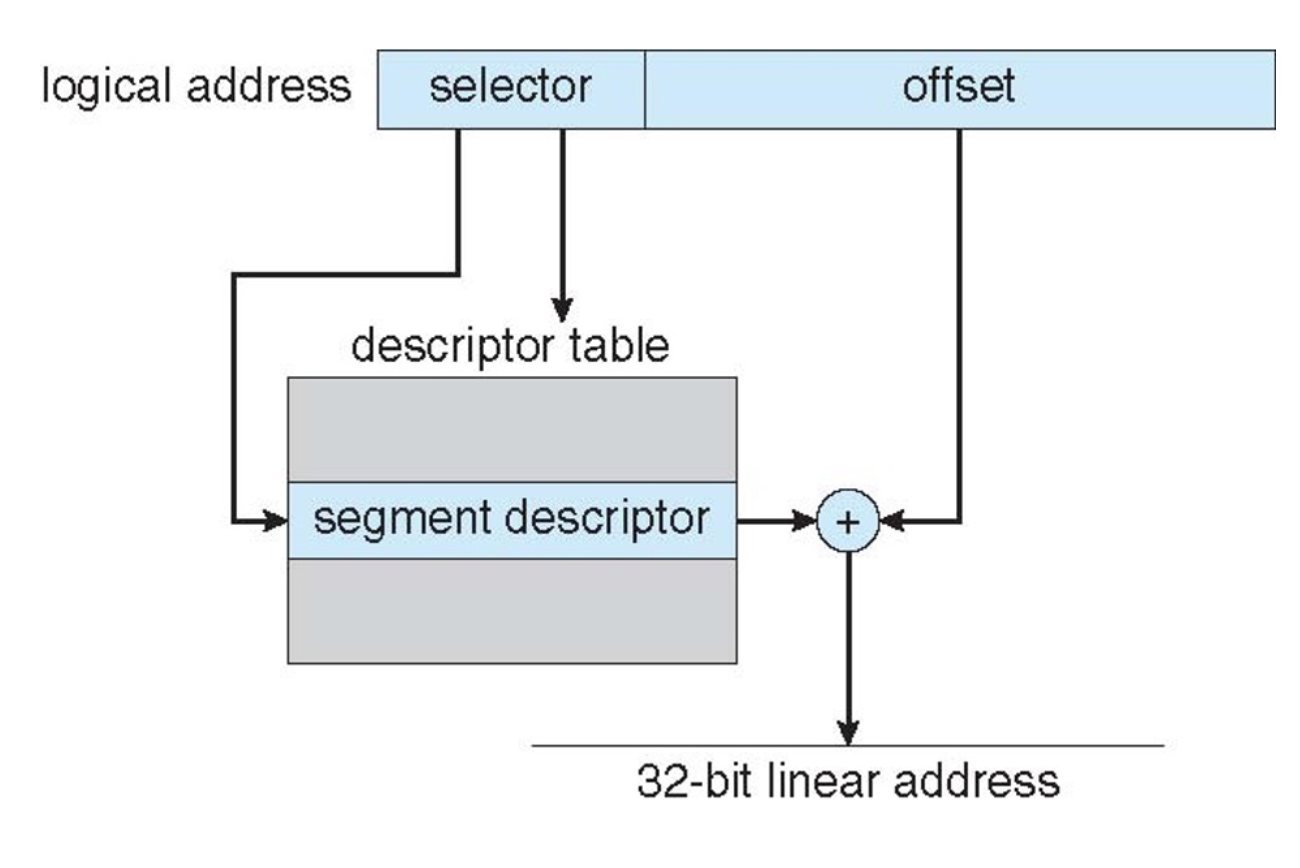

- 논리적 주소를 세그먼트 번호 + 오프셋으로 분리 → 세그먼트 테이블을 통해 물리 주소를 알아낼 수 있음(

base,limit필요) - limit: 4KB 크기로 한정된 페이지와 달리 컴파일 시에 어떤 크기로 할당될지 모르기 때문에 별도의 자료 구조를 통해 전달해야 함

- STBR(Segment-table base register): 메모리 내 세그먼트 테이블 위치

- Protection: 각 엔트리가 세그먼트 테이블과 연관되어 있는 유저 스페이스에만 접근할 수 있도록

validation bit체크. 추가적으로 읽기/쓰기 권한을 줌으로써 사용자에 따라서 조정 가능

- E.g.) S를 통해 세그먼트 시작 주소 파악. Limit 범위까지만 체크 가능. 초과하지 않았다면 base에 넣어서 피지컬 메모리에 접근 가능(벗어났을 때에는 트랩을 통해 잘못된 접근으로 트랩 핸들러 호출).

Fragmentation

- 세그먼트 사용 중 발생할 수 있는 이슈

- External Fragmentation: 남아 있는 메모리 공간이 요청받은 메모리보다 크지만, 분리되어 있어서 요청 받은 메모리를 넣을 수 없을 때

- Internal Fragmentation: 남아 있는 메모리 공간에 요청받은 메모리를 넣을 수 있지만 완전히 들어맞지는 않아서 낭비되는 조그마한 공간이 있는 경우. 이 공간을 다른 요청에 할당할 수 없기 때문에 낭비가 생길 때

최대한 메모리를 효율적으로 사용할 수 있도록 매핑하자!

- 메모리가 있을 때에 1/3이 사용하기 부적합해진다는 법칙이 존재. 추가적인 방법으로 이를 줄일 수 있다!

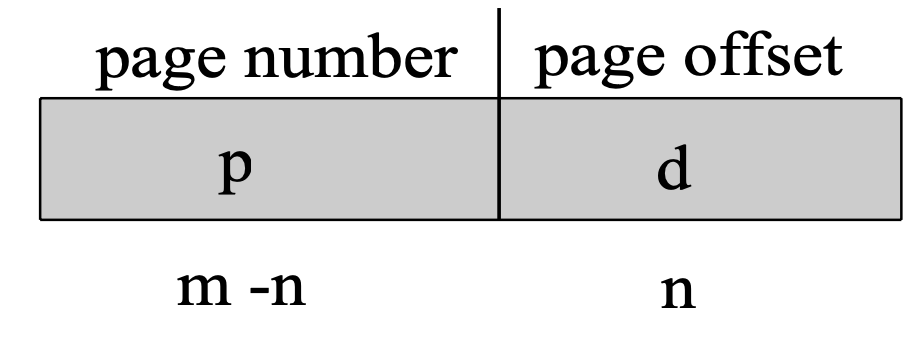

Paging

- 프로세스의 피지컬 주소 공간은 비연속적

- 페이징 기법을 통해 External Fragmentation을 방지할 수 있음 - 메모리 블럭의 크기가 4KB 프레임 크기로 유지되기 때문

- 물리 메모리 할당 시 N 페이지, N 프레임을 매핑, 추후 프로그램 실행 가능

- 페이지 테이블을 통해 논리적 주소를 물리적 주소에 번역

- Internal Fragmentation은 여전히 해결 X(피지컬 메모리에 프레임을 사용하더라도 비연속적으로 적재되어 있기 때문)

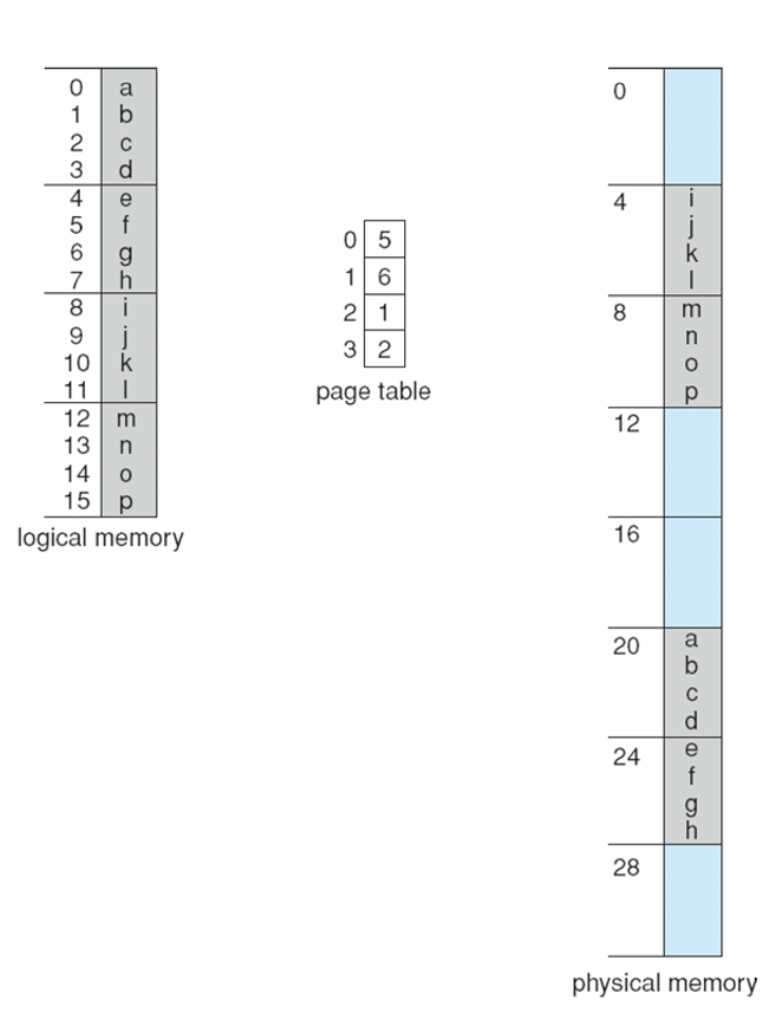

- CPU의 주소는 페이지 번호 및 페이지 오프셋으로 분리된다. 이때 주어진 논리적 주소 크기는 2^m, 페이지 크기는 2^n이다.

- E.g.) 논리적 주소 크기는 2^4 = 16바이트, 페이지 크기는 2^2 = 4바이트이다. 피지컬 메모리의 한 페이지는 4바이트이다.

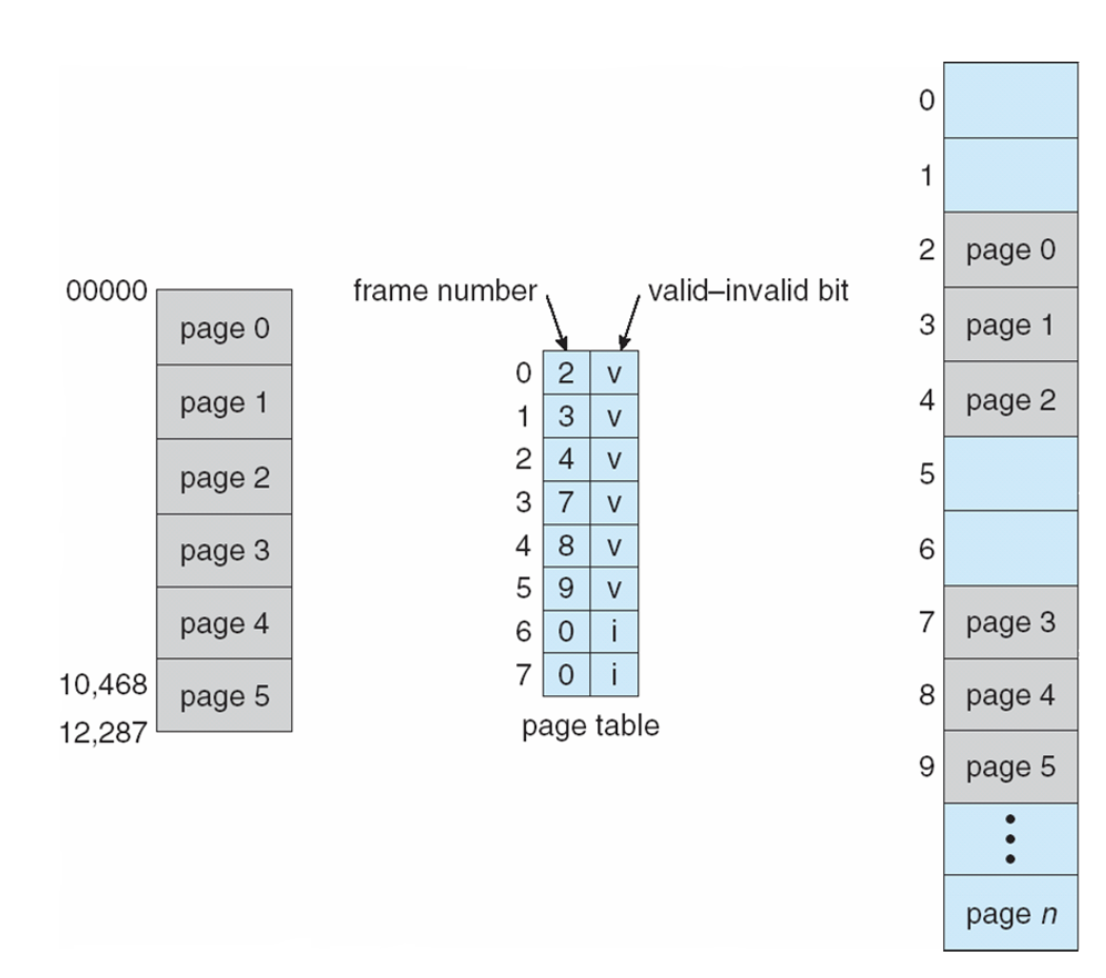

Memory Protection

- protection bit를 각 프레임에 할당 → 읽기 전용 / 읽기 쓰기 모두 가능 접근을 선택할 수 있음

- 페이지 테이블의 각 엔트리에 붙은 vaild-invalid 비트: 프로세스의 논리적 주소 공간에 존재한다면 valid, 그렇지 않다면 invalid. 또는 PTLR을 통해 어디까지 접근할지 명시해서 확인

- 위반 사항(violation)이 존재한다면 동기적 이벤트를 처리하는 트랩 핸들러 호출

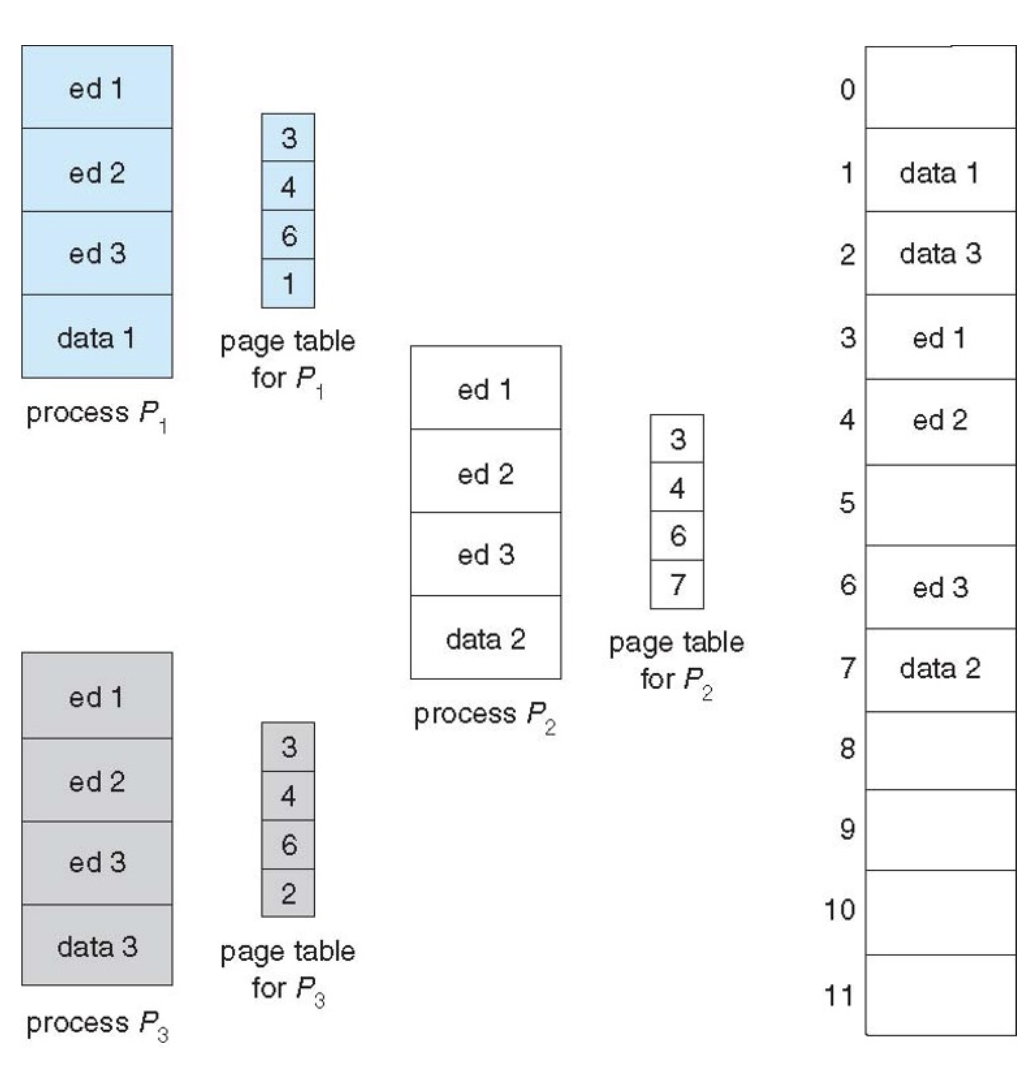

Shared Page

- 여러 개의 프로세스 상 코드 공유가 필요할 때

- E.g.)

lib.c라이브러리를 통해 호출될 때 주소 공간을 효율적으로 사용하기 위해 동일한 코드의 중복 사용 X - E.g.) P1, P2, P3가 동일한

ed1,ed2라는 공유 페이지를 참조할 수 있기 때문에 메모리 효율적 - 보안이 필요한 코드는 페이지 테이블 플래그 비트를 설정함으로써 따로 설정 가능

Intel 32, 64 bit Architectures

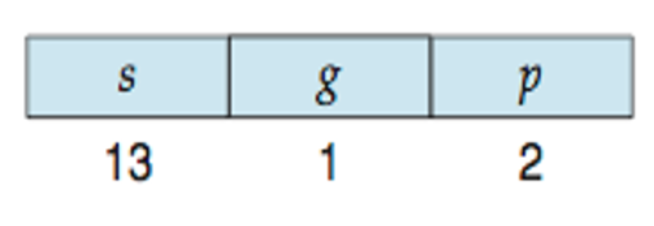

Intel IA-32 Architecture

- segmentation, paging 모두 지원

- 각 세그먼트 사이즈는 4GB(32비트 컴퓨터가 표현 가능한 가장 큰 길이): 프로세스 당 16K 세그먼트

- 두 파티션으로 분리: (1). 처음 8K는 private, (2) 두 번째 8K는 shared

- s가 세그먼트 번호, g가 상태 비트, p가 오프셋 담당 비트

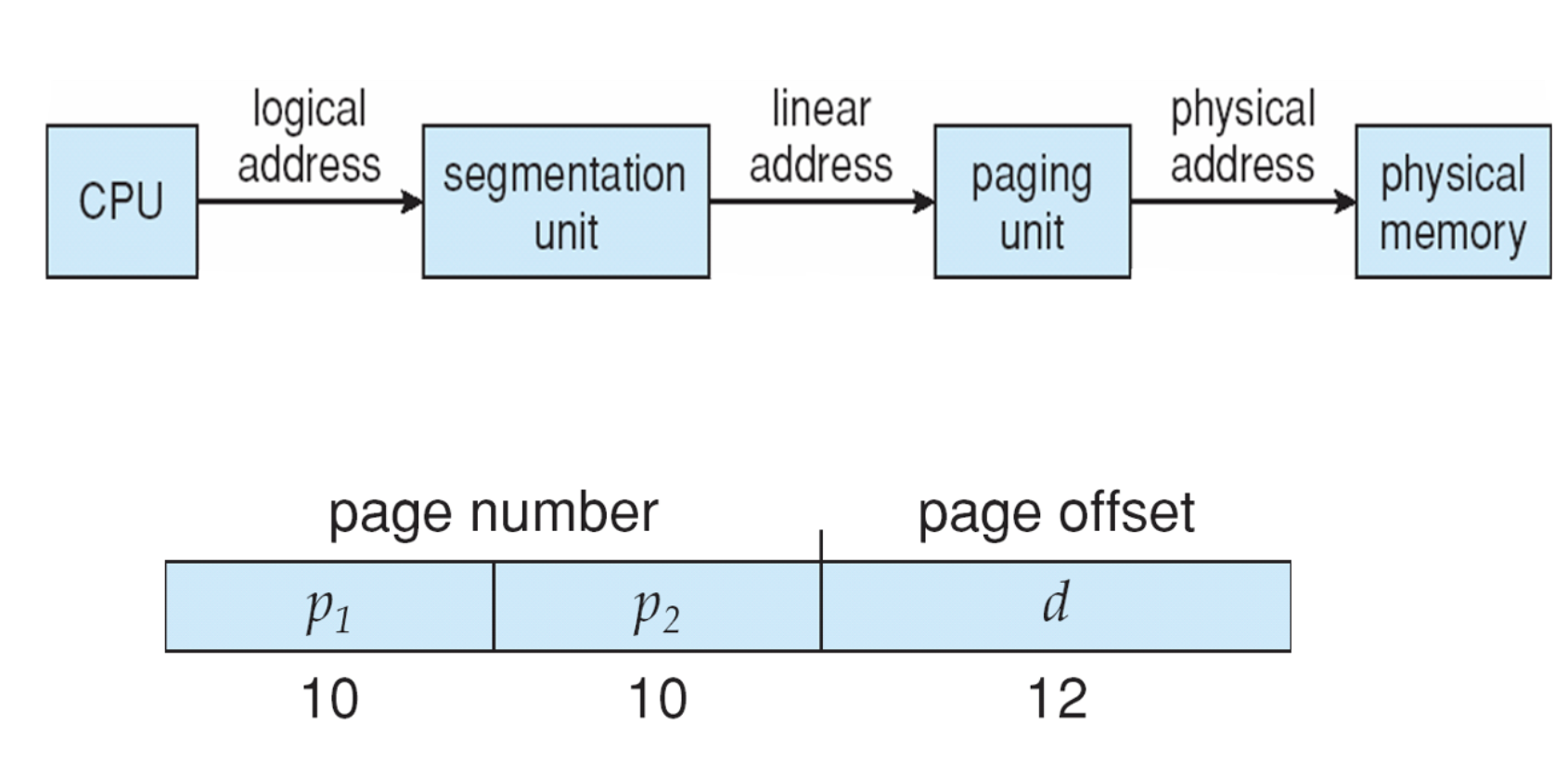

- 논리적 주소 → 연속 주소 → 물리적 주소 접근

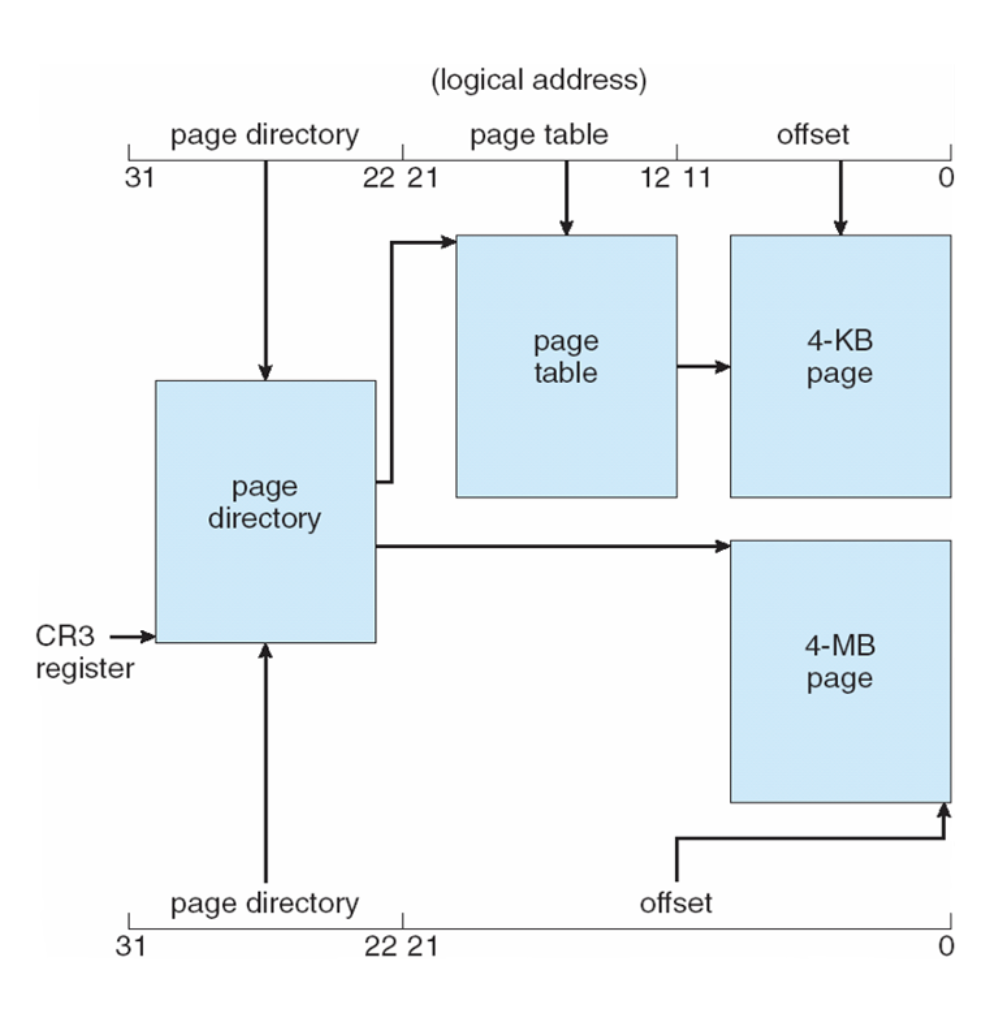

- 리니어 주소에서는 페이지 디렉토리 접근 → CR3 레지스터 접근(프로세스마다 서로 다른 페이지 디렉토리 가짐) → 페이지 테이블에서 페이지 테이블 번호 체크 → 오프셋을 통해 피지컬 메모리의 프레임 체크

- 4MB 페이지를 사용하기 위해서는 22비트의 오프셋을 사용해야 함. 나머지 10비트만 페이지 디렉토리를 위한 용도로 사용.

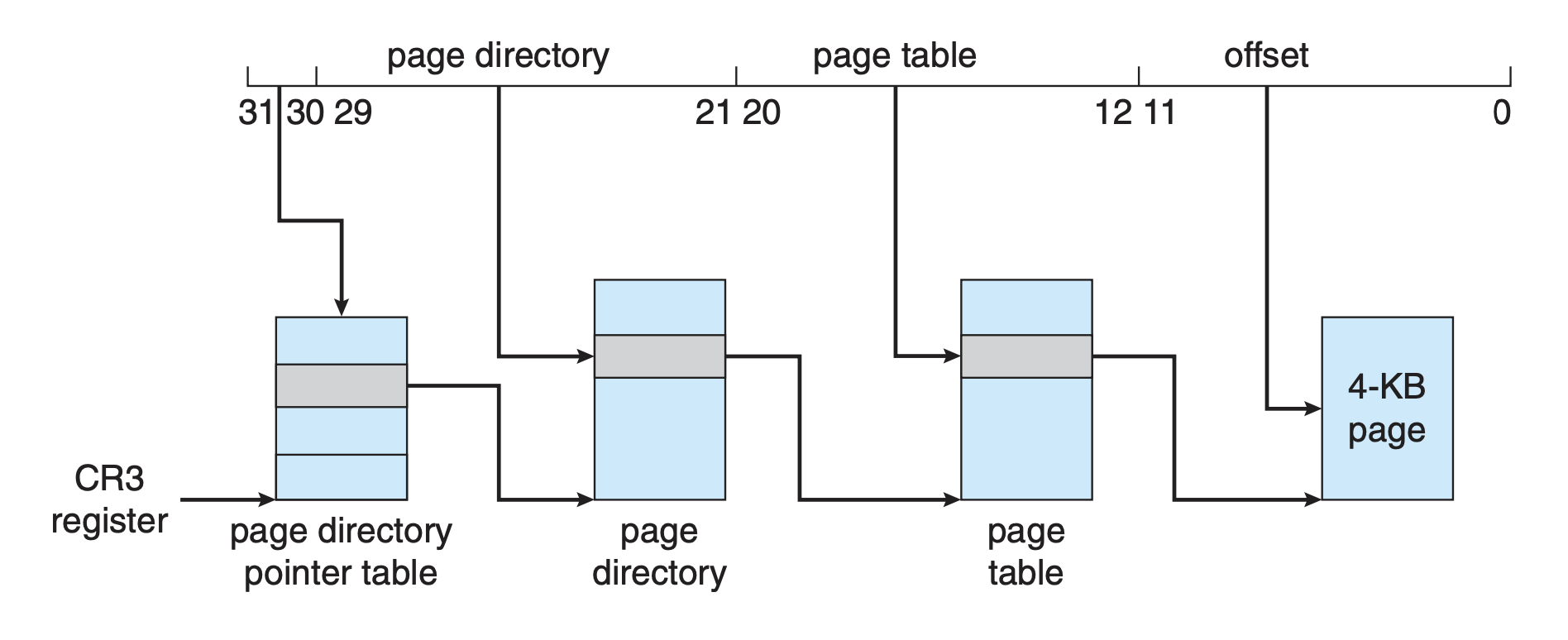

Page Address Extension

- 32비트 컴퓨터에서 4GB 바이트 이상의 메모리를 사용하는 프로그램을 사용할 수 있도록 지원하는 방법(4GB: 2^32비트로 표현 가능한 가장 큰 주소)

- 3-레벨 멀티 페이지 사용하기 → 64비트 지원 가능(2비트의 페이지 디렉토리 포인터 테이블을 사용함으로써 32비트/32비트 총 64비트 표현 가능)

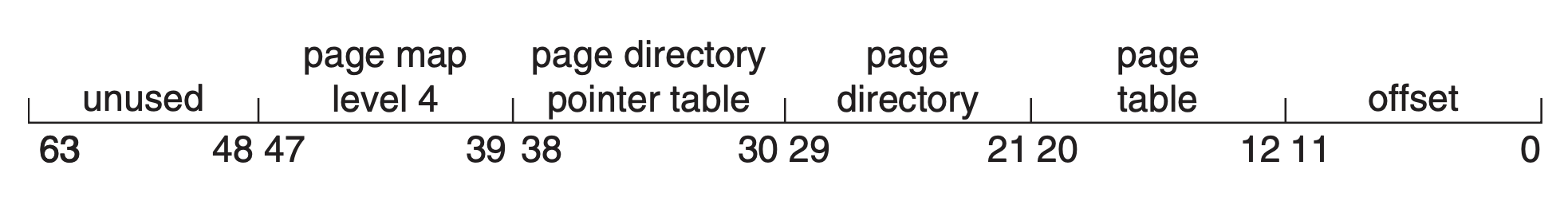

Intel x86-64

- 64비트로 표현 가능한 메모리 공간은 매우 큼. 일반적으로 48비트 정도를 주소 공간 표현에 사용함

- 페이지 테이블 레벨은 최대 4레벨까지 지원 가능

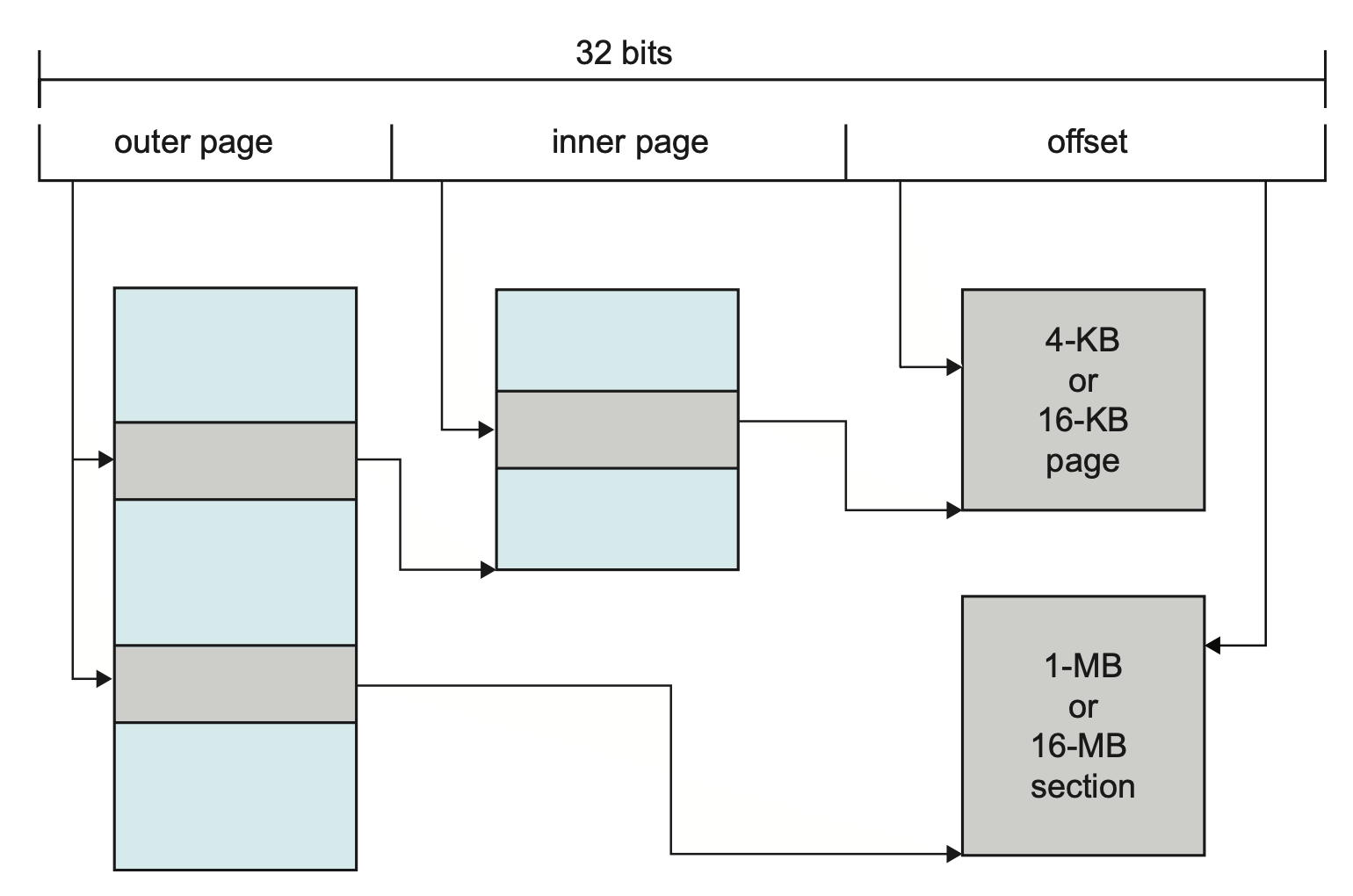

ARM architecture

- 모바일 칩 시장에서 가장 우위를 점하는 칩

- 4KB, 16KB, 64KB 페이지

- 4레벨의 페이지 테이블을 제공

- TLB 레벨이 2레벨: Micro, Main 두 종류 존재. 두 종류의 캐시를 통해 매우 효율적으로 페이지 테이블을 사용하기 위한 방법(Micro, Main, Page Table 순서의 Table walking). 페이지 테이블을 최대한 적게 사용하기 위해 캐시 히트 비율을 높이기 위함