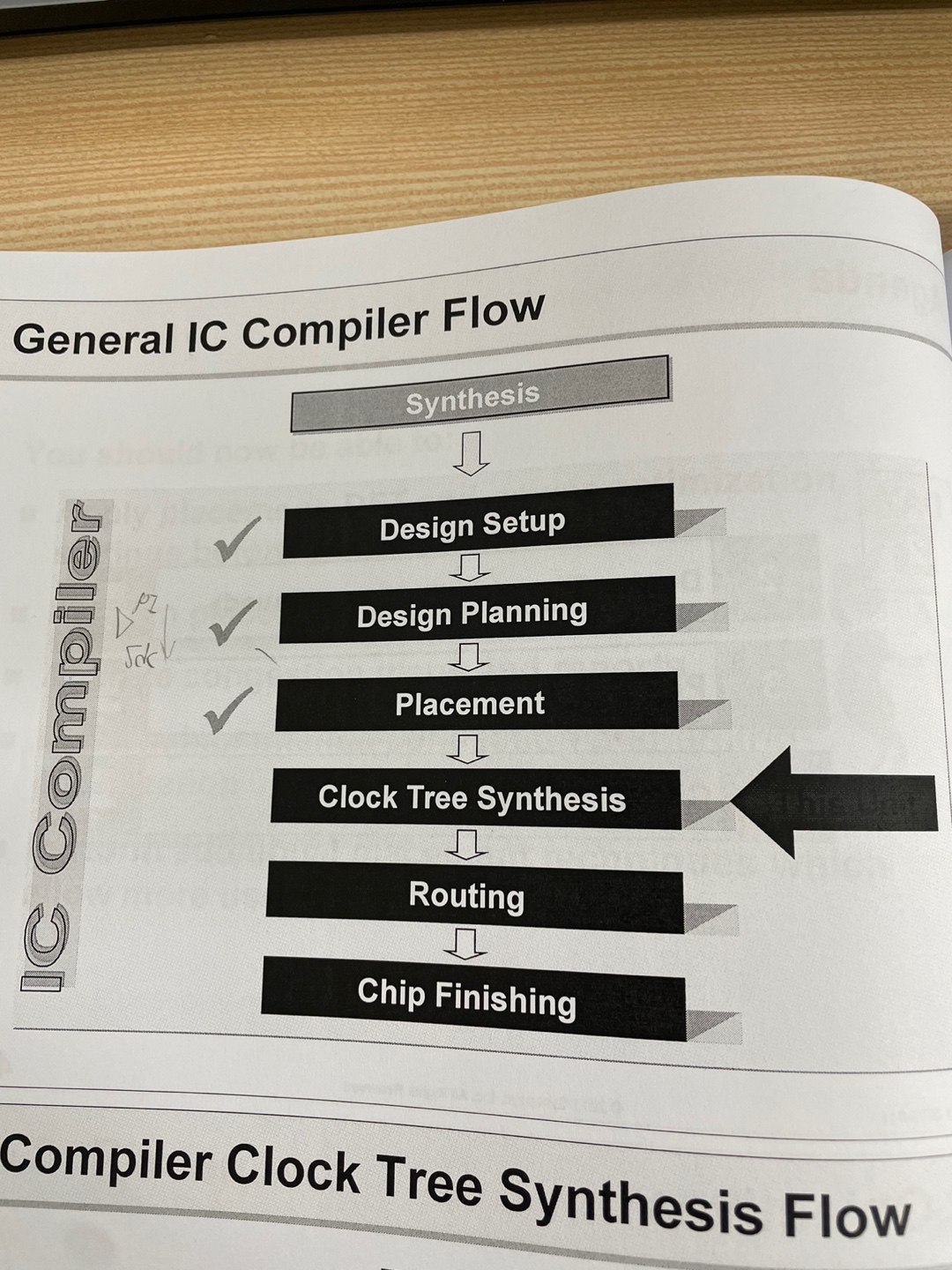

4. Clock Tree Synthesis

Design Status Prior to CTS

: CTS 전 check 사항

- Placement - completed

- Power and ground nets - prerouted : power plan을 했는지

- Estimated congestion - acceptable : placement할 때 congestion 잘 해결했는지

- Estimated setup timing - acceptable

- Estimated max cap/transition - no violations : 공정사에서 정해준 거 초과한 건 아닌지

- High fanout nets

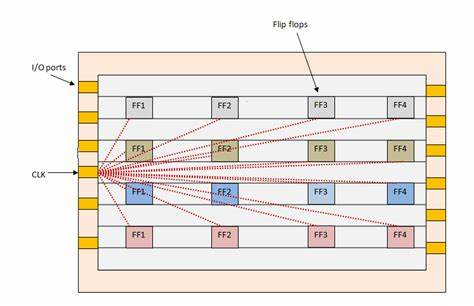

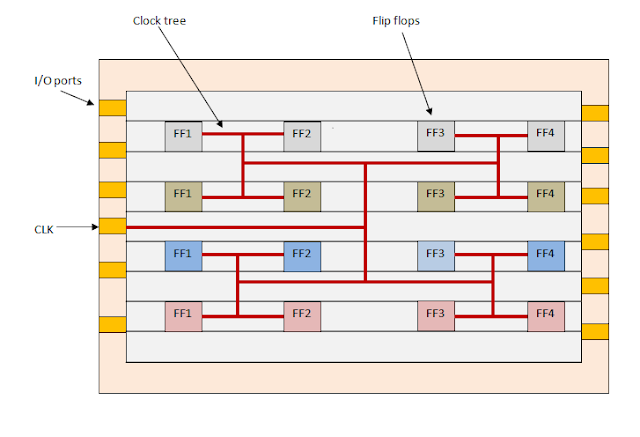

CTS 하기 전 vs 이후

- before CTS

엄청난 skew 발생

- after CTS

버퍼를 넣어 해결할 거면 common point에 넣어 효율 증대

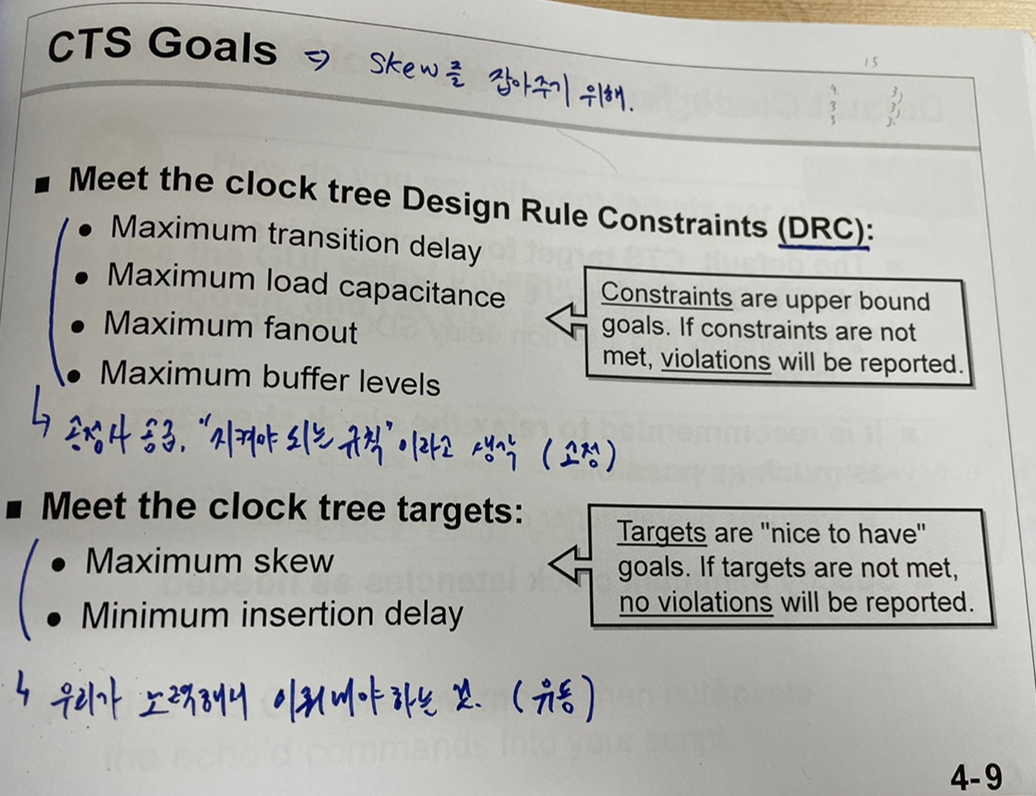

CTS의 목표 : 동일한 클록 신호가 각 단말 노드에 최대한 동시에 도착하도록 하는 것 (Skew를 잡아줌)

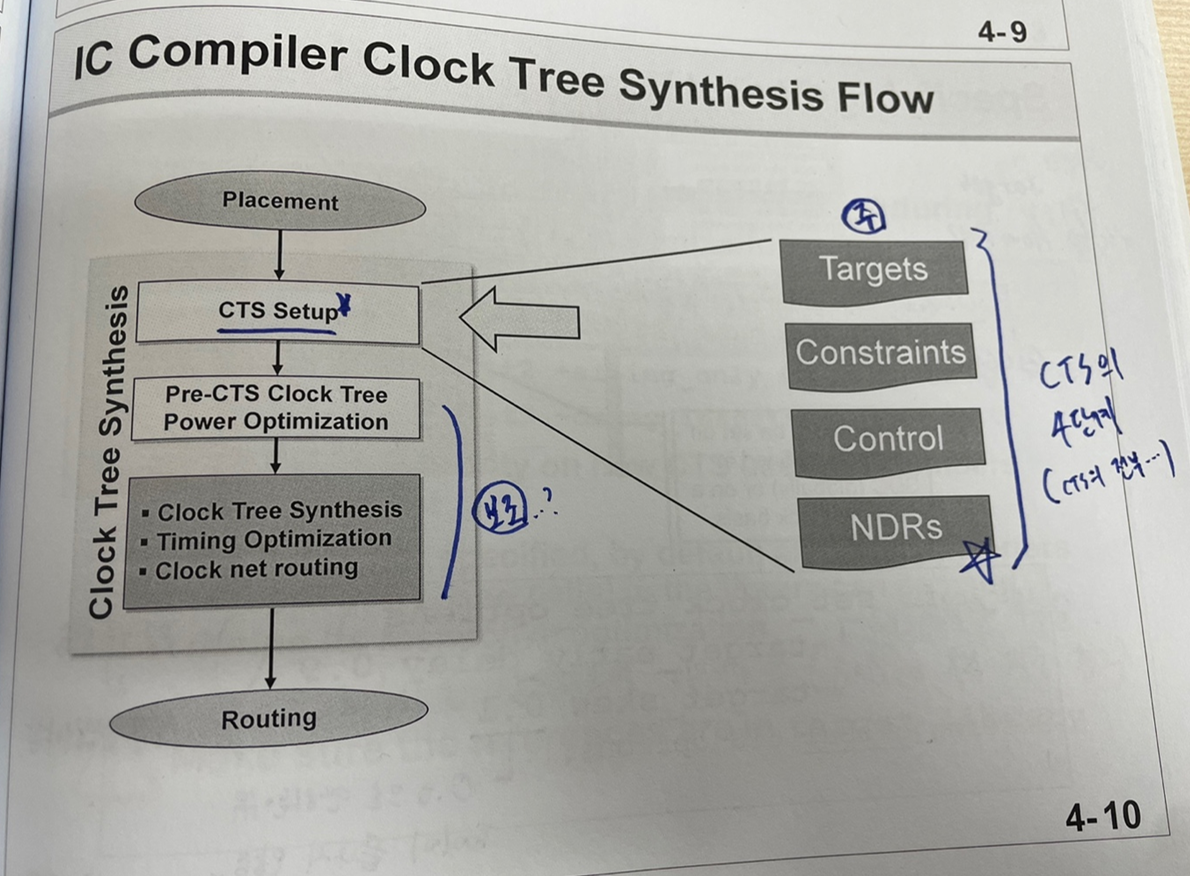

4.1 CTS Setup

[CTS Setup]

- Target

- Constraints

- Control

- NDRs

4.1.1 Targets

skew를 0ns로 맞추자

그럼 어떻게 target을 지정할까?

방식은 1. 윈도우 2. cmd로 정할 수 있음

icc_shell> set_clock_tree_options -target_early_delay 0.9 -target_skew 0.1

1.skew가 0.1로 허용치를 준 이유는 0.0은 ideal값이기에 0.0을 만들라면 tool의 계산이 끝나지 않음

그래서 target_skew의 허용치를 잡는 것은 회로를 보고 판단하는 엔지니어의 경험

+클럭마다 지정이 가능함

+어떤 버퍼를 넣을 수 있는지 설정 가능

만일 list를 안 정해주면 아무거나 씀

4.1.2 Constraints

"PI에서 준 SDC를 확인하라!"

PT에서 사용한 가상의 skew값은 지우고 실제 skew로 재야 함

PI에서 준 SDC 파일에는 set_clock_uncertainty -setup 이 들어가 있음

remove_clock_uncertainty [all_clocks] : 가상 skew값 지우는 방법

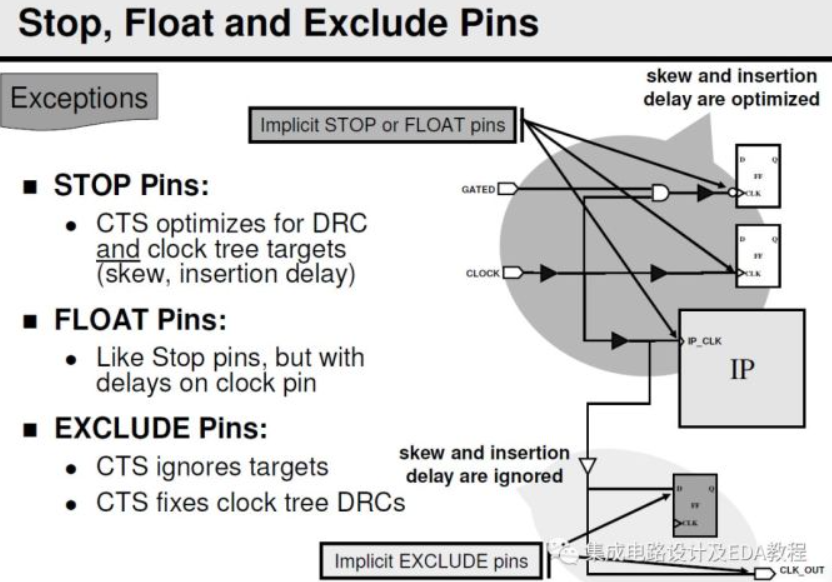

4.1.3 Control

Stop pin

: 지연 균형을 맞추는 데 사용되는 클록 트리의 끝점입니다. 클록 트리 합성 중에 ICC는 정지 핀을 사용하여 설계 규칙 제약 조건과 클록 트리 타이밍( 스큐 및 삽입 지연)을 계산 하고 최적화함

sink pin이라고도 함

- 포트 > 레지스터 clk pin

Float pin

IP 안의 레지스터까지 재야함

Exclude pin

무시하는 pin

Generated and Gated Clock은 CTS에서 무시? 넘어가도 됨

왜냐면 skew는 globally하게 적용하기에 end 점을 DATA FF의 clk으로 잡고 skew 재는 것이 중요

set_clock_tree_exception -exclude_pins [get_pins FFD/CLK]

: exclude path 지정

4-22

Master clock이 다르기에 CTS 따로

문제) WNS가 (-)값

해결) Group화 : 묶어서

4-23

불완전한 solution

4-24

CTS를 해봐야지 문제가 보임

그렇기에 CTS 이후 문제를 계속해서 파악하는 것도 중요

4-26 IP 안의 레이턴시는 알 수 없음

해결방법) 공정사에서 timing을 알려줌 / float_pin으로 IP 내부 설정

-

Explict_stop_pin 정의

set_clock_tree_exception -stop_pins [get_pins IP/IP_CLK]

-

Explict_float_pin 정의

set_clock_tree_exception -float_pins IP/IP_CLK -float_pin_max_delay_rise 0.15

+추가자료

//4-29,30

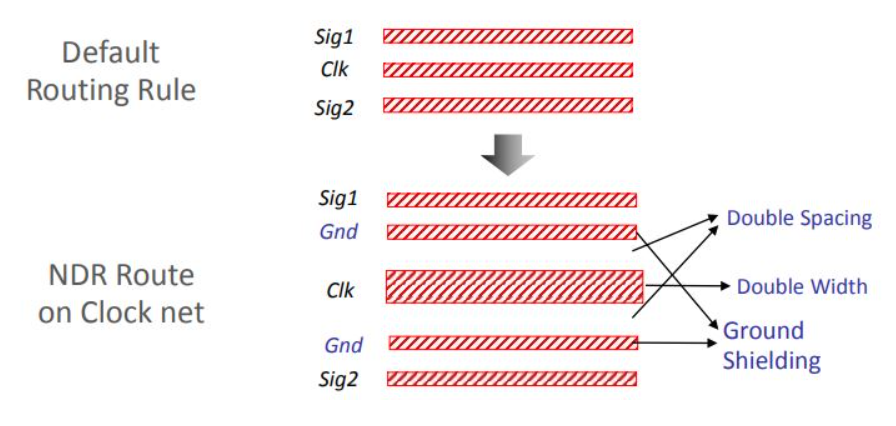

4.1.4 NDRs

NDRs(Non-Default Routing Rules)

실제로 CLK 2ns이면 굉장히 민감(toggle도 많고)

Cross-talk을 막기 위해 NDRs를 함

Cross-talk

쉽게 생각해서 옆집 소음(talk)가 들린다 라는 의미로 해석하면 좋음

크로스톡(Cross-talk)은 전자 회로 설계에서 중요한 개념 중 하나로, 신호가 인접한 회로 경로나 케이블 등을 통해 다른 신호에 영향을 미치는 현상을 나타냅니다. 주로 인접한 신호 경로 사이에서 전기적 또는 전자기적 상호작용이 발생할 때 나타나며, 이는 회로의 동작에 부정적인 영향을 미칠 수 있습니다.

- 전기적 크로스톡 (Electrical Cross-talk):

인접한 전선이나 트레이스로부터 전자기적인 영향을 받아 발생합니다.

주로 고주파 회로에서 발생하며, 전기적 신호가 서로에게 간섭을 일으킬 수 있습니다.

주로 높은 주파수에서 발생하는데, 빠르게 전환되는 디지털 신호에서 더 크게 나타날 수 있습니다.- 자기적 크로스톡 (Magnetic Cross-talk):

인접한 전선이나 트레이스에 흐르는 전류로 인해 발생하는 자기적인 영향을 나타냅니다.

주로 저주파 회로에서 발생하며, 자기적인 결합으로 인해 회로 간의 상호작용이 발생합니다.크로스톡은 다양한 부정적인 영향을 일으킬 수 있음

- 노이즈 발생: 크로스톡은 인접한 신호에 노이즈를 추가할 수 있습니다.

- 신호 왜곡: 크로스톡으로 인해 신호의 형태가 왜곡될 수 있습니다.

- 타이밍 문제: 고주파 신호의 경우, 크로스톡으로 인해 신호의 도착 시간이 불안정해지고 타이밍 문제가 발생할 수 있습니다.

크로스톡 문제를 해결하기 위해 디자이너는 다양한 기술과 방법을 사용합니다. 이에는 물리적인 레이아웃의 최적화, 적절한 신호 간격, 그리고 크로스톡을 감소시키는 회로 설계 기술 등이 포함됩니다.

보통 double-spacing, double-width, shiedling로 함

(신호 2배로 키우고, 굵기 2배, clk net 주변 gnd 깔기)

Tech File의 규칙에 맞게 NDR 설정 중요

NDR 규칙 적용하기 :

define_routing_rule MY_ROUTE_RULES -widths {M3 0.4 M4 0.4 M5 0.8} -spacings {M3 0.42 M4 0.63 M5 0.82}

CLK에 routing rule 적용하기 :

set_clock_tree_options -clock_tree clk /

-routing_rule MY_ROUTE_RULES /

-layer_list "M3 M5"

Tool한테 NDR을 정의하고 RULE을 적용함

NDR 권장사항

double width, spacing 사용하기

double via insertion 고려하기(저항 줄이기)

클럭싱크 피하기 (*클럭싱크란 특정 지역에서 신호 흡수? 정도로 생각)

여기까지 CTS Setup 끄읕!!!

4.2 Clock Tree Power Optimization Pre-CTS

책에선 한장으로 간소화 되어있지만(icc1기준)

현재 실무에서는 칩이 작아지면서 Power쪽이 정말 중요해짐 ICC2에서 자세히 다룰 예정

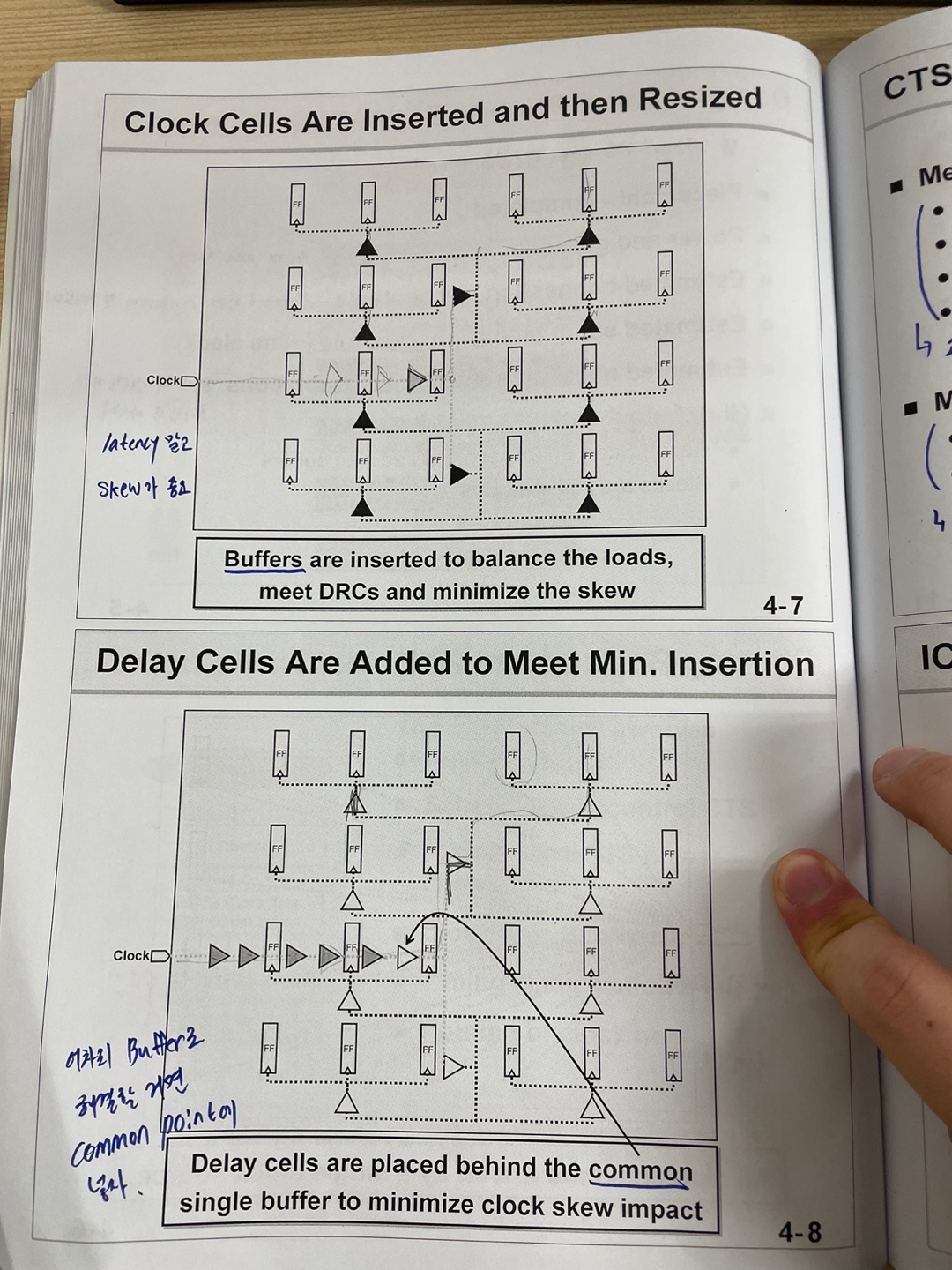

4.3.1 Clock Tree Synthesis

CTS가 하는 일 (Clock_opt를 통해서)

- Synthesis and balancing of individual clock tree networks

- Timing and DRC optimization of non-clock logic

- Routing of clock tree network

[간단 요약]

- 개별 클럭 트리 네트워크의 통합 및 균형 조절:

각 클럭 트리 네트워크의 요소를 조절하여 전체적인 균형을 유지하고, 네트워크 간의 통합을 최적화합니다. 이렇게 하면 클럭이 전체 회로에 고르게 전파되고, 타이밍 문제를 최소화할 수 있습니다.- non-클럭 로직의 타이밍 및 DRC 최적화:

클럭과 관련 없는 로직 부분에서 발생하는 타이밍 문제와 DRC(Design Rule Check)를 최적화합니다. 이로써 non-클럭 부분도 안정적으로 동작하며, 설계 규칙을 준수하게 됩니다.- 클럭 트리 네트워크의 라우팅:

클럭 신호를 안정적으로 분배하기 위해 클럭 트리 네트워크의 라우팅을 수행합니다. 이는 효율적이고 안정적인 클럭 신호 전달을 보장하며, 전체 회로의 성능을 향상시킵니다.

수행을 위한 추가 옵션

- Inter-clock delay balancing

- Scan-chain re-ordering : CTS 진행하면서 Logic 배치 바뀜 (3-19,20)

- Power optimization

등등

//추가자료

스캔 체인은 테스트용 설계에 사용되는 기술입니다. 그 목적은 IC의 모든 플립플롭을 구성하고 관찰하는 쉬운 방법을 제공하여 테스트를 용이하게 하는 것입니다. 스캐닝의 기본 구조에는 스캐닝 메커니즘을 제어하고 관찰하기 위한 다음 신호 세트가 포함됩니다.

CTS 할 때 추천 방법 (in 실무)

- clock_opt

- clock_opt -only_psyn -no_clock_route : timing이랑 DRC 집중해서 최적화

+요즘은 복잡해서 GUI, TEXT가 아닌 리포트로 확인함