SYNOPSYS (PT&ICC)

1.Linux 기초 - MobaXterm

Linux 기초 Linux : 운영체제 사용 이유 : Tool 사용을 위해 mobaxterm으로 접속 기본 명령어 pwd : 현재 작업 하고 있는 디렉토리의 경로명 출력 cd : 현재 작업 디렉토리에서 다른 디렉토리로 이동할 때 사용 (절대 경로 및 상대 경로로

2.SYNOPSYS DAY1

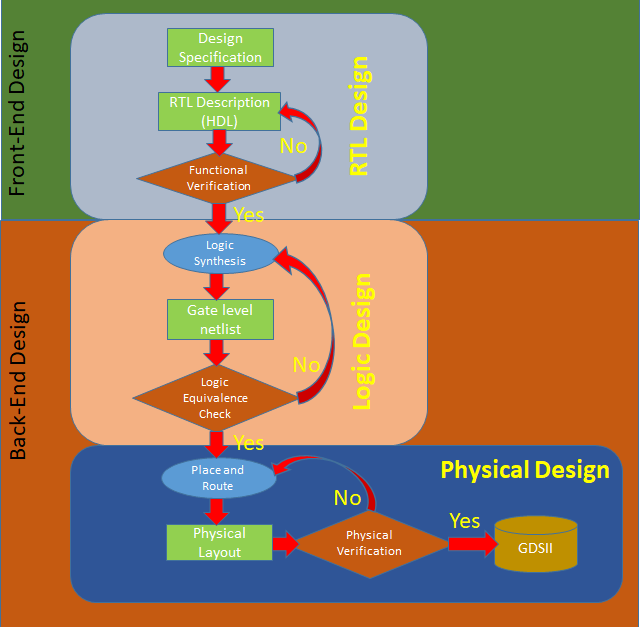

시스템 반도체(SoC) : SoC's combine a processing core, memory, and logic on a single chip 아날로그, 디지털로 나눠짐 디지털 SOC 설계 과정이 수업의 주요 내용임. 주요 내용 : Back-end (P&R)

3.SYNOPSYS DAY2

Hold clk latency : 자체 skew : clk latency 간의 차이 //1-12 hold : DATA 보낼 때 걸리는 시간. 즉, 보내기 위한 지연시간 hold violate : 늦게 올 데이터가 일찍올 때 전 데이터와 충돌됨 prime time

4.추가실습 DAY2

hold 이지만 다 rising edge로 되어있음//예외 경우를 보여줌library hold time의 차이때문에 ff이 들어가도 dat가 작아졌지만 slack은 met

5. SYNOPSYS DAY3

//3-8FF = 레지스터 = 스케셜 디바이스 : 클럭이 들어간 deviceFF의 D는 입력이지만 path입장에서 end point위의 그림에서는 ABCD - start point, FF1_D FF2_D - end pointSlack이 제일 나쁜 거 >> report

6.SYNOPSYS DAY4

시스템 반도체 칩을 만드는데 검증을 빠르고 정확하게그때 필요한 TOOL이 검증된 TOOL >> Golden , Signoff ( 공정 툴, 시놉시스 툴)회로 설계에서 제일 중요한 거 FF(데이터 주고 받기)그 다음 setup hold//4-14문제 : min pulse

7.SYNOPSYS DAY5

//6-8FF은 clk을 기준으로 data를 전달하고 전달 받음clock network = clock tree레이턴시 = 클럭 network에서 걸리는 딜레이CTS = clock만 routing 함set_clock_latency 1 get_clocks Clk : P&R

8.SYNOPSYS DAY6

PrimaryGeneratedVirtualprimary clock : 실제 FF에 들어가는 클럭. 즉, 오실레이터create_clock -period 4 get_ports Clk : 주 clock은 tool에다가 알려주는 command왜냐면 회로 밖에 있기에 PT에 직

9.SYNOPSYS DAY7

Prime Time 사용(기본 설정)칩을 만들 때 환경에 대해서도 생각을 해줌PVT(프로세스 볼티지 템퍼러쳐) 고려해서 칩을 만듦그럼 OCV와 무슨 관계냐?chip 내부에 대해서 알셀을 지날 때 마다 전력이 사용되어 전압이 떨어짐 : IR DROP >> 설계자는 이걸

10.SYNOPSYS DAY8

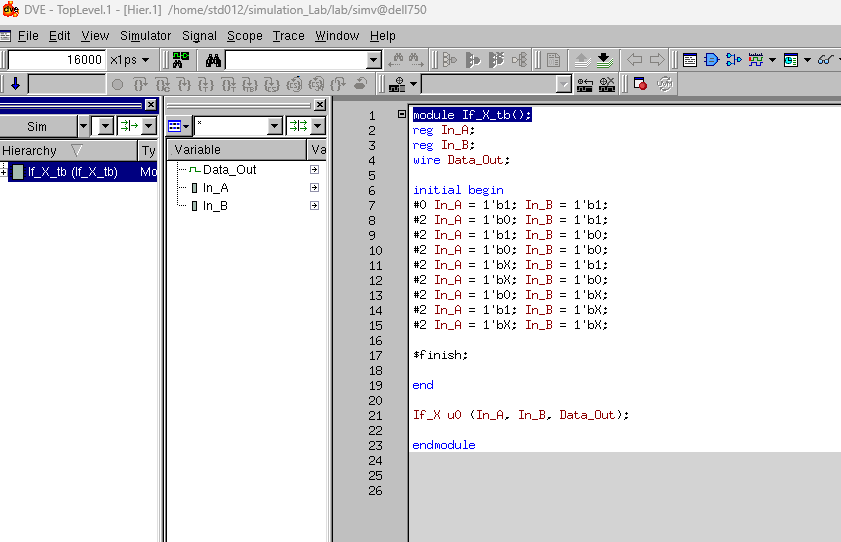

RTL : verilog를 가지고 code를 작성함관련 Tool : Verilog-HDLVerification : code가 목적에 맞게 잘 작동하는지 확인. 즉, 시뮬레이션관련 Tool : VCS, VerdiSynthesis(합성) : 디지털 설계에서 RTL 설계를

11.SYNOPSYS DAY9

lab7 lab7 simulation과 synthesis의 불일치가 일어나는 지 확인 lab8 lab8 simulation과 synthesis의 불일치가 일어나는 지 확인

9. Debugging Constraint Issues 9.16.17) Master Clock(Primary) 찾기 > getattribute [getpins F2/CLK] clocks report_cell F2 제약조건에서 Master Clock이 중요함 위의 2가

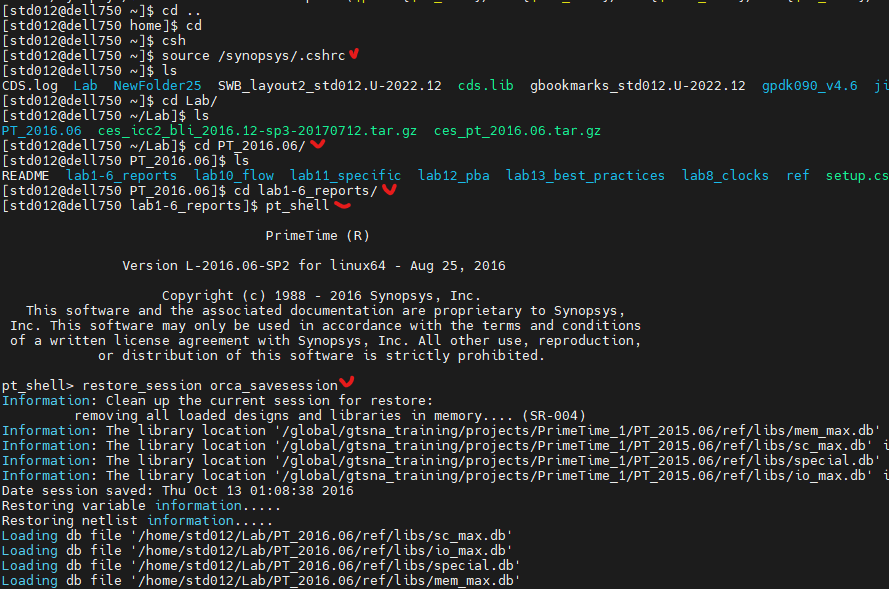

13.SYNOPSYS DAY11(PT)

11. Analyzing Four Specific Situations Latch based analysis [Default = Old] >1번 상황일 때는 0으로 떨어질 때 같이 데이터가 출력됨 2번 상활일 때는 data가 들어올 때 FF의 edge처럼 동작 D>Q

14.SYNOPSYS DAY12(ICC)

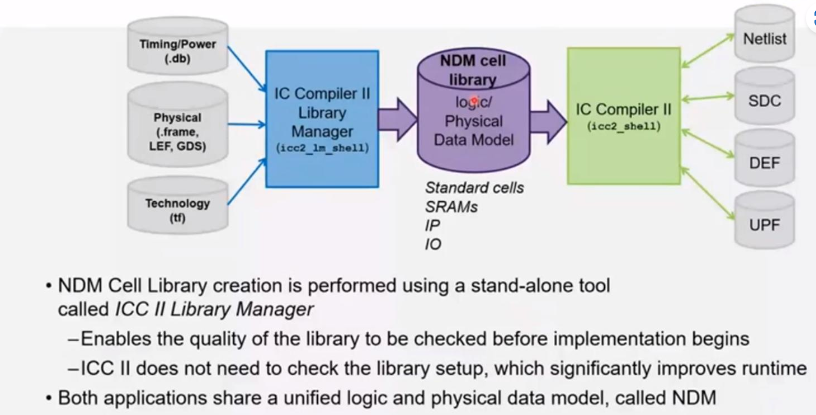

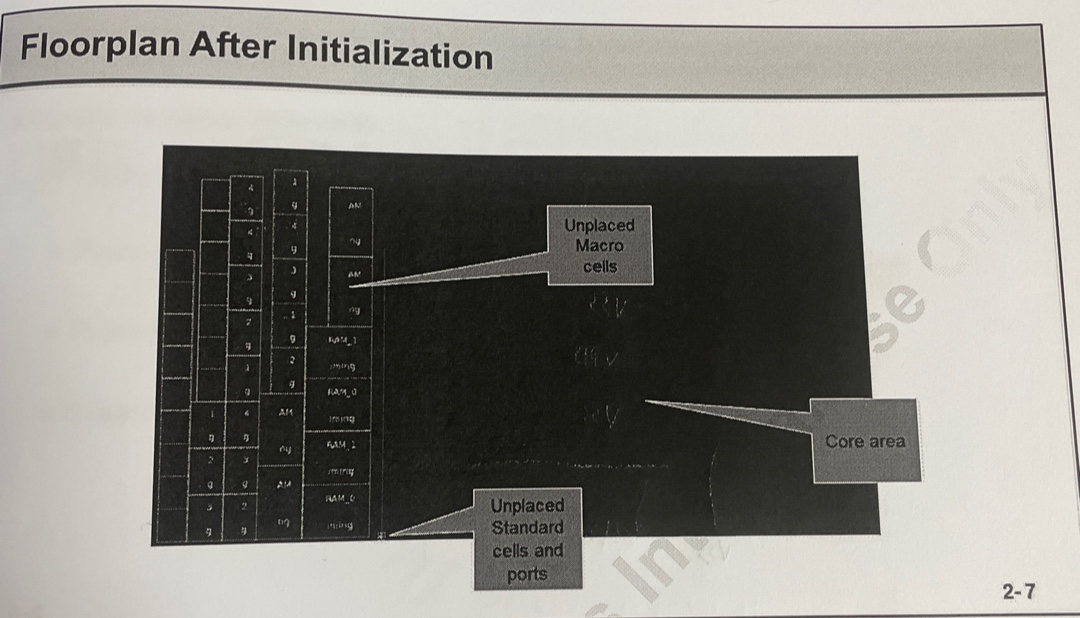

Synthsis DataLogic/timing library files : 공정사 공급Constraints File (orca.sdc) : Front-End 공급GLN : Design Compiler의 결과물Physical DataPhysical Lib Director

15.SYNOPSYS DAY13(ICC)

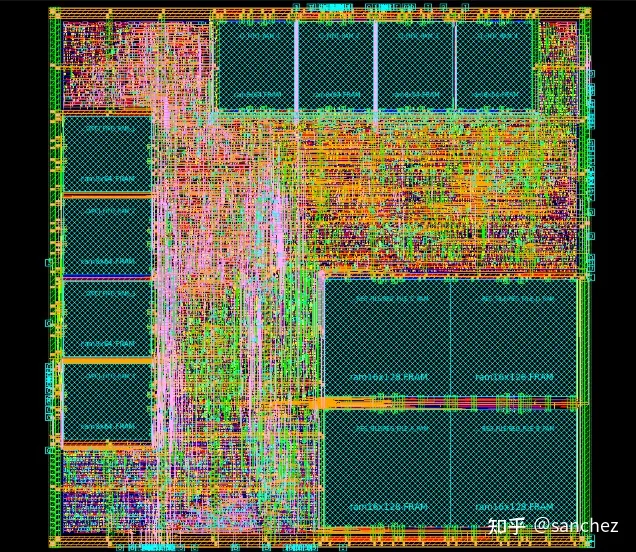

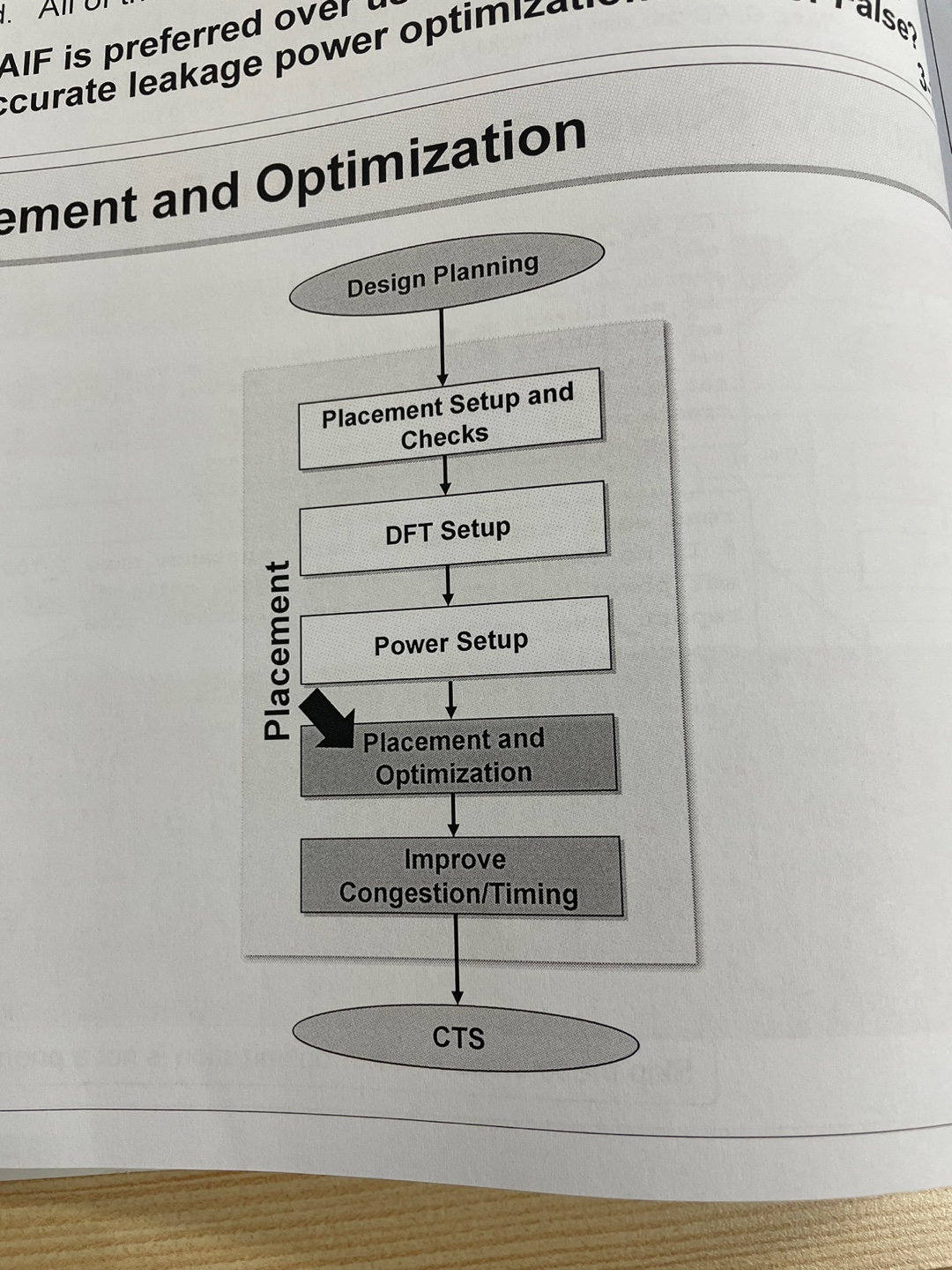

2. Design Planning Create starting floorplan 끝난 이후 다음 단계 진행 2.2 Virtual flat placement 2.2.1 Set placement strategy parameters 배치 전략을 짜는 것은 마크로셀을 어떻게

16.SYNOPSYS DAY14(ICC)

3-37 알아두는게 좋다.Placement해보고 Congestion or Setup Violation 문제가 있으면 Option을 바꾼다.그리고 문제를 해결하면 Route 단계에서 Congestion을 해결한다는 방안이 있는데 좋지는 않음.Route에서 문제를 해결할

17.SYNOPSYS DAY15(ICC)

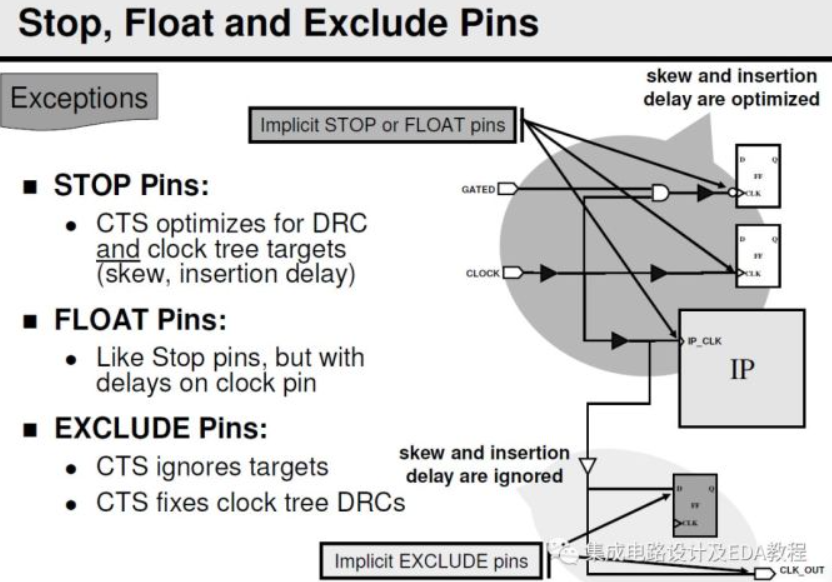

4. Clock Tree Synthesis Design Status Prior to CTS : CTS 전 check 사항 > Placement - completed Power and ground nets - prerouted : power plan을 했는지 Estim

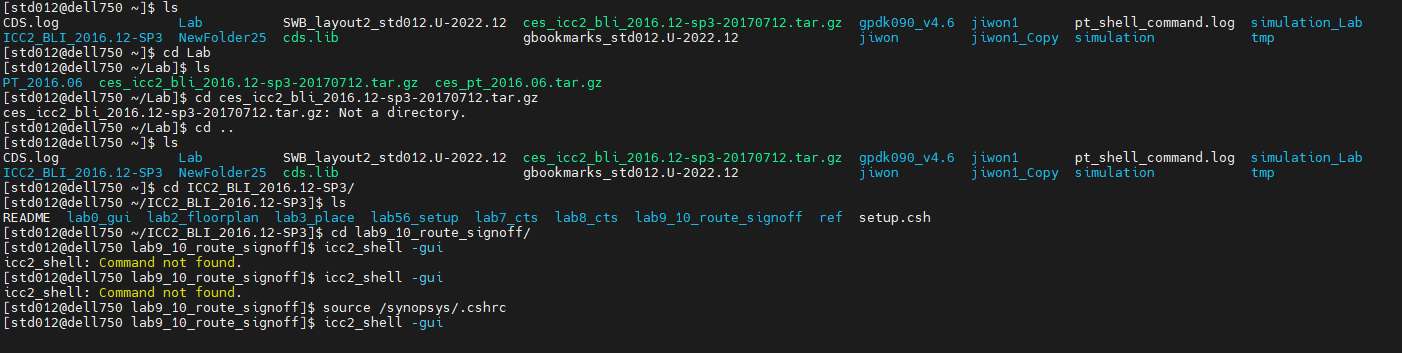

18.SYNOPSYS DAY17(ICC2)

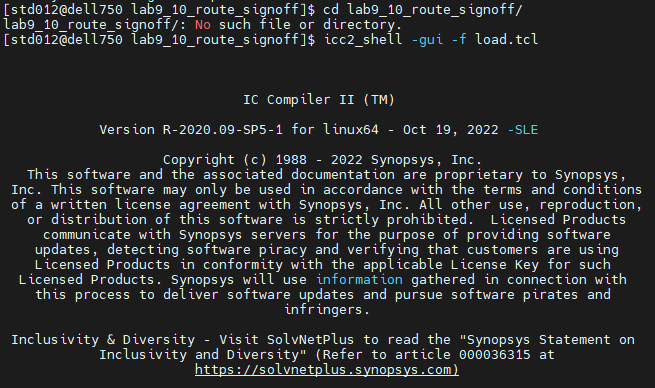

1. NDM Reference Libraries >### NDM : ICC2가 읽을 수 있게 logic lib, psysical lib을 합치는 파일 (=icc에서 miliyway랑 비슷한 형식이라고 생각하면 됨) NDM 을 만들라면 뭐가 필요한지 > #### R

19.SYNOPSYS DAY17(icc2-실습)

Q) What is the default value of the search_path application variable? : search_path 응용 프로그램 변수의 기본값은 무엇입니까? A) 현재 디렉토리 Q) which commands in tcl wi

20.SYNOPSYS DAY18(icc2)

분석과 최적화를 위해 요구된 corner, mode, scenario 정의OCV 적용Tool에 읽혀질 만한지(셋업이 완벽한지) 확인 >> cell 만 불러온 상태에서 에러가 나타나면 안됨!corner : 라이브러리에 있음 (PVT)mode : sdc(PI에서 주는 타이

21.SYNOPSYS DAY19(ICC2)

22.2/21 실습

라우팅하기에 타이밍 괜찮아 보임(setup은 굿 hold는 약간 vio가 있지만 무시해도됨)교재 run.tcl 파일에 안테나 관련 파일 주소가 적혀있어 그걸 불러 읽어와야 함현재 via opt 알고리즘 3가지중tcl파일에서 확인해보면post-route via optim