Verilog?

C언어 기반이지만 하드웨어적 특성이 추가되어 표현력을 높혔다. 이로 인해 광범위한 기술능력을 가진 하드웨어, 트랜지스터 등 설계가 가능하다.

Verilog에서 데이터를 저장하는데 사용하는 2가지 변수는

Wire와reg2가지이다. 하지만 2가지는 다르다!

reg>>

Reg는 data를 저장하기 위한 변수로 다음 값이 할당되기 전까지 현재 값을 유지하므로 procedural assignment를 구현할 때 사용된다. Initial/always block 구문 내에서 출력으로는 반드시 reg를 사용해야 한다. Combinational logic과 sequential logic을 구현할 때 모두 사용 가능하다. 하지만 reg를 사용하여 combinational logic(절차적 할당(always문 등)을 사용한 CL)을 구현하면 현재 값을 유지할 필요가 없기 때문에 wire처럼 합성된다.

wire>>

Wire는 그 단어 그대로 물리적인 연결선이다. Continuous assignment(연속적인 할당)의 출력을 연결하기 위해 사용된다. 즉, continuous assignment의 대표적인 구문인 assign문에서 사용되며 combinational logic을 설계할 때 사용된다. Wire를 통해 gate와 module을 서로 연결하며 신호가 저장되지 않는다.

※ reg과 register는 같은 말이다?

reg와 register의 개념이 동일한 것은 아니다. reg라는 자료형을 사용하여 register의 역할을 하는 logic을 하드웨어로 구현하는 것으로 이해함이 적절하다

Verilog HDL은 3가지 verilog 모델들이 존재한다.

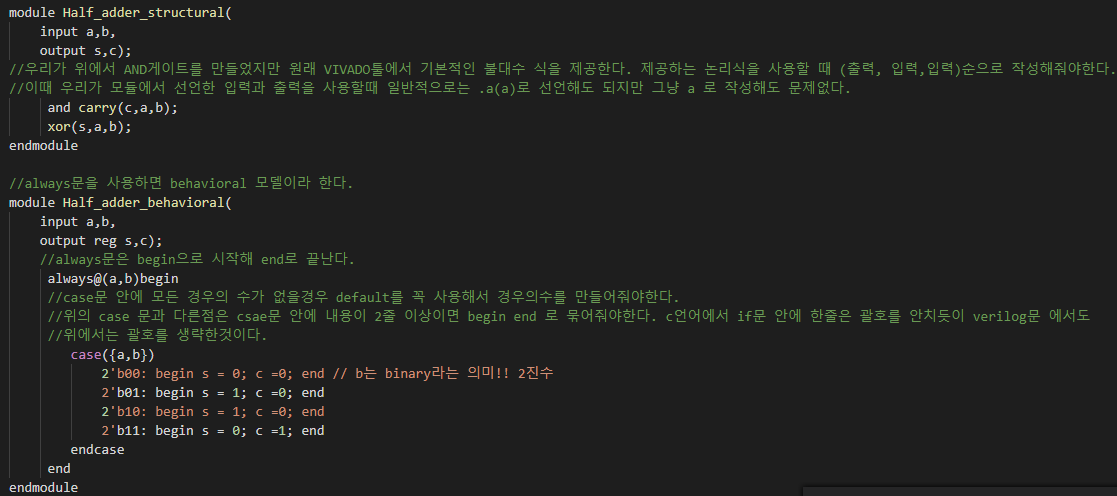

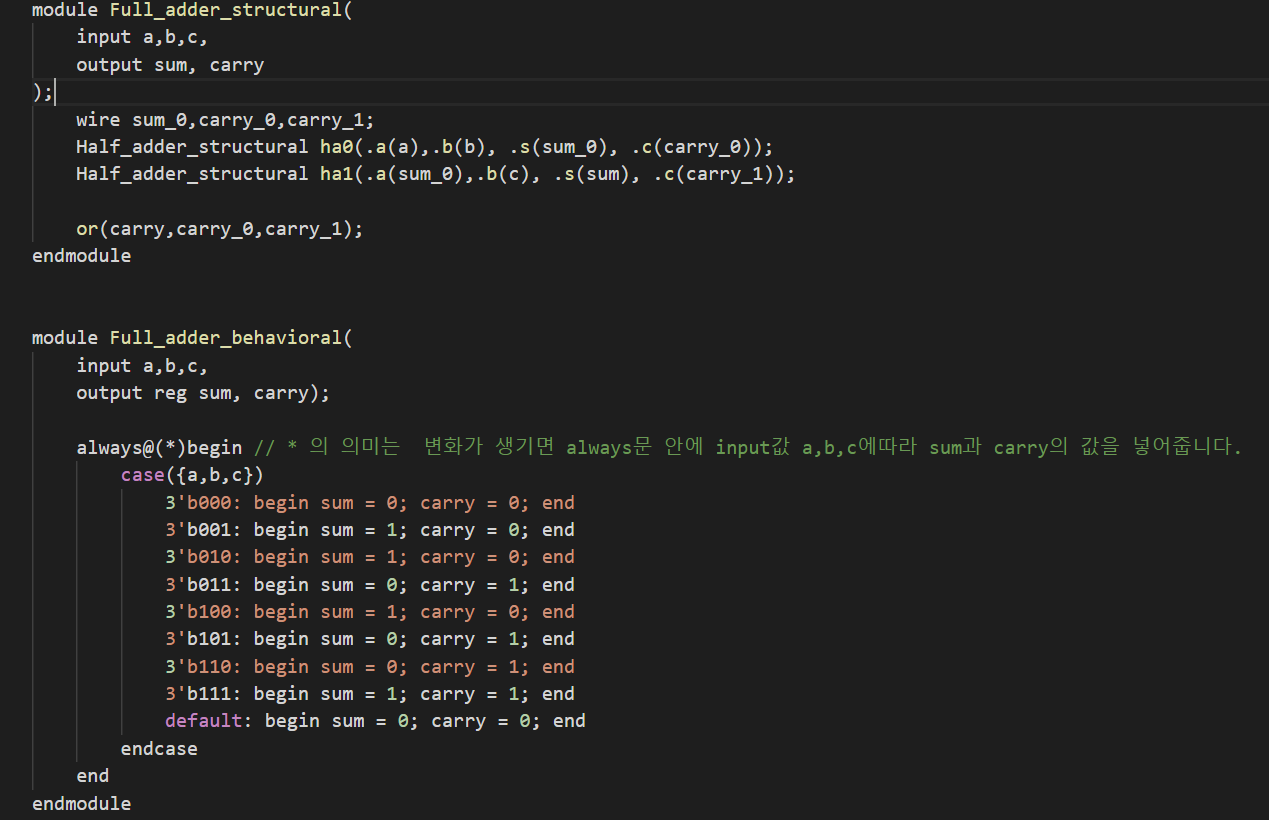

1.동작적 모델(behavior) :

어떤 특정한 구조나 기술을 나타내지 않는 상위 추상화 레벨에서 회로나 시스템을 표현. 매우 중요한 회로이거나, 이를 블록으로 표현해서 보여줄 때, 이 모델로 코딩한다. 동작적 구조로 모델링하면 구조는 알기 어렵고, 동작만 알 수 있다._always 문을 사용해 입력에 대한 동작들을 정의한다. (always문의 output은 reg로 선언.)_-> C 언어 처럼 구체적인 회로구성에 대해 신경쓰지 않고 기술하는 모델.

2.구조적 모델(structural) :

사용된 컴포넌트 간의 상호 연결구조가 분명히 기술되는 레벨. 특정 라이브러리/패키지의 개별 게이트나 플리플롭의 사용을 지정할 수 있을 정도로 자세하다(동작적 모델보다 하위 추성화 레벨)상호 연결구조를 모두 정의해줘야하므로 코드가 길어진다.

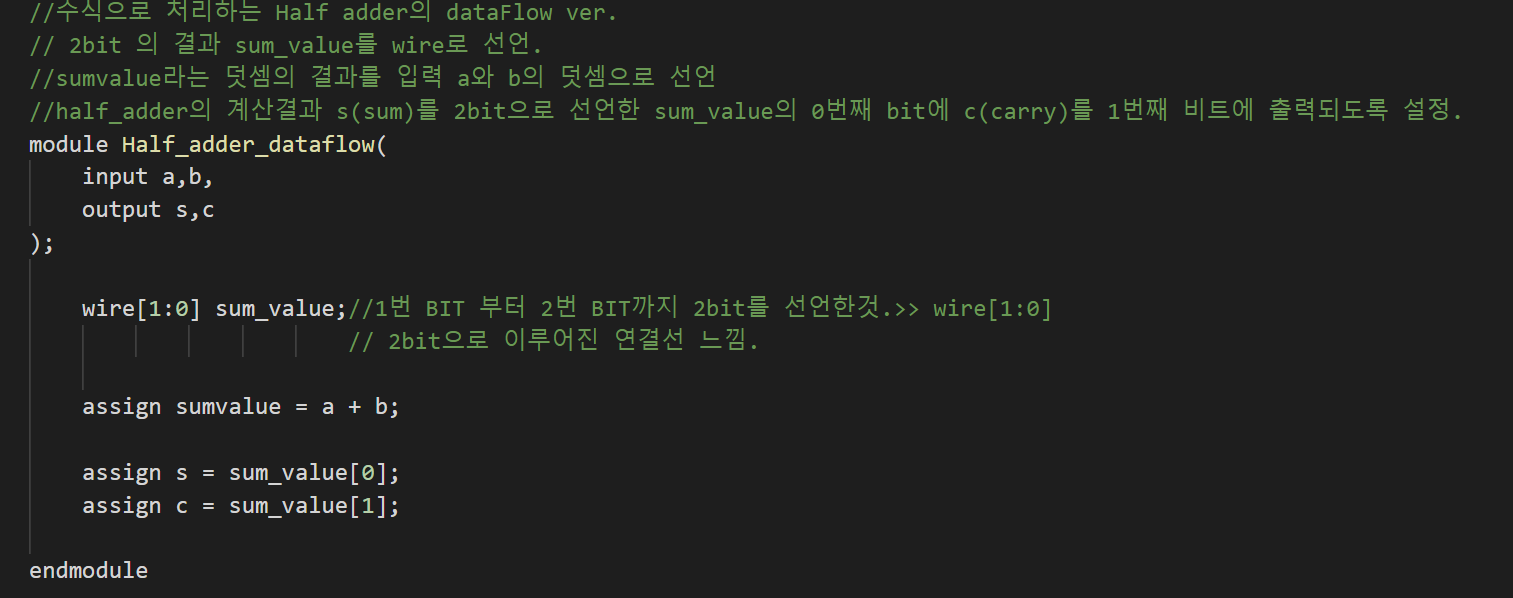

3.데이터 흐름 모델(data flow(RTL)) :

RTL은 레지스터 전송 언어라고 한다. 이는 동기 시스템의 동작을 기술하기 위해 수십 년간 사용돼왔다. data Flow에서는 데이터들의 경로와 제어 신호를 명시한다. wire를 사용해 데이터들의 경로와 선들을 정의해 연결되어 수행되는 기능들을 선언과 정의해준다. -> 각 신호 or 데이터가 어떻게 변환되고 다른 요소로 전달되는지에 중점을둡니다. ex. assign 문

Verilog 실습

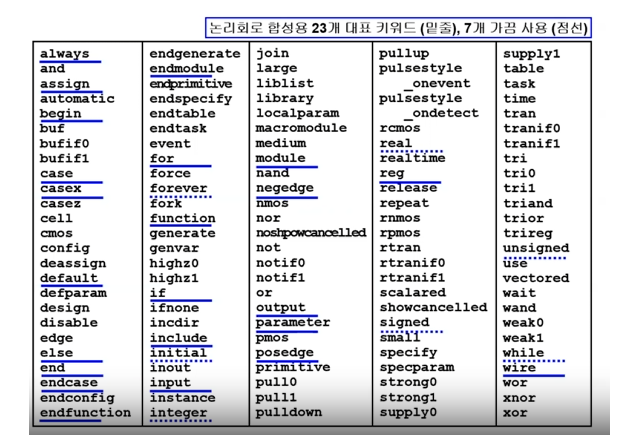

- Verilog에서 제공하는 키워드 리스트

✔ 그 외

- 상수 표현

- d(10진수)- h(16진수)

- b(2진수)

- o(8진수)

- Port

- inout : 반도체 제조 원가 절감을 위해 사용되기도 한다.

모듈 선언시 모듈명 선언후 ()안에 입력과 출력을 선언. 이때 함수식 선언이 아닌 열거식, 컴마로만 이루어져 선언하고 마지막 (); 뒤에 콜론을 찍는다. 모듈 선언이 끝나면 endmodule로 마무리한다. module AND_Gate( output reg q, input a,b ); //일반적인 case문과 다르다. case문은 endcase로 닫는다. always @(a,b)begin case({a,b}) 2'b00: q = 0; 2'b01: q = 0; 2'b10: q = 0; 2'b11: q = 1; endcase end endmodule기본적으로 Module구성은 위와 같이 module로 시작해서 endmodule로 끝난다.

2.기본적인 AND Gate 와 Half Adder 설계

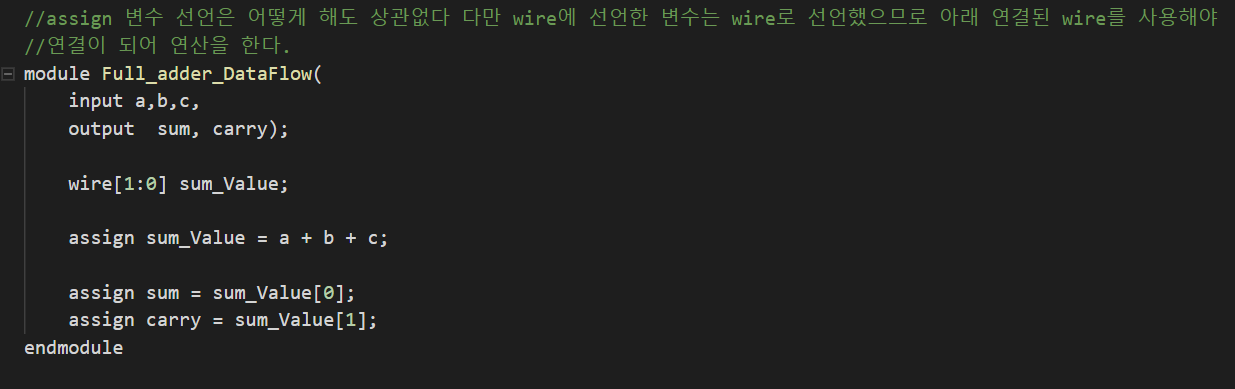

- Half Adder 의 Data flow 모델링

4.Full Adder의 구조적 모델링,동작적 모델링,Data Flow 모델링 및 TestBench

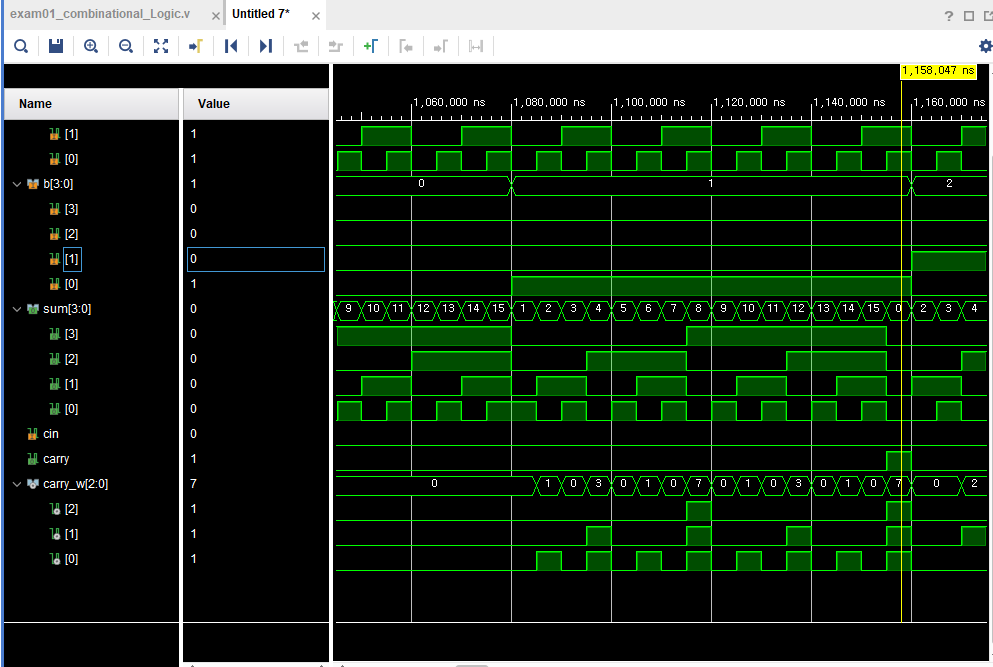

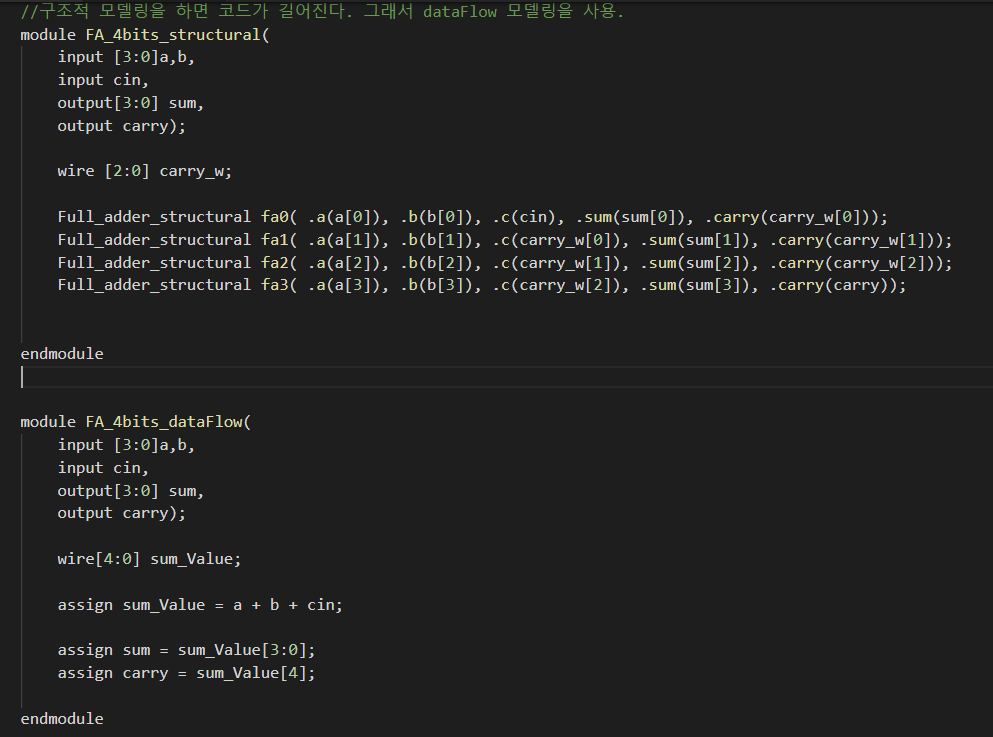

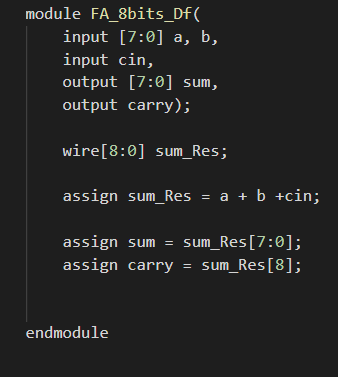

5.4bit Full Adder의 구조적 모델링,동작적 모델링,Data Flow 모델링 및 TestBench

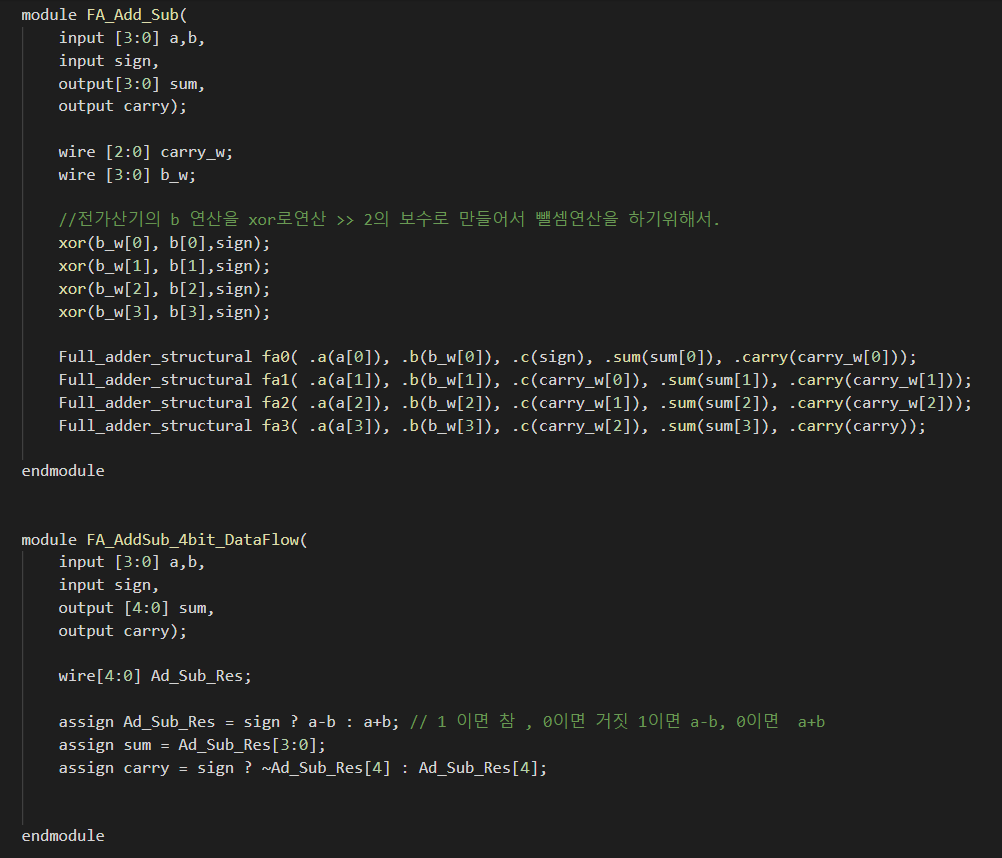

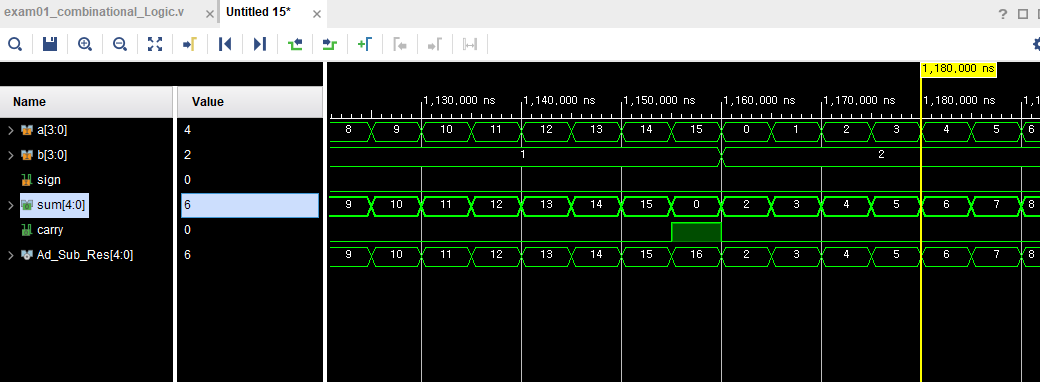

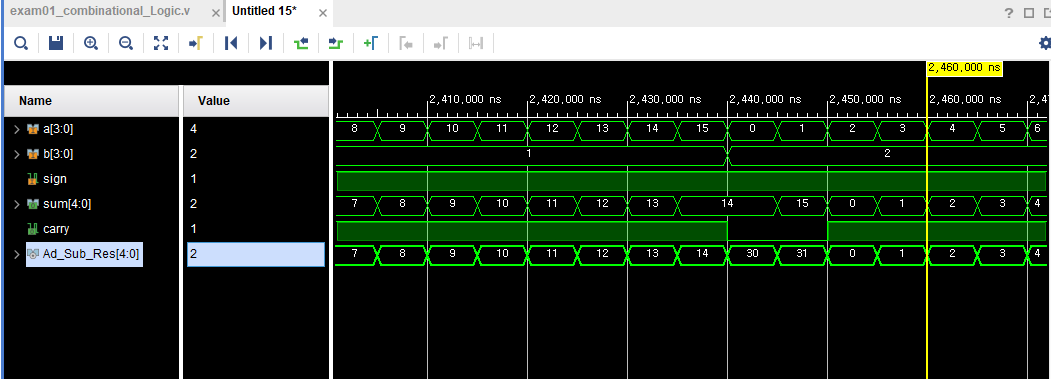

6.FA_감가산기 및 TestBench

2비트 숫자를 반전시키고 +1 을 하면 반전된다. (ex. 0101 (5) => 1010 + 1 = 1011(-5) )

위에서 설명한 내용은 컴퓨터에서 음수를 저장하기 위해 사용하는 방법이다. 4bit 연산을 한다고 하면 0000~ 1111 까지 표현이 가능하다. 양수만 저장한다면 0~15까지 저장이 가능하다! (이때 1000 은 "8" 이라고 둔다) 만약 16개 중 절반은 음수로 할당한다면? 1000은 -8로 둘 수 있다.

★이는 맨앞에 비트가 1이면 음수 0이면 양수이다.★

0111(7)고 1001(-7)을 덧셈연산을 하면 10000이 된다.

0100(4)와 1100(-4를 더해도 10000이다 즉, 전부 10000인 셈이다.

두 수를 더하게되면 최대 비트 크기보다 크면서 가장작은 2의 거듭 제곱수가 나온다.

이렇게 생각하자 음수를 생각할때 최상위 비트가 1이고 아래 0이 아니고 1인 비트자리수가 있다면? 만약 1000(-8) => [8:1][4:0][2:0][1:0] 이라면 4비트 이므로 최상위 음의 정수는 -8일 것이다.

1001(-7) => [8:1][4:0][2:0][1:1] > 만약 최상위 1비트가 1이고 하위 비트 중 1인 bit자리가 존재한다면 최상위 음의 정수에서 비트 자리수가 의미하는 정수를 더해준다면 음의 정수가 계산됨.

즉! 현재 첫번째 비트자리가 "1" 이므로 -8에 1을 더해주면 -7이된다

감가산기를 설계할 dataFlow로 설계할 때 뺄셈을 할때 carry가 발생하는것을 주의해야한다.

Dataflow에서는 뺄셈을 했을 때 carry의 비트수가 1이되는 경우가 있다(less의 의미). 이는 연산하는 앞이 더 크거나 작다는 의미이고 carry 비트수가 0이면 (연산하는 앞이 더 작거나 같다는 의미이다.)

즉 a + b 에서

a >= b --> carry = 1, a < b ---> carry = 0