사전지식

PLD : Programmable Logic Device

프로그램이 가능한 전자 퓨즈선으로 연결된 게이트의 배열(array)로 구성된 집적회로.

#디지털 시스템의 설계를 위해 PLD사용.

장점

1. 복잡한 논리회로를 하나의 집적회로로 프로그래밍 할 수 있다.

2. 필요한 소자들의 수와 비용을 절감할 수 있다.

3. 주로 AND , OR 게이트의 배열 구조를 갖는 집적회로이다.

4. 결국 PLD는 논리요소들이 배열 형태로 되어 있어 배열 형태의 내부 연결선을 프로그래밍 할 수 있다.

PLD 내부구조

전자 퓨즈선의 연결 유무에 의해 AND-OR 연산 즉, 곱의 합 형식의 조합논리 회로를 구현.

즉! AND와 OR의 배열 형태로 구성되어있는 것을 PLD라한다.

PLD는 3가지 형태를 갖는다.

1. PROM

2. PLA

3. PAL

ROM

기능: ROM은 데이터나 프로그램 코드를 저장하는 메모리 장치입니다. 주로 컴퓨터 시스템의 기본 입출력 시스템(BIOS)이나 임베디드 시스템의 펌웨어 등에 사용됩니다. 저장된 데이터는 읽기 전용이어서 프로그램 실행에만 사용할 수 있고, 수정할 수는 없습니다.

#동작 방식

제조 과정:

1. ROM은 마스크 프로그래밍 방식으로 제조됩니다.

2. 데이터나 프로그램 코드를 마스크에 인코딩하고, 이를 이용해 실리콘 웨이퍼에 데이터를 기록합니다.

3. 이렇게 기록된 데이터는 ROM 칩에 영구적으로 저장됩니다.

데이터 액세스:

1. CPU가 ROM의 특정 주소를 읽으면, 해당 주소에 저장된 데이터가 CPU로 전송됩니다.

2. ROM은 읽기 전용이므로, 데이터를 수정할 수 없습니다.

특징:

1. 전원이 꺼져도 데이터가 유지되는 비휘발성 메모리입니다.

2. 제조 공정에서 최적화된 상태이므로, 사용자가 직접 수정하기 어렵습니다.

3. 새로운 기능이나 코드를 추가하려면 새로운 ROM 칩을 제작해야 합니다.

※이처럼 ROM은 데이터 저장과 프로그램 실행을 위한 읽기 전용 메모리로, 제조 과정에서 데이터가 영구적으로 기록되는 특징을 가지고 있습니다.

읽기 전용을 위해 존재하는 메모리이다. 쓰기는 오직 한번만 가능하고 후에 읽기만 가능하도록 제작된 메모리!

가장 기본적인 형태는 n 개의 입력 라인을 가진 Rom은 8words X 4-bit ROM이다. 8words는 decoder의 출력을의미한다.이는 ROM에는 decoder가 구성되어있고 입력은 가장먼저 decoder로 들어간다. 예를들어 3개의 입력이들어간다면 decoder는 출력으로 2^n 으로 8개의 출력, 즉 minterm으로 변환한다.

이를 가지고 decoder의 출력신호에 연결된 수직선 즉 ROM의 출력들과 연결되어 ROM의 출력에 신호를 보낸다.ROM은 program 가능한 AND,OR 게이트이다.

즉, SOP form. 이는 제조 공정 중에 마스크 패턴을 이용해 논리 함수를 프로그래밍 하는 것을 의미한다. 이 과정에서 ROM 내부 회로가 SOP형태로 구현된다는 의미. (SOP form이란? AND 게이트의 출력을 OR 게이트로 연결하는 방식으로, 임의의 논리 함수를 표현할 수있다.)

PLA(Programmable logic Arrays)

- 하드웨어적으로 보다 코스트가 적게 만들수 있는 장점이있다.

- ROM의 입력이 많아짐에 따라서 decoder에서 n개의 입력에 따른 수십개의 Full decoder출력이 나오게된다.

- 하지만 실제 사용되는것은 생각보다 많지 않는 문제를 해결하기위해 나온것이 PLA이다.

따라서 PLA는 ROM만큼 flexible하고 random logic에 대해 보다 적은 비용이 들어가며, 주로 control logic에 사용된다.

PLA는 AND array와 OR array로 이루어져 있다. AND array를 decoder대신 이용해서 필요한 부분만 사용한다.

PLA(Programmable Logic Array)의 AND 어레이와 OR 어레이의 연산 과정 ↙

AND 어레이

- AND 어레이는 입력 신호들을 논리 AND 연산하여 중간 결과를 생성합니다.

- 각 행(row)은 하나의 AND 게이트를 나타내며, 입력 신호들이 해당 행의 퓨즈 또는 EPROM 셀에 따라 AND 연산됩니다.

- 이렇게 생성된 중간 결과는 곧 "곱(Product)"이라고 부릅니다.

즉, AND 어레이의 연산 과정은 "곱의 합(Sum of Products)"을 생성하는 것입니다.

OR 어레이

- OR 어레이는 AND 어레이에서 생성된 중간 결과들을 논리 OR 연산하여 최종 출력을 생성합니다.

- 각 열(column)은 하나의 OR 게이트를 나타내며, 중간 결과들이 해당 열의 퓨즈 또는 EPROM 셀에 따라 OR 연산됩니다.

- 이렇게 생성된 최종 출력은 곧 "합(Sum)"이라고 부릅니다.

즉, OR 어레이의 연산 과정은 "합의 곱(Product of Sums)"을 생성하는 것입니다.

★★★ 이처럼 PLA의 AND 어레이와 OR 어레이는 각각 "곱의 합"과 "합의 곱" 연산을 수행하여, 사용자가 원하는 논리 회로를 구현할 수 있게 합니다. 이를 통해 PLA는 ROM에 비해 더 유연하고 효율적인 논리 회로를 구현할 수 있습니다.

-

ROM과 PLA차이

-

구조적 차이

1. ROM에는 Decoder가 포함되어 있지만, PLA에는 AND 어레이와 OR 어레이가 포함되어 있습니다.

2. Decoder는 입력 신호를 이진 주소로 변환하여 특정 메모리 위치를 선택하지만, AND 어레이와 OR 어레이는 입력 신호를 논리 연산하여 출력을 생성합니다.

프로그래밍 방식의 차이:

3. ROM은 제조 시 마스크 패턴을 통해 프로그래밍되므로 변경이 어렵지만, PLA는 퓨즈 또는 EPROM 기반으로 프로그래밍되어 사용자가 직접 프로그래밍할 수 있습니다.

유연성 및 효율성:

4. ROM은 고정된 논리 기능만 수행할 수 있지만, PLA는 AND 어레이와 OR 어레이를 조합하여 다양한 논리 기능을 구현할 수 있어 더 유연합니다.

5. PLA는 입력 및 출력 신호의 수가 많아도 AND 어레이와 OR 어레이의 크기만 늘리면 되므로 효율적입니다. -

면적 및 속도

1. ROM은 Decoder로 인해 면적이 크지만, PLA는 AND 어레이와 OR 어레이로 구성되어 면적이 더 작습니다.

2. ROM은 Decoder로 인해 지연 시간이 길지만, PLA는 병렬 처리가 가능하여 더 빠른 속도를 가집니다.이처럼 PLA는 ROM의 단점을 보완하여 더 유연하고 효율적인 논리 회로를 구현할 수 있습니다. 특히 AND 어레이와 OR 어레이를 통해 다양한 논리 기능을 구현할 수 있다는 점이 PLA의 핵심적인 장점입니다.

-

ROM의 단점

- 제조 과정에서 논리 회로가 이미 고정되어 사용자가 직접 수정하기 어렵다.

- 새로운 기능이나 로직을 추가하려면 새로운 ROM 칩을 제작해야 한다.

PLA 장점

- 프로그래밍이 가능하므로 사용자가 직접 논리 회로를 변경할 수 있다.

- 새로운 기능 추가나 로직 변경이 상대적으로 쉽다.

즉, PLA는 ROM과 같은 기능을 제공하면서도 사용자 정의가 가능하다는 점에서 ROM의 단점을 보완한 메모리 유형이라고 할 수 있습니다.

이처럼 PLA는 ROM의 단점을 극복하고자 개발된 메모리 기술로, 유사한 기능을 제공하면서도 프로그래밍 가능성을 높인 것이 특징입니다.

PAL

- 프로그래밍이 가능한 논리회로를 구현하는 소자이다.

- PAL은 AND array의 입력조합을 프로그래밍하여 회로를 구현할 수 있다.

- 출력 논리는 고정된 OR게이트로 인해 제한적이다.(PAL회로에는 OR게이트가 포함되어있지 않다.)

- PLA와 마찬가지로 프로그래밍은 가능하지만 OR게이트가 고정되어 있어서 AND array의 입력조합만 변경할 수 있고 출력 논리는 변경할 수 없다.

따라서 PAL은 구조가 단순하고 빠른 동작 속도를 가지지만, 유연성이 다소 제한적여서 PLA보다 유연성이 떨어지지만 구조가 단순하여 동작속도는 PLA보다 빠르다.

SL(Sequential Logic Circuit) : 순차 논리회로

- 현재출력이 현재입력뿐 만 아니라 과거의 입 출력 함수를 바탕으로 현재 출력값이 결정되는 회로

특징

- 과거의 입출력 함수를 저장하기 위한 메모리(기억회로)가 필요. 이를 feedBack시스템이라 한다.

- 과거의 정보가 현재 출력에 영향을 준다. -> 즉, 출력은 시간의함수!

- 주어진 입력 x 에 대해서 출력이 unique하지 않다.

동기, 비동기식 시스템- 동기(synchronous) : Clock을 공유하고, 플립플롭들이 같은 시간에 동작.

- 비동기(asynchronous) : clock을 공유하지 않고, 플립플롭들이 각자 동작 해석이 복잡하기 때문에 대부분의 디지털 시스템은 동기 순차회로이다. (latch라고도 부른다.)

- 동기 순차 논리회로 구조 2가지

mealy machine

- 출력 = f(입력,현재상태)

- 다음상태 = f(입력,현재상태)

# mealy machine은 입력이 변할 때, 상태가 변할 때 모두 출력이 변경되므로 통제가 불편

moore machine- 출력 = f(상태)

- 다음상태 = f(입력, 현재상태)

# moore machine은 상태가 변할 때만 출력이 변경된다. 이는 입력과 출력이 직접 연결되지 않아 간단하므로 컴퓨터를 비록한 대부분의 디지털 시스템에서 사용됩니다.

CL VS SL (조합논리회로 VS 순차논리회로)

- CL

- Gate를 사용 : AND, OR, NOT, NAND, NOR, XOR, XNOR..

- MSI Module : MUX, DEMUX, ENCODER, DECODER, PLD, PLA, PAL, ROM ...

- 일반적인 CL설계.

- 값을 저장하지 못한다.

- 클럭을 사용하지 않음

- 입력의 변화가 출력에 바로 반영.

- ex : 가산기, 멀티플렉서(MUX), 디코더, 인코더

- SL

- 메모리 기본소자 사용 : Latch, F/F, CSR, D, JK, T

- MSI Module : Counter, register

- 일반적인 SL설계

- 값을 저장하는 latch, F/F, register(F/F의 모임), 메모리 등의 소자가 있어서 현재 상태를 저장한다.

- 클럭을 사용하여 값을 저장한다.

- 입력이 변화해도 주로 클럭의 edge에서 값이 저장.

- ex : 카운터, 레지스터, 클럭 분배기, FSM

- 기억소자

- Latch

- SR Latch

- D Latch

- F/F

- Edge Trigger D F/F

- SR F/F

- JK F/F

- T F/F

- Master Slave F/F

여기서 중요한점은 Latch와 F/F의 차이는 트리거링(Triggering)의 차이이다.

- 래치(Latch): 클록(Clock) 입력을 갖지 않는 2진 기억소자(쌍안전회로)를 말한다.

플립플롭과 유사하고(기억 및 귀환요소 특성), 클록 입력이 없는 비동기식 순서논리회로 소자이다 여기에서 쌍안정회로란?

- 전기적으로 안정된 두개의 상태 (set, reset)

- 전기적 자극(Trigger)에 의해 하나의 안정상태에서 또 다른 안정상태로 변하는 회로

- 1비트를 저장한다. 입력된 이전의 상태를 기억하기도 하고 몇 개의 논리게이트를 조합해서 구성하기도 합니다.

1. 래치는 레벨 트리거링(Level-Triggered) 방식을 사용합니다.

2. 래치는 입력 신호가 활성 상태(High 또는 Low)인 동안 출력 상태를 유지합니다.

3.입력 신호가 변경되면 출력 상태도 즉시 변경됩니다.- 플립플롭(Flip-Flop): 플립플롭은 논리 게이트의 피드백 루프에 1비트의 정보를 보관 및 유지할 수 있는 기억장치이다. 전기 신호가 지속적으로 공급되어야만 정보를 유지할 수 있는 휘발성 메모리이다.

1.플립플롭은 엣지 트리거링(Edge-Triggered) 방식을 사용합니다.

2. 플립플롭은 입력 신호의 변화(상승 엣지 또는 하강 엣지)에 의해 출력 상태가 변경됩니다.

3. 입력 신호가 활성 상태인 동안에는 출력 상태가 유지됩니다.

Latch

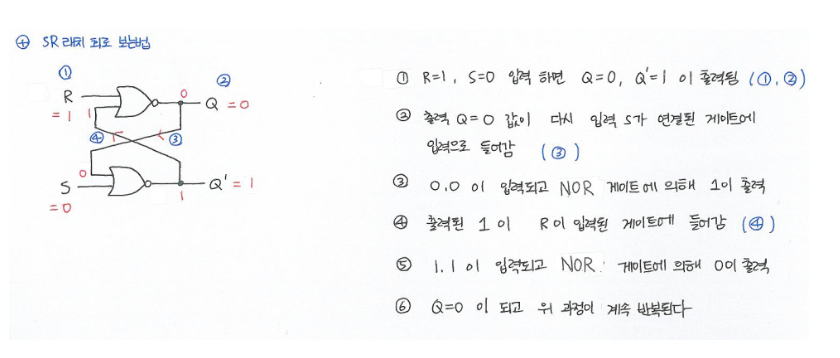

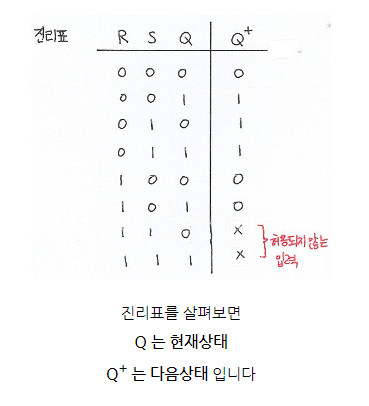

SR Latch : NOR or NAND 게이트로 구성된 회로. S는 set, R은 reset을 의미한다.

- SR Latch는 의 출력을 Q, Q' 라고 할때 두 출력들은 항상 서로 반대 값을 가진다(중요)

- 즉, 입력 S가 1이면 Q는 항상 1이고 R이 1이면 Q`는 항상 1이다.

- 이때 Latch는 메모리를 가지고 있어 Q,Q`의 값은 사라지지 않고 다음 값에 영향을 준다.

- S와 R 입력이 모두 0 즉,(S=0 , R=0)이면 과거 출력 값을 보존한다.

- S와 R 입력이 모두 1 즉,(S=1 , R=1)이면 사용이 금지된 출력이다. (계속 불안정된 상태가 되기 때문에 latch의 출력들이 서로 보수가 되어야한다는 기본규칙에 유배된다.)

- NOR게이트로 구성된 SR Latch의 회로는

S = 1 이면 Q(다음상태) = 1,R = 1 이면 Q(다음상태) = 0,S=R=0 이면 Q =Q(다음상태는 현재상태 즉 상태 유지) - 진리표에의한 특성식은 다음과 같다 =>

[Q = S+RQ] - NAND gate로 S-R Latch를 구성하면 반대로 (0,0)이 사용이 금지되는 출력이된다.(즉, 출력의 결과가 반전.)

회로도와, 특성식 등 정보 : https://blog.naver.com/tb_elec_engineer/221034769694

※ 주의해야할 점은 실제로는 Gate의 전파 지연 시간(delay)때문에 S와R 중 어느 하나가 먼저 High(1)가 되면 다른 것은 Low(0)가 될 수 밖에 없다.

즉, 전파 지연시간(delay)에 따라 출력을 예측할 수 없기 때문에 신뢰성이 떨어진다.

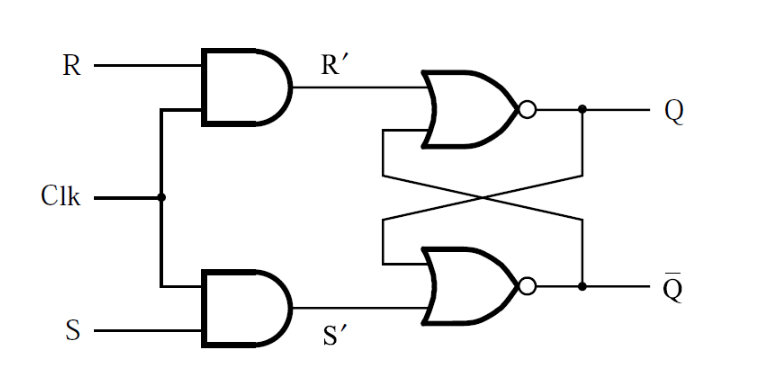

Gated SR Latch : Clk신호를 추가한 SR Latch

- SR Latch의 문제점 2가지 중 한가지를 보완한 회로.

- 문제점 1. 기존의 SR Latch는 S와R을 동시에 1/0으로 만든다면 NOR, NAND의 특성 때문에 출력이 모두 0/1이된다는 단점이 있다.

- 문제점 2. 노이즈가 발생해 R,S 신호를 교란해 기대하지 않은 결과를 나온다.

#이 두가지 문제 2번째 문제를 해결한 것이 Gated SR Latch이다.

- clk신호가 0이면 현재상태를 유지한다.

- NOR게이트에 0과,X 가 들어가면 항상 X`가 출력(입력이 X하나인 NOT 게이트와 같다.)

- 즉, clk = 0 => S와R 값의 상관없이 현재상태를 유지한다.

- clk신호가 1인 경우(High level Trigger)

- 기존의 Latch와 같은 역할을 수행한다.

- 이는 R과S 의 값을 변경할 때만 clk신호를 1로 만들어주고 clk신호가 0이면 R과S 값을 수정하지 못하게 막는다.

- 이 경우 기존 SR Latch의 문제점 중 노이즈가 값을 뒤집어 버리는 경우를 해결한다.

- 단! S와 R이 동시에 1이 되는 문제는 해결하지 못한다.

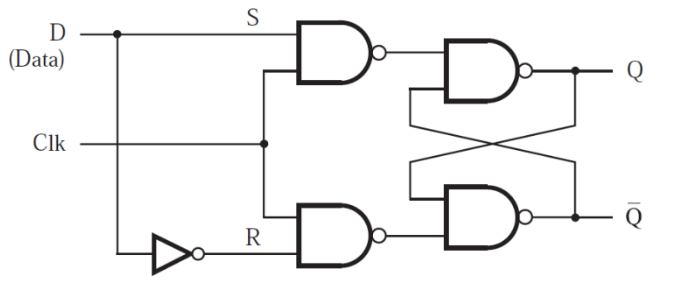

Gated D Latch(F/F) : Gated SR Latch와 다르게 S와 R이 항상 반대 값을 가지게 R에 S의 NOT을 입력하는 회로.

- Gated SR Latch에서 S와 R이 모두 1이되는 문제는 해결하지 못했다. 이를 해결하기 위해 D 입력을 이용해 R에는 NOT을 연결해 문제를 해결해보려한다.

- clk 신호가 0인 경우 : 현재 상태 유지

- NAND 게이트에 1,S가 들어가면 항상 S`(S NOT)이 출력.

- 즉, D의 값과 상관없이 현재상태를 유지한다.

- S = R = 0 => 상관없이 현재상태를 유지한다.

- clk 신호가 1이 경우

- D 가 0 이면 Q´(다음상태)가 0, 1이면 Q´(다음상태)가 1이다.

(즉, D값이 Q´(다음상태)에 그대로 반영.) - D값이 S로, D의 NOT값이 R로 들어가기 때문에 S와 R이 동시에 1이되는 상황을 해결한다.

- D 가 0 이면 Q´(다음상태)가 0, 1이면 Q´(다음상태)가 1이다.

- clk 신호가 0인 경우 : 현재 상태 유지