PDT(Propagation Delay Time)

- PDT가 일어나는 주요원인들은 다음과 같다.

1. 커패시턴스

2. 저항

3. 인덕턴스

4. 부하 용량

왜 이들이 PDT를 일으키는지 이해하기 위해서는 반도체의 기초지식을 알아야하기때문에 정리를 하면서 PDT를 설명하겠습니다.

반도체 소자

- 반도체로 사용되는 4족, 3,5족 화학물이 사용된다.

- 4족은 주로 Si(실리콘)이 사용된다.

- 3,5족은 GaAS, Inp이 사용된다.(이들은 3가 원소 Ga와 5가 원소 As가합해져서 반도체소자가 된다. 주로 광(빛)과 관련된 반도체소자에 이용됩니다.즉, 특수용도에 사용됩니다.)

- 주로 반도체 소자에 사용되는 Si의 원자번호는 14번이다. 이는 원자핵 주변에 14개의 전자를 가지고 있다는 의미이다.(전자는 14개가 무작위로 주변을 도는 것이 아니라 원자핵과 가까운 순서로 2,8,18 ... 순으로 전자가 채워진다.)

원자는 고체가 되면 반드시 체외각 전자가 8개가 되도록 결합을 한다. Si의 경우 4개의 체외각 전자가 존재한다. Si원자는 서로 공유결합을하면서 서로 체외각 전자 하나씩을 공유하여 2개의 체외각 전자가 있는것처럼 보인다. 이렇게 4개의 Si원자가 서로 공유결합을 하여 8개의 체외각 전자가 만들어진다. (공유 결합은 결합력이 강하다!)

- 반도체는 진성반도체(intrinsic) , 불순물 반도체(extrinsic)로 나눌 수 있다.

- 진성반도체는 Si이외 불순물이 하나도 존재하지 않는 single crystal로 이루어진 반도체 이다.(순도 100%, 무결점)

- 전자의 갯수와 Hole의 갯수가 동일하다는 특징이 있다.

- 우리가 중요하게 봐야할 것은 불순물 반도체이다. 반도체에 불순물을 첨가하는데 이 불순물을 우리는 Donor, Acceptor라 칭한다.

- Donor : Si에 5가원소의 불순물을 첨가하면 4개의 전자는 공유결합을 하고 나머지 1개의 체외각 전자 남게된다.

이때 우리는 전자(-)를 n이라 칭하고, Hole(+)(정공)을 p라 칭하면, 불순물의 농도가 높아지면 그만큼 전자의 개수가 많아지게되고 전자의 개수가 많아지면 Hole(정공)이 전자와 결합해 Hole의 개수도 줄어들게 되면서 전자의 개수가 Hole보다 많아지게된다. 우리는 이를 n형 반도체라고 한다! - Acceptor : Si에 3족원소의 불순물을 첨가하게되면 3족원소는 체외각 전자의 수가 3개이다. 즉, 공유결합을 하면 3개의 체외각 전자는 공유결합을 하지만 1개의 전자가 모자르다. 이렇게되면 다른 Si에 있는 전자가 빈자리를 채우면서 공유결합을 하는데 이렇게 빈자리를 매꾸면 다른 Si에서 가져온 전자의 자리에는 Hole이 생성이된다. 그렇게되면서 전자의 갯수보다 Hole의 수가 더 많아지게된다. 우리는 이를 p형 반도체 라고 한다.

반도체 내의 전류가 흐르는 방향은 전자의 방향과 반대이며 Hole의 방향과 같다.

- Drift Current : 옴의 법칙이 성립하는 전류. 즉 ,외부에서 전압이 가해지면 전자(-)와 Hole(+)은 그 반대방향으로 가속.(이동중에는 전자만이 전류를 운반한다.)

- Diffusion Current : Hole밀도가 높은곳에서 낮은곳으로 이동. 즉, 위치에 따른 Carrier의 농도 변화가 발생할때 발생하는 전류 Carrier(전자,Hole)는 농도를 갖는 위치에 절반은 왼쪽, 나머지는 오른쪽으로 이동. Diffusion Current는 Drift Current와 동일하므로 전자의 이동과 반대방향으로, Hole이동과는 같은 뱡향으로 Diffusion Current가 생성된다. (이는 전하의 이동이다. 즉, 전류의 이동!!)

- Donor : Si에 5가원소의 불순물을 첨가하면 4개의 전자는 공유결합을 하고 나머지 1개의 체외각 전자 남게된다.

- 진성반도체는 Si이외 불순물이 하나도 존재하지 않는 single crystal로 이루어진 반도체 이다.(순도 100%, 무결점)

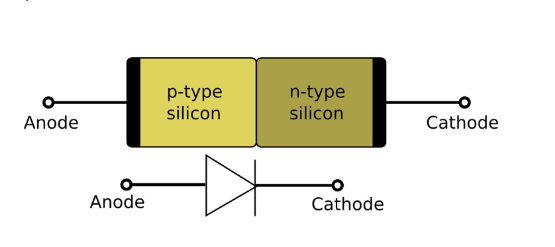

PN Junction Diode

- PN다이오드는 N형 반도체와 P형 반도체 2가지를 붙여놓은것이다.우리는 이를 PN접합 다이오드(PN Junction Diode)라고 부른다.

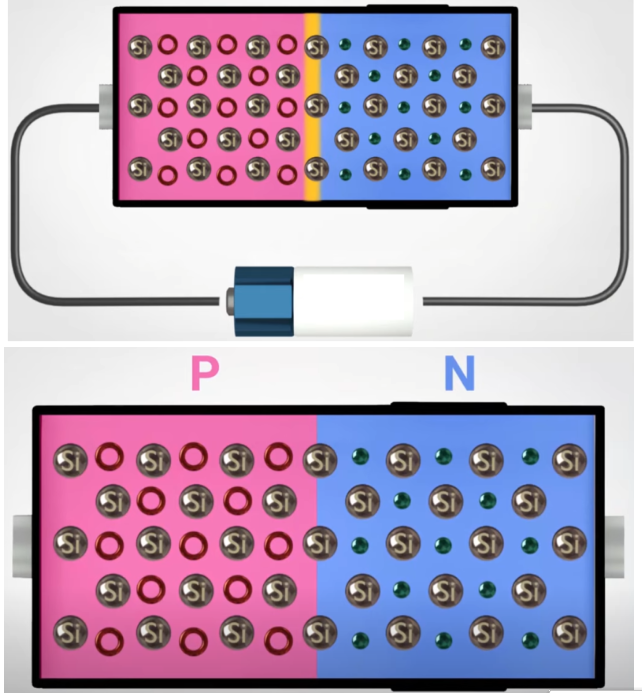

- PN접합이 되면 접합되는 부분에는 N형 반도체에 존재하는 자유전자가 P형 반도체쪽으로 넘어가서 2개의 Silicon의 접합부에서 P쪽은 약간의 (-)극성이되고 N쪽은 자유전자를 뺏김으로써 약간의 (+)극성일 띄게되는데 이것이 위에서 설명한 Diffusion이다(P형 silicon에는 Hole의밀도가 높고 N형에는 Hole의 밀도가 낮으므로 밀도가 높은곳에서 낮은곳으로 Hole이 이동하여 Diffusion Current 발생! 전자도 마찬가지로 N형에서 P형으로 전자가 이동한다. 이때 전류는 전자의 이동과 반대방향이므로 전류는 P->N으로 흐르게 된다.).

- 접합부에는 Diffusion에 의해 공핍영역(Depletion Region)이 생기게된다. 이부분은 극성으로 인해 전기장이 형성되고, 형성된 자기장에 의해 N타입 쪽에 있는 전자는 공핍영역의 (+)쪽으로 끌어당겨진 뒤 다시 다시 P타입쪽 공핍영역의 (-) 극성 전기장에 의해 흐름이 막힌다. 이를 우리는 Barrier라고 하며 문턱전압이라고도 한다. 이는

0.7V의 전위차를 가지게된다

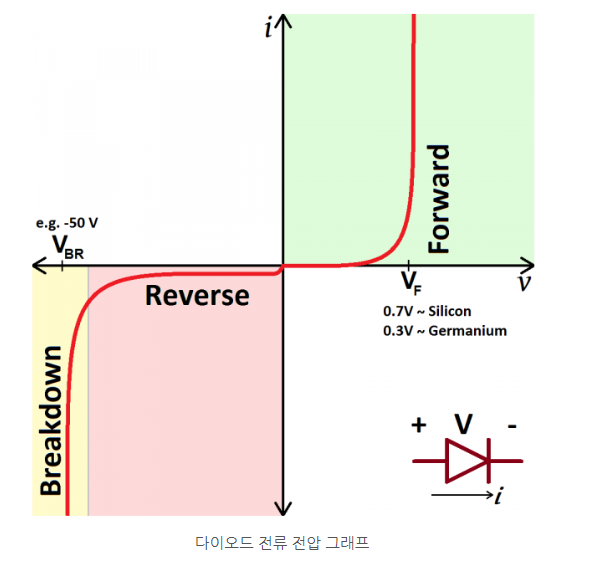

- 이렇게 N형에는 (-)극[GND : 그라운드]가 연결되고 P쪽에는 (+)[VCC]가 연결이되면 공핍영역이 점점 줄어들다가 결국 Barrier가 사라져 전류가 흐르게 됩니다. 이때 그림과 같이 Barrier가 사라지면 전류가 쉽게 흐르게 되는데 이때 실제 전자의 흐름은 N->P로 흐르지만 기존의 물리법칙에서의 전류의 흐름은 (+) -> (-)로 흐르는것으로 착각할 수 있다. 전류의 흐름을 혼동하지말자.(전류의 흐름은 전자의 흐름과 반대!!) 우리는 이를 정방향 바이어스(Forward Bias)라고 한다.

- 이때!! 전류가 흐르게 되는 것은 P쪽에 연결된 전압. 즉, 공급되는 전압이 문턱전압 0.7V를 넘겨야한다. 만약 0.7V를 넘기지 않는다면 0.7V가 넘지 않을때까지는 전류의 흐름이 원활하지 않을것이다. 우리는 공급전압을 활용해 전류가 흐르는 양을 조절할 수 도 있다!

- 위 그림처럼 N쪽에 (+)극[VCC : 공급전압], P쪽에는(-)[GND]를 연결하면 전자와 Hole이 양쪽 끝으로 이동하여 공핍영역이 넓어지면서 Barreir(Barrier Voltage = Built-in Voltage)가 넓어지고 그로 인해 전류가 흐르지 못하게된다. 우리는 이를 역방향 바이어스라고한다.(Reverse Bias)

- 이때, 역방향으로 가해준 전압의 크기만큼 문턱전압(Built-in Voltage)이 커지게되며 위에서 언급한 Diffusion이 거의 일어나지 않는다. 그렇기 때문에 Diffusion Current가 거의 0에 수렴하고 Drift Current만 남게된다. 이때 Drift Current는 온도에 의해 발생하는 Minority Carrier에 의해 발생하므로 애초에 크기가 크지않기때문에 역방향 바이어스에 의해 인가되는 전압의 크기에는 영향을 끼치지 않는다.(하지만 이 적은양의 Carrier로 인해 소량의 전류가 흐른다 . 이는 온도가 높아질 수록 소량의 전류도 상승한다.) 따라서 역전압상태에는 PN접합 다이오드는 Open Circuit으로 동작한다.

PN Junction Diode - Capacitance

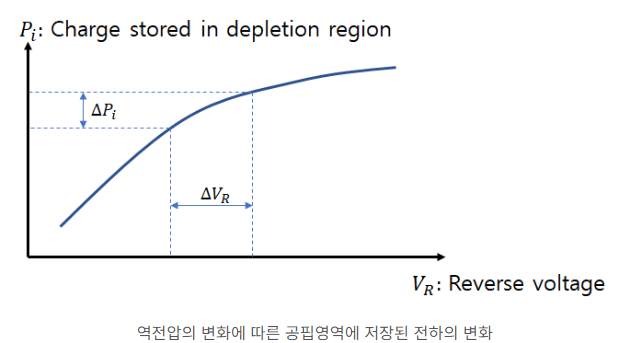

- 역뱡향 바이어스로 전압을 인가했을 때 공핍 영역이 커지면서 전류가 흐르는것이 어려워지는것을 위에서 설명했습니다. 이를 다르게 말하자면 공핍영역에 저장된 전하의 크기가 변화한다고 말할 수 있습니다. 즉! 공급전압의 크기를 변화시키면 공핍영역내에 저장된 전하가 변화합니다.

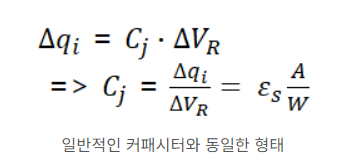

- 사진을 보면 역방향바이어스의 공급전압이 높아지면서 공핍영역의 전하량이 증가하는것을 볼 수 있습니다. 이는 일반적인 커패시턴스(Capacitance)의 식과 동일하다!

- 하지만 역전압의 크기가 계속 커지게되면 Break Down이라는 현상이 발생하여 공유결합이 끊어지면서 무수히 많은 Carrier가 발생하여 공유결합으로 생성된 공핍영역도 사라지면서 전류가 많이 흐를 수 있는 상태가된다. Break Down은 PN접합의 전압이 일정크기가 되었을 때 발생하는데 이때 PN접합은 전압원처럼 동작이 가능하다!

즉! 커페시턴스의 역할을 한다는 것을 정리해보면.

- 커페시터 : 전자회로에서 전하를 모으는 장치.

- 커페시턴스 : 물체가 전하를 축적하는 능력을 나타내는 물리량.

그렇다면 위에서 설명을 한 것처럼 PN접합 다이오드에서 역방향전압이 걸리면 공핍영역이 넓어지면서 공핍영역내의 전하량이 증가한다. 이는 커페시터의 역할을 하며 이렇게되면 PN접합 다이오드 양단에 커패시턴스가 발생하게된다. 이로 인해 다이오드의 내부 전기장이 강해지게되면서 Si이 파괴되거나 커패시턴스가 신호 전달시 전하를 저장하고 방전하는 과정에서 PDT(전파지연: Propagation Delay Time)가 발생하게된다!

그렇다면 회로를 설계할 때 PDT를 줄이기위해서 다양한 요인들이 있겠지만 그 중에서도 커패시턴스로 인한 원인을 해결하기 위해서는 커패시턴스를 줄여야 할 것이다!! 이는 반도체의 크기를 줄이면 해결 될 것이다. 왜? 위에서 언급했듯이 커패시터의 식을 보면 커패시터의 면적(A)를 줄이면 커패시터의 전하량이 줄어들어 PDT의 발생을 낮출 수 있다!