F/F

F/F : Flip Flop

- clk입력을 가지며 clk입력에 반응하여 출력의 상태를 바꾸는 기억소자.

clk(clock)은 출력을 제어하는 입력. - F/F은 Triggering(트리거링)이라는 F/F의 상태를 변화시키는 동작을 의미한다. 이는 clk신호나 set/reset의 입력에 의해 F/F의 상태변화시킨다.

- 2가지 종류의 Trigger

1. Level Trigger- Positive Level Trigger(PLT)

- Negative Level Trigger(NLT)

2. Edge Trigger - Positive Edge Trigger(PET) -> Rising Edge(상승 엣지)

- Negative Edge Trigge(NET) -> Falling Edge(하강 엣지)

※ Trigger로 Latch와 F/F비교

- 메모리소자가 Level Trigger라면 -> Latch

- 메모리소자가 Edge Trigger라면 -> F/F

- JK F/F

- 기존의 F/F 과 유사하지만 이전에 1,1 입력은 금지되는 단점이 있었다. JK F/F은 이것을 보완한다.

- 입력이 1,1 일때 현재출력은 이전 출력의 보수 상태(반전)로 변환한다.

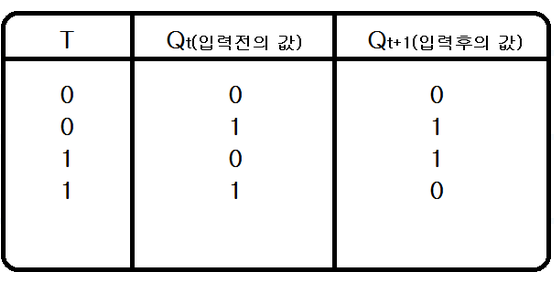

- T F/F

- 두 입력을 같게하여 출력을 0일때 는 현재상태 유지, 1일때는 반전시킨다.

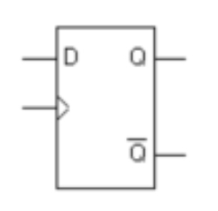

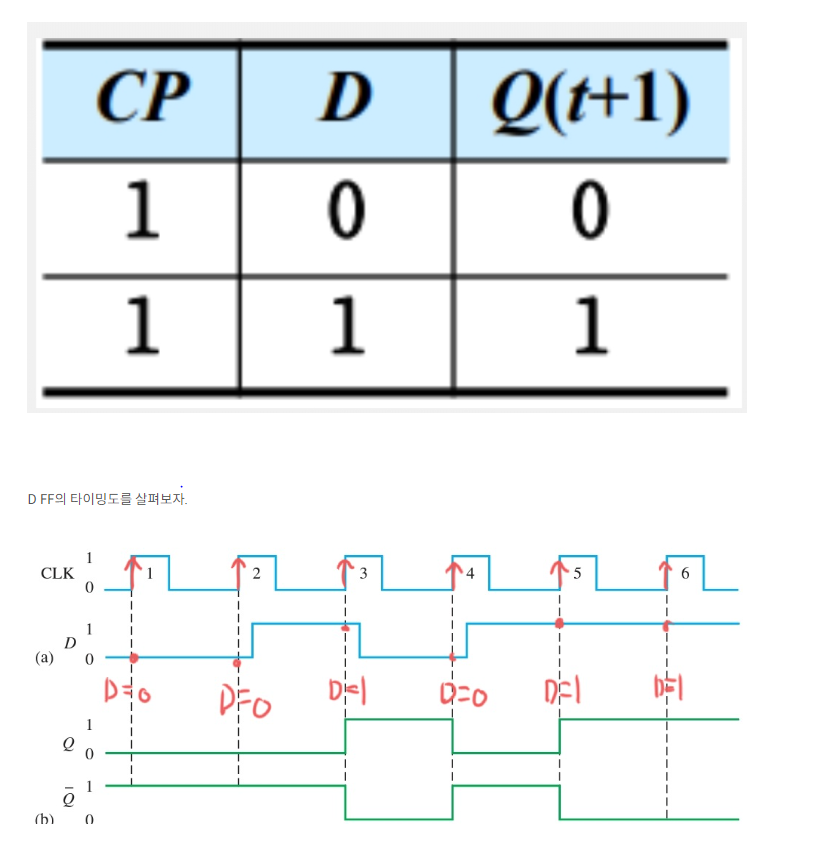

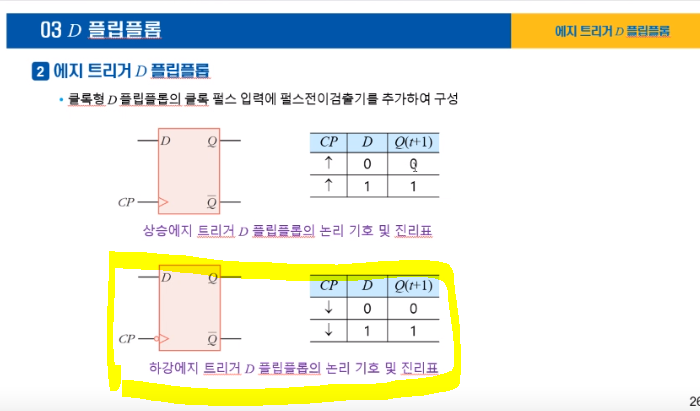

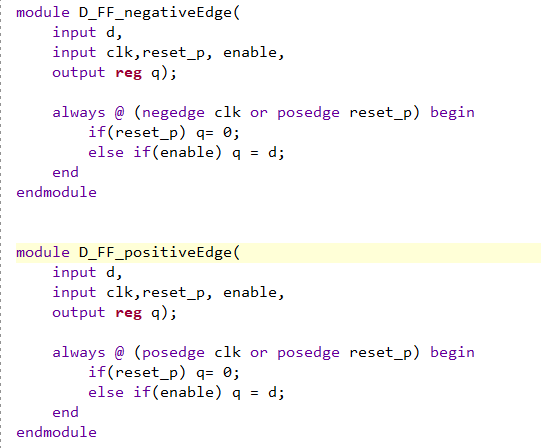

D F/F

- D F/F

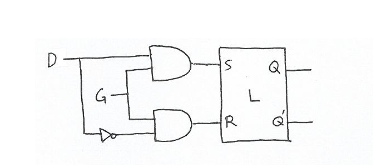

D는 Data를 의미합니다. 신호 전달이 늦어진다는 점에서(회로를 더 많이 거치므로) Delay의 의미도 있습니다. D 플립플롭은 SR 플립플롭에서 R을 사용하지 못하도록 막아놓은 회로입니다. 즉, 다음 클럭까지 D값을 기억하는 회로입니다.

구조를 보면 S가 D로 바뀌어 있고, R이 D의 NOT으로 바뀐 것을 확인할 수 있습니다. 값을 넣어보면 쉽게 알 수 있지만, D=0일 때, Q=0, D=1일 때, Q=1이 됩니다.

- D 플립플롭의 특성표는 다음과 같습니다.

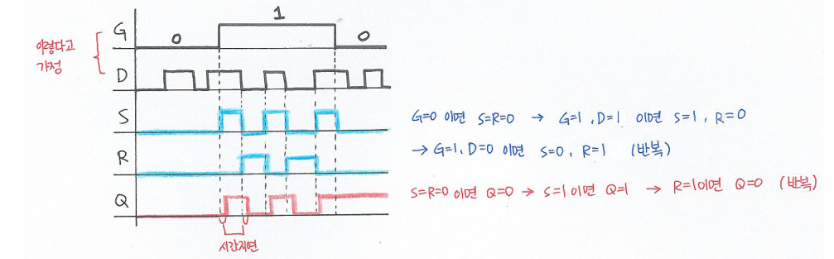

- Gated D Latch

이전에 설명한

Gated D Latch와D F/F는 같다 하지만 이 둘은 Latch로 구현하거나 F/F로 구현한 회로냐에 따라 다르다 이유는 설명했듯이 Trigger방식의 차이이다. F/F은 Edge-Trigger로 Clock이 상승, 하강일때의 D의 값을 출력시켜주고 다음 상승,하강 edge까지 그 출력을 유지한다. 하지만 Latch는 Level-trigger방식으로 clock이 High상태일때의 D값을 출력하고 clock이 Low이면 출력은 0이된다.

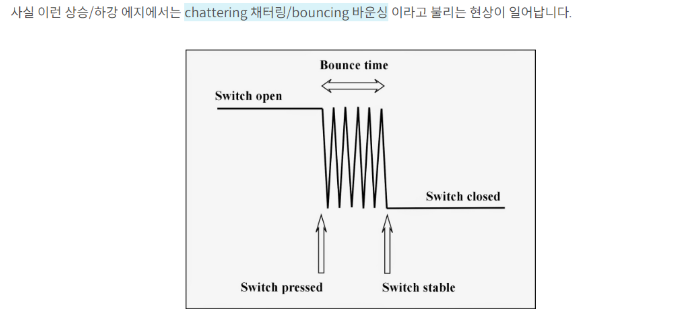

이때 F/F의 Edge-Trigger로 인해 발생하는 문제점이채터링 현상이다

- 해결방법

- 입력 신호 디바운싱(Debouncing)

- 입력 신호에 디바운싱 회로를 추가하여 불안정한 신호를 안정화시킬 수 있습니다.

- 디바운싱 회로는 일정 시간 동안 신호의 변화를 감지하여 안정된 신호만 통과시킵니다.

- RC 필터, 스미트 트리거, 전자 스위치 등의 회로를 활용할 수 있습니다.

- 레벨 트리거(Level-Triggered) 방식 사용

- 레벨 트리거 방식의 플립플롭은 입력 신호가 일정 레벨에 도달하면 동작하므로, 채터링 현상이 발생하지 않습니다.

- 레벨 트리거 방식은 에지 트리거 방식에 비해 복잡도가 높지만, 채터링 문제를 해결할 수 있습니다.

- 동기화 회로 사용

- 입력 신호를 클록 신호와 동기화하여 안정적인 동작을 보장할 수 있습니다.

- 동기화 회로는 입력 신호를 클록 신호에 맞추어 정렬함으로써 채터링 문제를 해결합니다.

- 고속 동작 회로 사용

- 채터링 현상은 주로 느린 동작 속도에서 발생합니다.

- 고속 동작 회로를 사용하면 채터링 현상을 최소화할 수 있습니다.

- 고속 트랜지스터, 고속 논리 게이트 등을 활용할 수 있습니다.

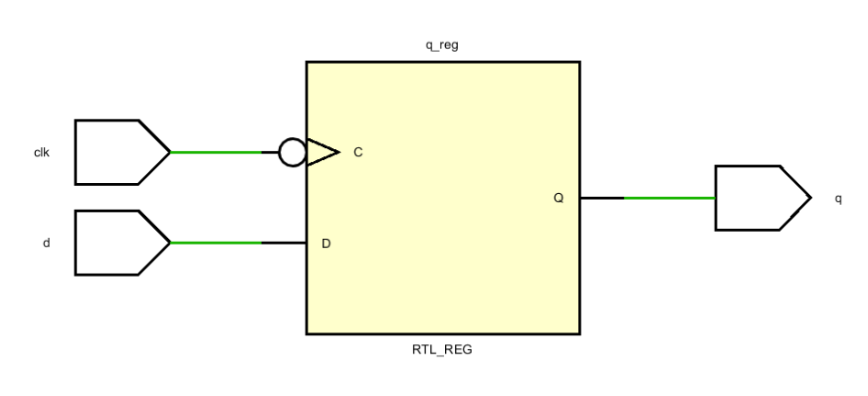

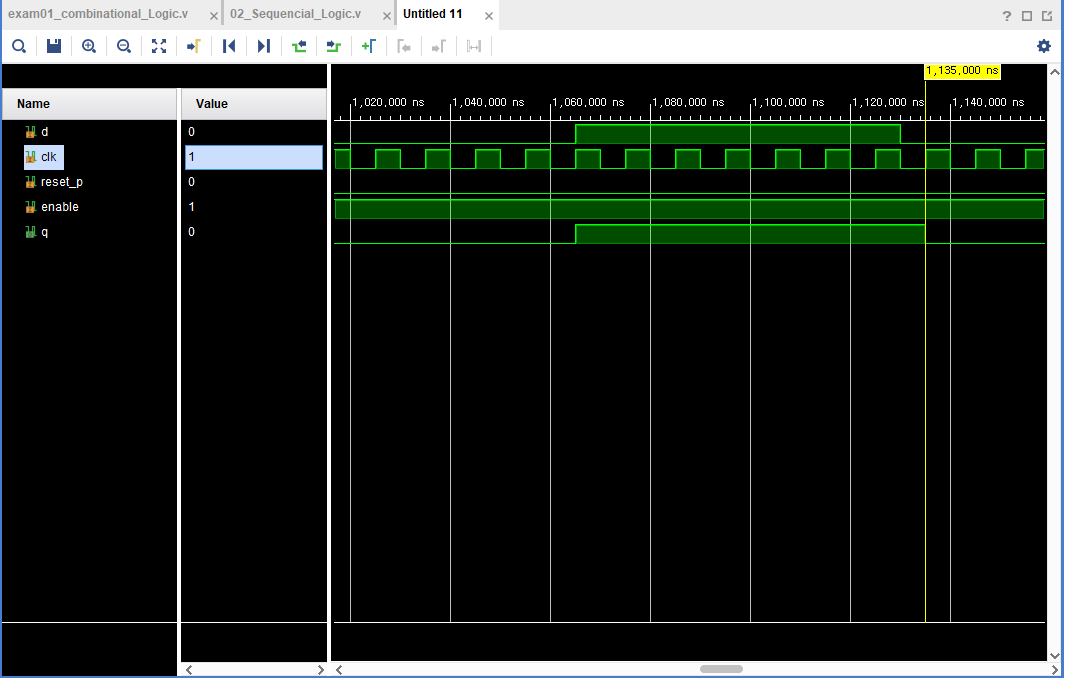

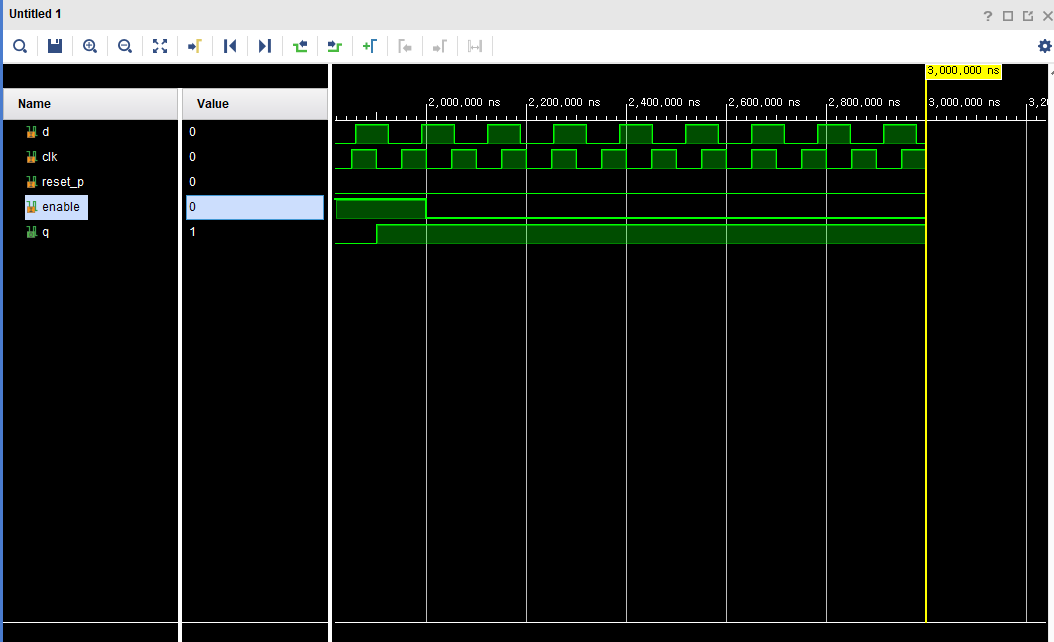

실습

- 결과

- enable 입력이 1 일때 D의 값을 그대로 출력합니다. 단 clk의 positive-edge일때만 D의 값을 확인하여 출력으로 전달합니다.

- enable의 입력이 0 이되면 clk과 d의 입력과는 상관없이 출력이 유지된다. 즉, 입력이 무용지물이란 의미.

- enable 입력이 1 일때 D의 값을 그대로 출력합니다. 단 clk의 positive-edge일때만 D의 값을 확인하여 출력으로 전달합니다.

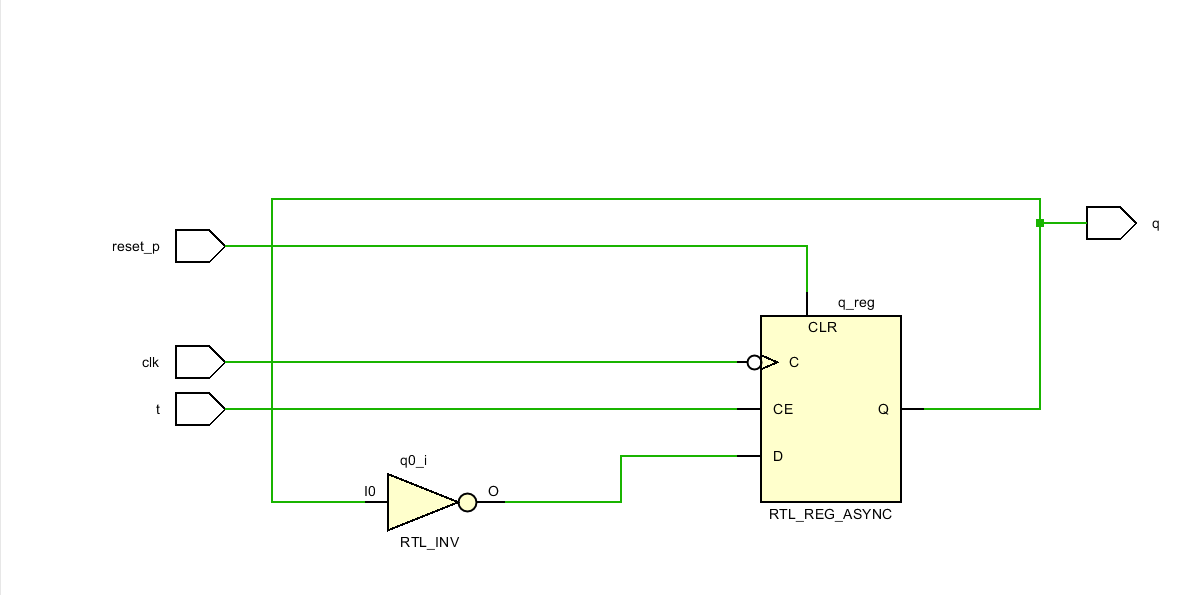

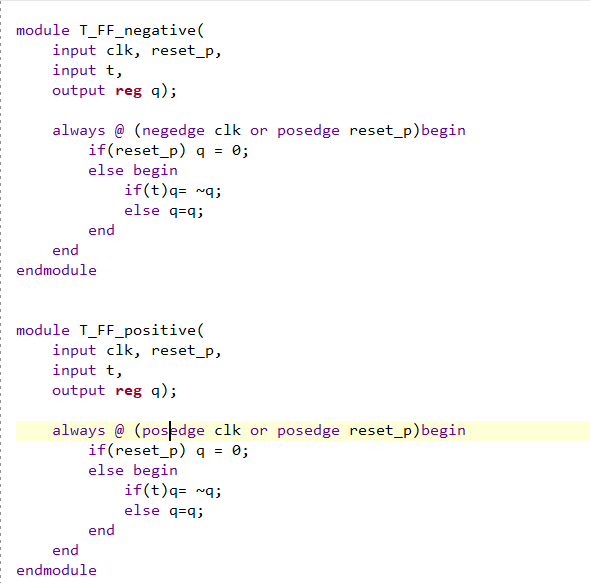

T F/F

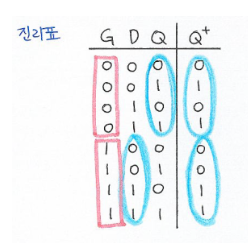

아래 그림은 Elobrate로 로직을 구현한 모습이다. Gate Level로 구현하여서 T F/F을 D F/F의 출력이 입력으로연결되고 거기에 NOT gate가 붙는다.

- 위에서 Verilog 코딩을한 T F/F은 clock의 EdgeTriggr(rising, falling) 일때 만약 T의 입력이 0이라면 출력 q는 입력값의 현재상태를 유지하고 T의 입력이 1이라면 출력 q는 입력값의 현재상태를 반전시켜 출력한다.

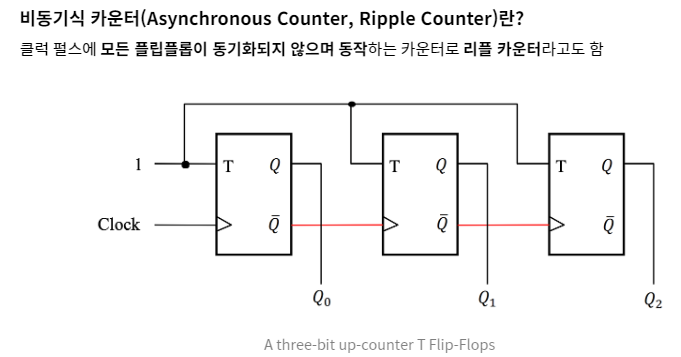

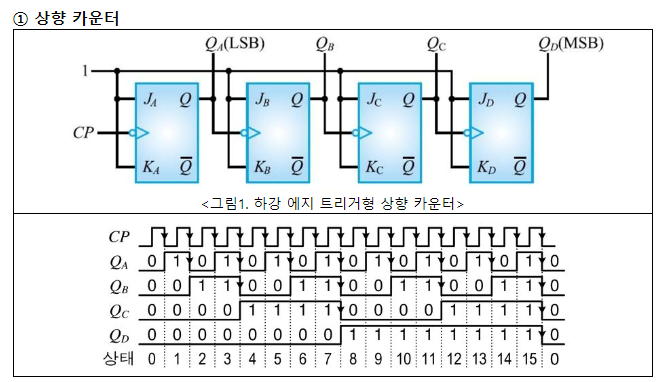

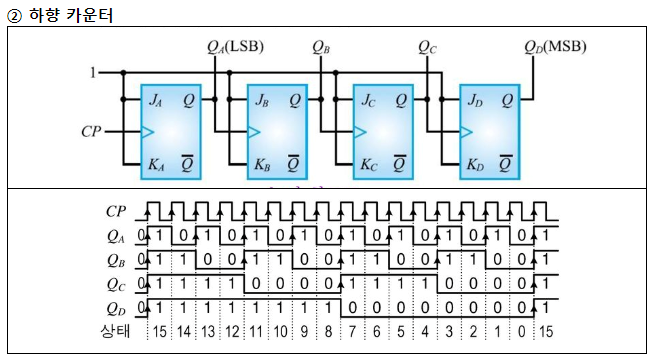

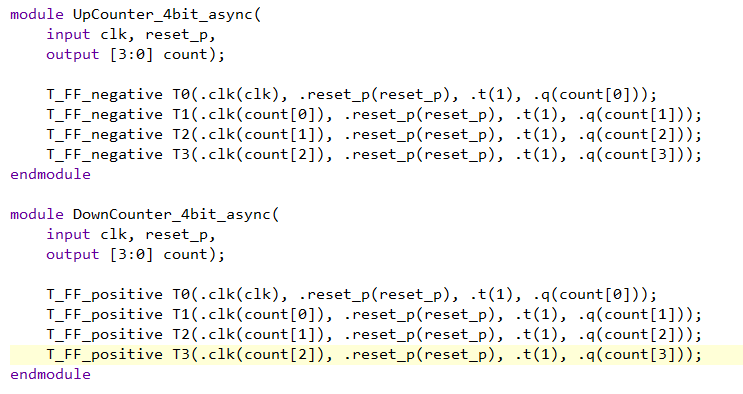

UP,Down Counter

-

T F/F을 활용한 것이 Counter이다.

-

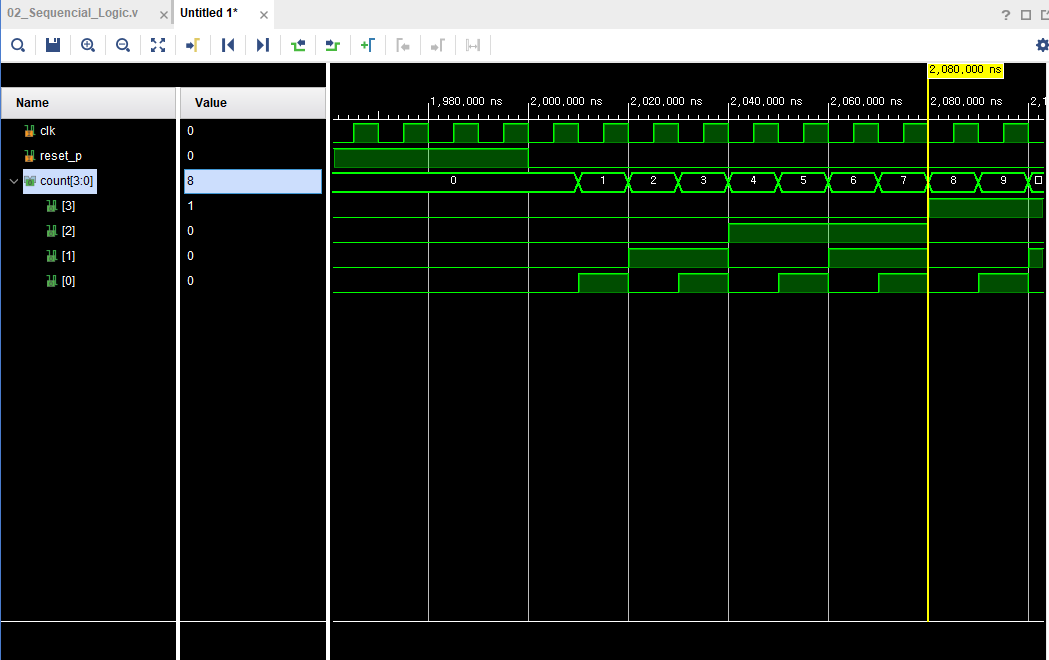

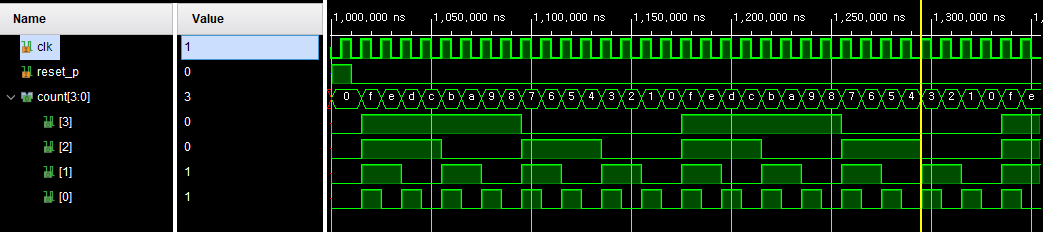

결과

- UpCounter

- DownCounter

★★★

1.상승엣지, 하강엣지 두개 모두 처음 clk신호에 따라서 먼저 엣지에서 출력을 반전시킨다.

2. 두번째 T F/F에서의 입력은 첫번째 clk신호를 입력으로 받은 출력이다. 즉 타이밍도를 보면 첫번째의 출력이 2번째 T F/F의 입력이되어 첫번째 출력의 엣지 즉, 두번째의 입력의 clk은 첫번째 F/F의 clk의 엣지에 의해 반전시킨 출력이 들어가는 것이다.

- UpCounter

F/F의 동작특성

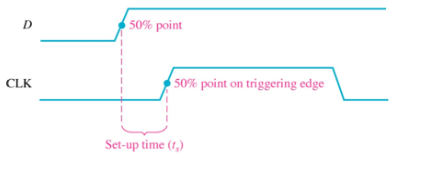

Setup Time (설정 시간):

- Setup Time은 데이터 입력 신호가 플립플롭의 클록 입력 전에 안정된 상태로 유지되어야 하는 최소 시간입니다.

- 데이터 입력 신호가 Setup Time 내에 변경되면 플립플롭의 동작이 불안정해질 수 있습니다.

- Setup Time은 플립플롭의 내부 동작 특성에 따라 달라지며, 데이터 입력 신호와 클록 신 호 간의 타이밍 관계를 결정합니다.

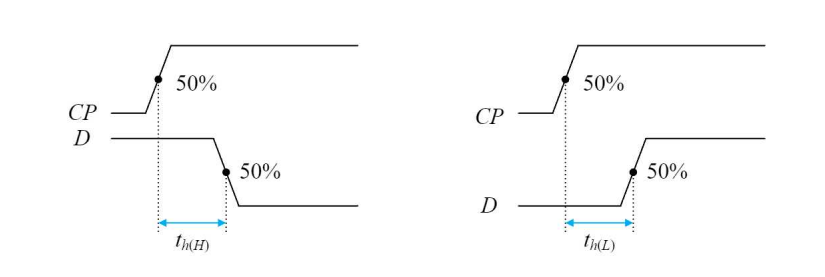

Hold Time (유지 시간):

- Hold Time은 데이터 입력 신호가 플립플롭의 클록 입력 이후에도 일정 시간 동안 안정된 상태로 유지되어야 하는 최소 시간입니다.

- 데이터 입력 신호가 Hold Time 내에 변경되면 플립플롭의 동작이 불안정해질 수 있습니다.

- Hold Time 또한 플립플롭의 내부 동작 특성에 따라 달라지며, 데이터 입력 신호와 클록 신호 간의 타이밍 관계를 결정합니다.

펄스 폭 (Pulse Width):

- 플립플롭의 클록 입력 신호는 일정 시간 동안 High 또는 Low 상태를 유지해야 합니다.

- 이 때 High 또는 Low 상태를 유지하는 시간을 펄스 폭이라고 합니다.

- 펄스 폭이 너무 좁으면 플립플롭이 제대로 동작하지 않을 수 있습니다.

- 플립플롭 데이터시트에 지정된 최소 펄스 폭 사양을 확인하고 이를 준수해야 합니다.

최대 주파수 (Maximum Frequency):

- 플립플롭은 일정 주파수 이상에서는 제대로 동작하지 않습니다.

- 플립플롭의 최대 동작 주파수는 플립플롭의 내부 동작 속도에 따라 결정됩니다.

- 최대 주파수를 초과하면 플립플롭이 불안정해지거나 오동작할 수 있습니다.

- 데이터시트에 명시된 최대 주파수 사양을 확인하고 이를 준수해야 합니다.

- 플립플롭의 동작속도를 결정하는 중요한 파라미터, 플립플롭이 안전하게 동작할 수 있는 최대 주파수이며 항상 최대 클록 주파수 이하에서 동작시켜야 한다.

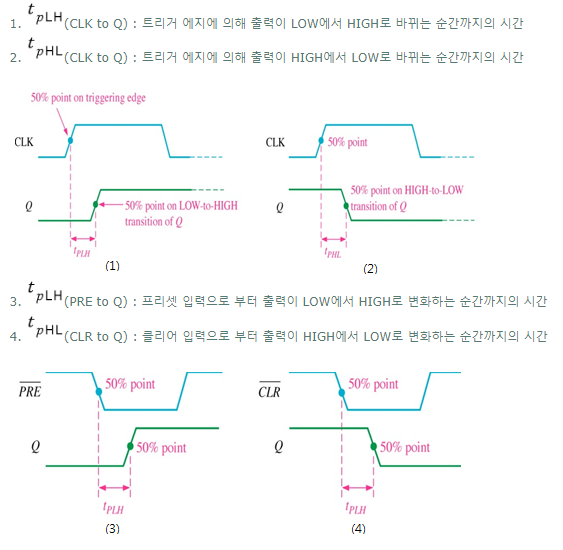

PDT(Propagation Delay Time):

- PDT는 입력 신호가 회로에 인가되어 출력 신호가 발생하기까지의 지연 시간을 의미합니다.

- 앞서 설명한 것처럼 회로의 기생 요소들로 인해 PDT가 발생합니다.

- PDT는 디지털 회로의 동작 속도와 직결되는 중요한 요소입니다.

Glitch현상과는 다르다.

글리치는 디지털 회로에서 원치 않는 순간적인 펄스 신호가 발생하는 현상을 말합니다.

글리치는 주로 조합 논리 회로에서 발생하며, 입력 신호의 타이밍 차이로 인해 발생합니다.

예를 들어, AND 게이트의 입력 신호들이 서로 다른 시간에 변화하면 잘못된 출력 신호가 나타날 수 있습니다. 글리치는 회로의 오동작을 유발할 수 있으므로 방지해야 합니다

다음에는 PDT의 대한 정리를 하겠습니다. 이를 확실하게 알고 넘어가기위해 반도체의 기초적인 지식들또한 정리하도록 하겠습니다.