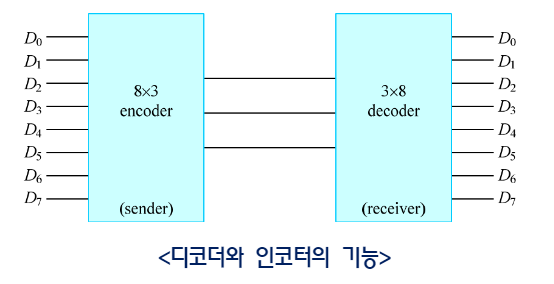

인코더(Encoder)

역할 : 여러 개의 입력 신호를 받아 이를 더 적은 수의 비트로 변환.

설명 : n개의 입력을 이진 코드로 압축하여 m개의 비트로 변환.

디코더(Decoder)

역할 : 입력된 이진 코드를 받아 이를 여러 개의 출력 신호로 변환.

설명 : m개의 비트를 받아 이를 최대 2^m개의 출력으로 확장

인코더와 디코더의 입력 신호는 하나씩 들어오는 것.

8X3일때 인코더는 8가지 경우의 수의 신호->3비트로 변환, 디코더는 3비트를 8가지 신호로 변환

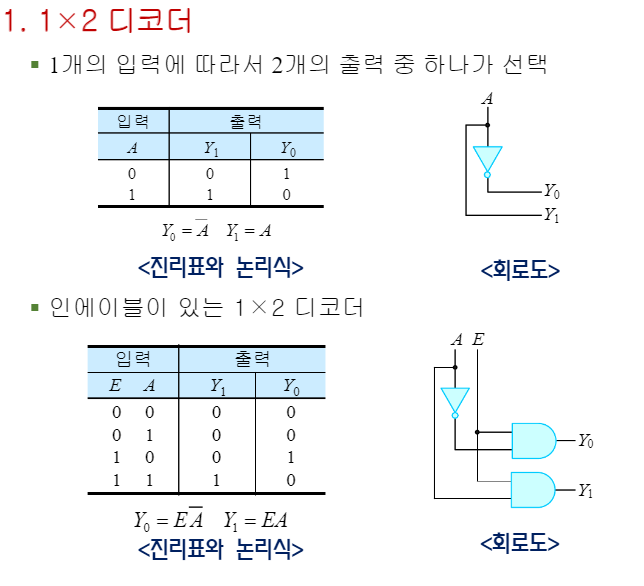

인에이블 신호 (Enable Signal)

인에이블 신호 (Enable Signal)

역할 : 디코더의 동작을 활성화 또는 비활성화하는 기능.

기능 : 인에이블 신호가 활성화 상태일 때만 디코더가 입력 신호를 해석하여 출력 신호를 생성. 비활성화 상태에서는 디코더가 작동하지 않거나 모든 출력을 비활성화 상태로 유지.

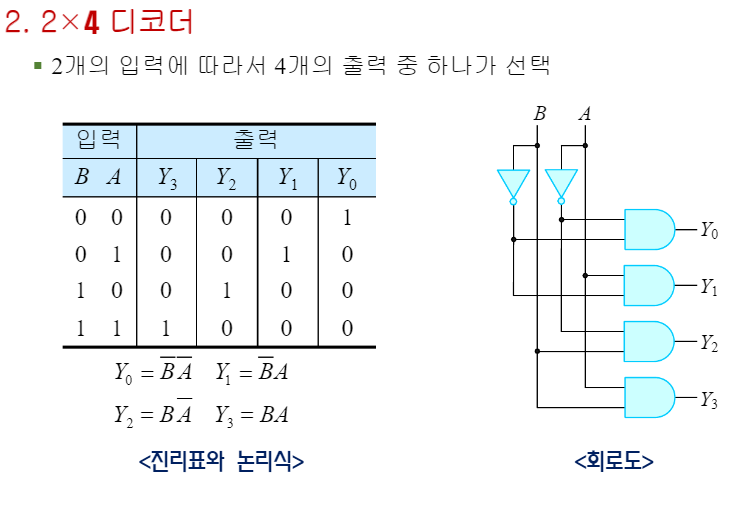

2x4 디코더

동작적 모델링

if문, case문 사용 (둘다 처리되지 않는 나머지 경우의 수에대해 설정을 꼭 해야줘야한다)

if문 사용

module decoder_2X4_b(

input [1:0] code, //2비트 입력신호

output reg [3:0] signal); //4가지의 출력신호

always @(code)begin //code신호 변화일때 동작

if(code == 2'b00) signal = 4'b0001; //2비트를 4가지 경우의 수로 변환

else if(code == 2'b01) signal = 4'b0010;

else if(code == 2'b10) signal = 4'b0100;

else if(code == 2'b11) signal = 4'b1000;

else signal = 4'b1000; //처리 되지 않은 나머지 경우의 수에대한 설정

end

endmoduleforce clock

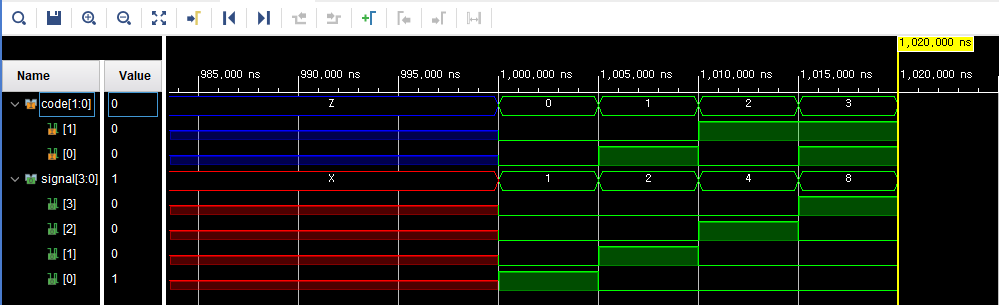

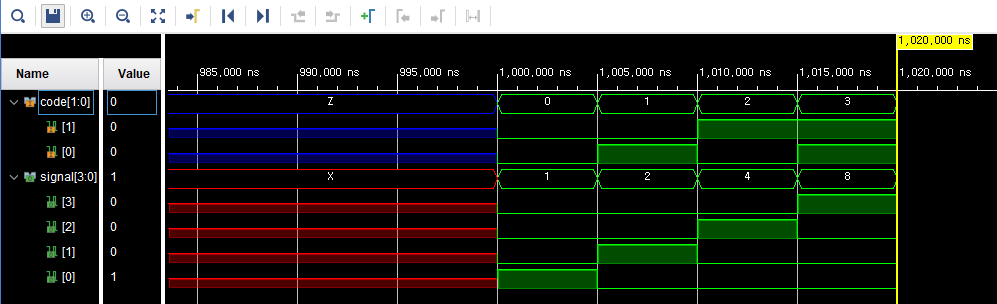

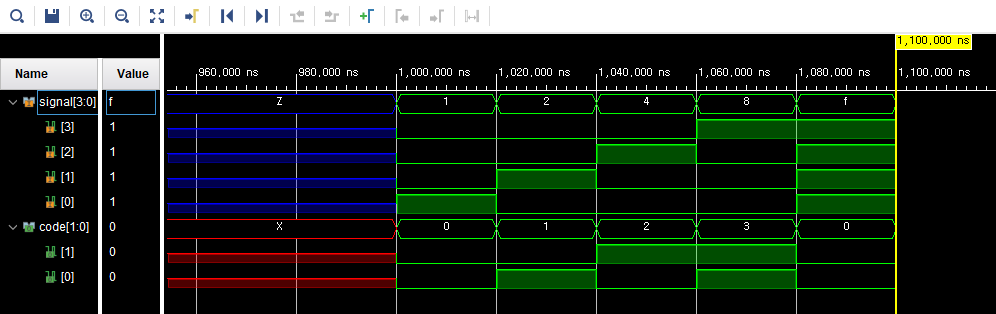

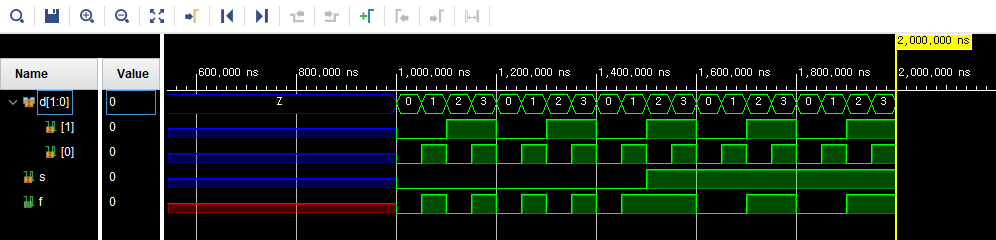

code[0] 10ns, code[1] 20ns

각 비트값에 해당하는 경우의 수 할당

각 비트값에 해당하는 경우의 수 할당

case문 사용

case문은 모든 경우에 대해 설정, 사용하지 않은 경우의 수가 있으면 default 사용, 설정하지않으면 이전출력 유지(래치 사용)(이렇게 되면 안됨, 이유는 래치 배우면)

module decoder_2X4_b(

input [1:0] code,

output reg [3:0] signal);

// if문 사용

// always @(code)begin

// if(code == 2'b00) signal = 4'b0001;

// else if(code == 2'b01) signal = 4'b0010;

// else if(code == 2'b10) signal = 4'b0100;

// else if(code == 2'b11) signal = 4'b1000;

// else signal = 4'b1000;

// end

// case문 사용

always @(code)begin

case(code)

2'b00 : signal = 4'b0001;

2'b01 : signal = 4'b0010;

2'b10 : signal = 4'b0100;

2'b11 : signal = 4'b1000;

default : signal = 4'b0001;

endcase

end

endmoduleif문과 case문 둘다 같은결과가 나옴

dataflow 모델링

module decoder_2X4_b(

input [1:0] code,

output [3:0] signal);

assign signal = ( code == 2'b00) ? 4'b0001 :

((code == 2'b01) ? 4'b0010 :

((code == 2'b10) ? 4'b0100 : 4'b1000));

endmodule

조건식 겹쳐서 사용, 조건식 참일때 원래의 정해진 경우의 수가 나오고 거짓일때 다시 조건식으로 들어가 다시 원래의 정해진 경우의 수가 나오고 반복

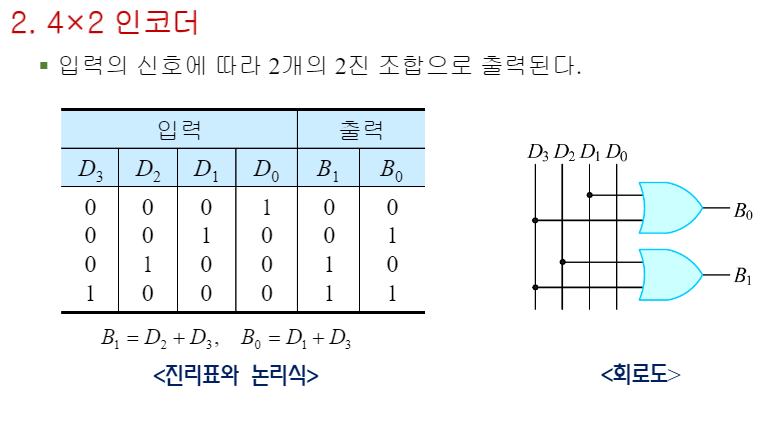

4X2 인코더

동작적 모델링

if문 사용

module encoder_4X2_b(

input [3:0] signal,

output reg [1:0] code);

always @(signal)begin

if(signal == 4'b0001) code = 2'b00;

else if(signal == 4'b0010) code = 2'b01;

else if(signal == 4'b0100) code = 2'b10;

else if(signal == 4'b1000) code = 2'b11;

else code = 2'b00;

//4가지의 입력상태에서만 동작 나머지 입력은 else로 처리

//else문 없면 랫치회로 생성-랫치회로는 만들어지면 안됨

//else문 동작은 평상시상태로-다른 동작이 생기면, 비용발생이나 리소스 사용

end

endmodulecase문 사용

module encoder_4X2_b(

input [3:0] signal,

output reg [1:0] code);

// always @(signal)begin

// if(signal == 4'b0001) code = 2'b00;

// else if(signal == 4'b0010) code = 2'b01;

// else if(signal == 4'b0100) code = 2'b10;

// else if(signal == 4'b1000) code = 2'b11;

// else code = 2'b00;

// end

always @(signal)begin

case(signal)

4'b0001 : code = 2'b00;

4'b0010 : code = 2'b01;

4'b0100 : code = 2'b10;

4'b1000 : code = 2'b11;

default : code = 2'b00;

endcase

end

endmoduledataflow 모델링

module encoder_4X2_d(

input [3:0] signal,

output [1:0] code);

assign code = (signal == 4'b0001) ? 2'b00 :

((signal == 4'b0010) ? 2'b01 :

((signal == 4'b0100) ? 2'b10 : 2'b11));

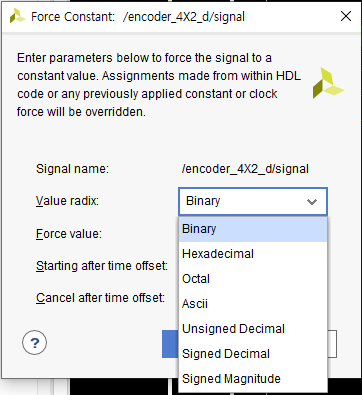

endmoduleforce constant사용

2진수값 입력으로 사용 설정

입력값 2진수, 각각 0001넣고 확인, 0010넣고 확인, 0100넣고 확인, 1000넣고 확인 후 1111입력확인-조건문 맨 마지막 적용(default와 같이 쓰임)

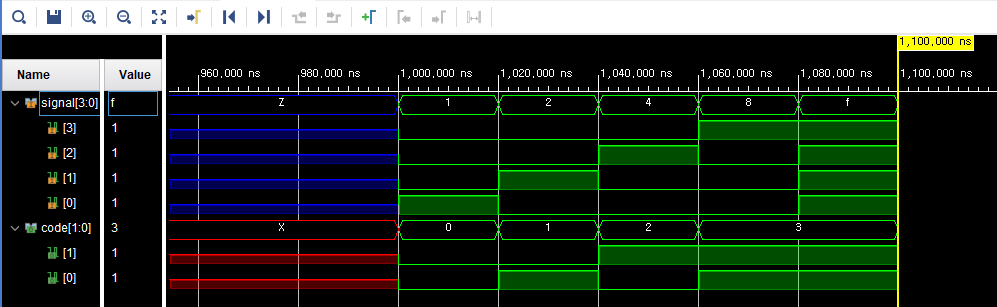

module encoder_4X2_d(

input [3:0] signal,

output [1:0] code);

assign code = (signal == 4'b0001) ? 2'b00 :

((signal == 4'b0010) ? 2'b01 :

((signal == 4'b0100) ? 2'b10 :

((signal == 4'b1000) ? 2'b11 : 2'b00))); //정해진 경우의 수 이외의 값을 입력했을때

//default값으로 평상시(2'b00)상태로 출력하기 위한 코드추가

endmoduledefault값을 설정한뒤 1111입력한 모습-2'b00으로 출력 나옴

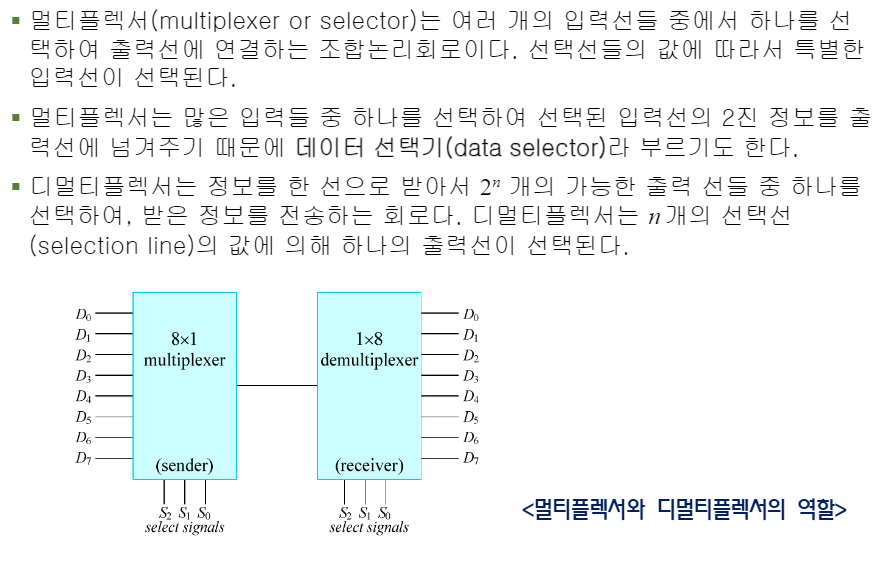

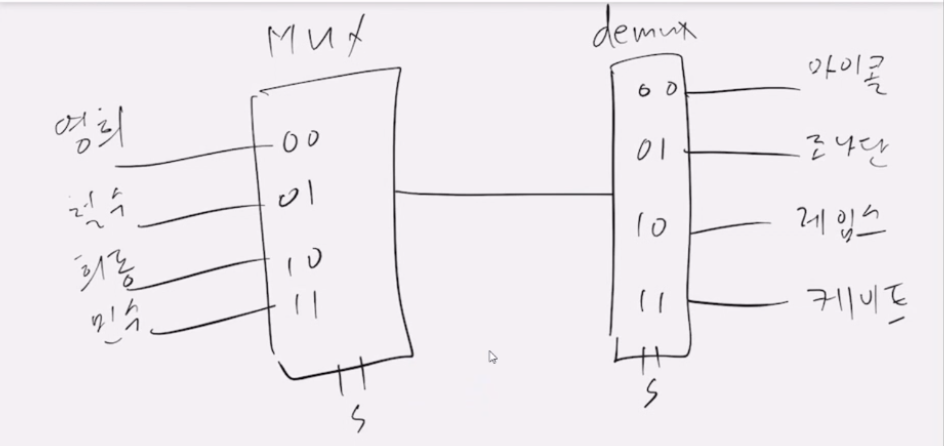

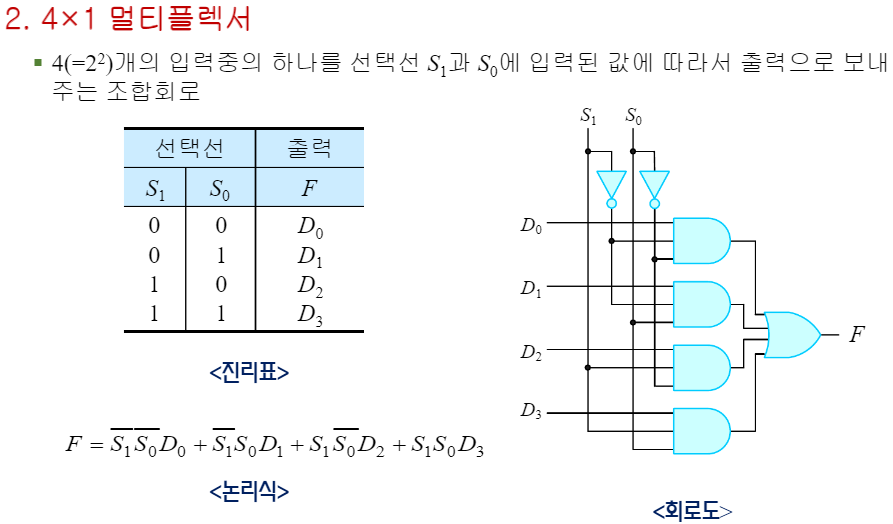

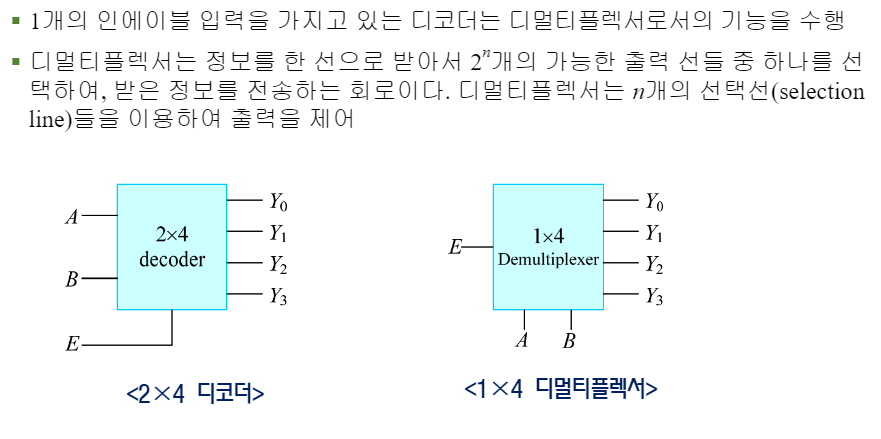

멀티플렉서와 디멀티플렉서

멀티플렉서와 디멀티플렉서는 전자 시스템에서 신호 경로를 선택하고 분배하는 데 중요한 역할을 하는 장치들이다.

멀티플렉서 (Multiplexer, MUX)

역할 : 여러 개의 입력 중 하나를 선택하여 단일 출력으로 전달하는 장치.

구성 : n개의 입력, m개의 선택 신호 (Select Signals), 1개의 출력.

m개의 선택 신호로 2^m개의 입력 중 하나를 선택.

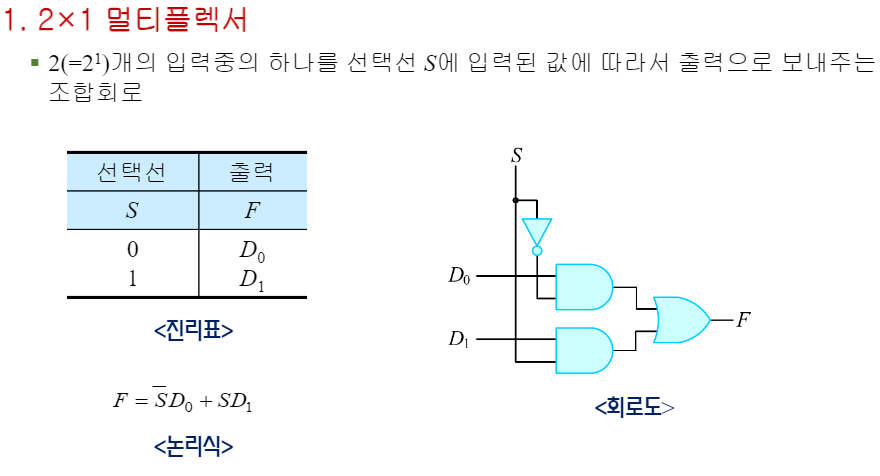

2X1 mux

module mux_2_1(

input [1:0] d,

input s,

output f);

assign f = s ? d[1] : d[0];

endmodules가 0일때 d[0]이 그대로 출력 s가 1일때 d[1]이 그대로 출력

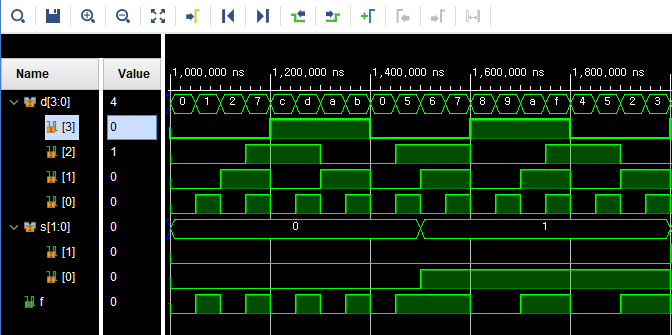

4X1 mux

벡터([3:0]또는 [1:0]같이 선언된것)로 선언된 신호는 개별 비트로 접근하거나 하나의 숫자 값으로 사용할 수 있다.

module mux_4_2(

input [3:0] d,

input [1:0] s,

output f);

assign f = d[s]; //인덱스를 s로 줌(00,01,10,11)

//s가0일때 d0출력, s가1일때 d1출력, s가2일때 d2출력, s가3일때 d3출력

endmodule

s[0]과 d[0] 연결 f에 d의 값(파형) 그대로 출력, s(1,2,3)과 d(1,2,3)도 마찬가지

8X1 mux

module mux_8_1(

input [7:0] d,

input [2:0] s,

output f);

assign f = d[s];

endmodule반대상황인 1x8 디멀티플렉서일때 f[s]=d는 불가

//module mux_8_1(

// input d,

// input [1:0] s,

// output f[3:0]);

// assign f[s] = d; //이렇게 하면 f[0]일때 나머지 인덱스들을 정해줄 수 없다

//endmodule디멀티플렉서의 경우, 하나의 입력 신호를 여러 출력으로 분배하기 때문에 각 출력이 특정 선택 신호에만 활성화되고 나머지 출력은 비활성화 상태로 유지되어야 한다. 이를 위해서는 각 출력에 대해 조건을 지정해 주어야 한다.(연결되지 않은 출력에는 0이라는 출력을 해줘야함, 그렇지 않으면 끊긴 상태와 같음)

디멀티플렉서 (Demultiplexer, DEMUX)

역할 : 단일 입력 신호를 받아 이를 여러 출력 중 하나로 분배하는 장치.

구성 : 1개의 입력, m개의 선택 신호 (Select Signals), n개의 출력.

m개의 선택 신호로 2^m개의 출력 중 하나를 선택.

1X4 디멀티플렉서

결합연산자'{}'사용

기능 : 여러 개의 벡터나 레지스터를 하나로 합치는 연산자.

예시 설명 : a와 b라는 두 개의 벡터를 {} 안에 넣어서 연결하면, 두 벡터가 연속적으로 이어진 새로운 벡터를 생성한다. 예를 들어, a가 [3:0] 범위이고 b가 [3:0] 범위일 때, {a, b}는 [7:0] 범위의 새로운 벡터를 생성한다.

module demux_1_4(

input d,

input [1:0] s,

output [3:0] f);

assign f = (s == 2'b00) ? {3'b000, d} :

((s == 2'b01) ? {2'b00, d, 1'b0} :

((s == 2'b10) ? {1'b0, d, 2'b00} : {d, 3'b000}));

endmodule

s값이 0,1,2,3 변할때 그에 맞는 출력값 f의 인덱스에 출력된다 입력d의 값(파형)이 그대로 출력

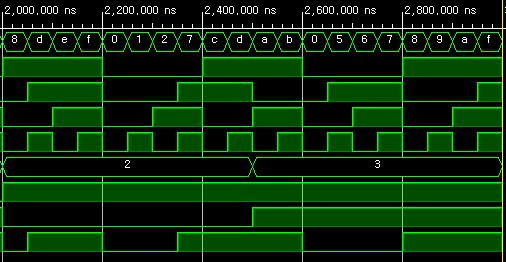

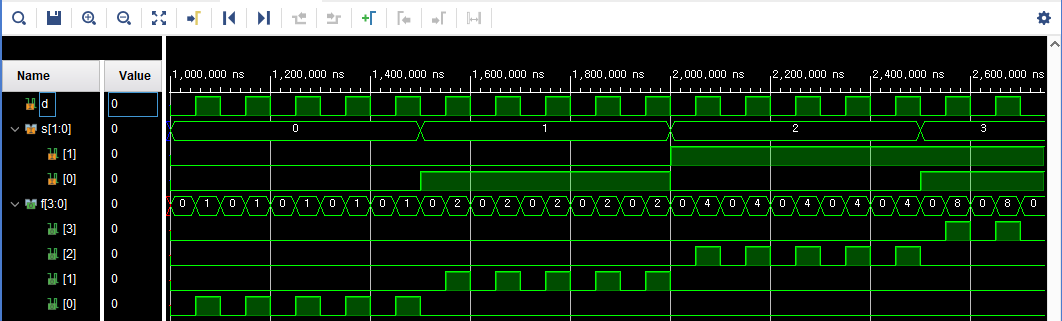

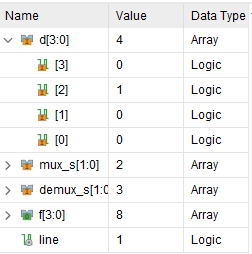

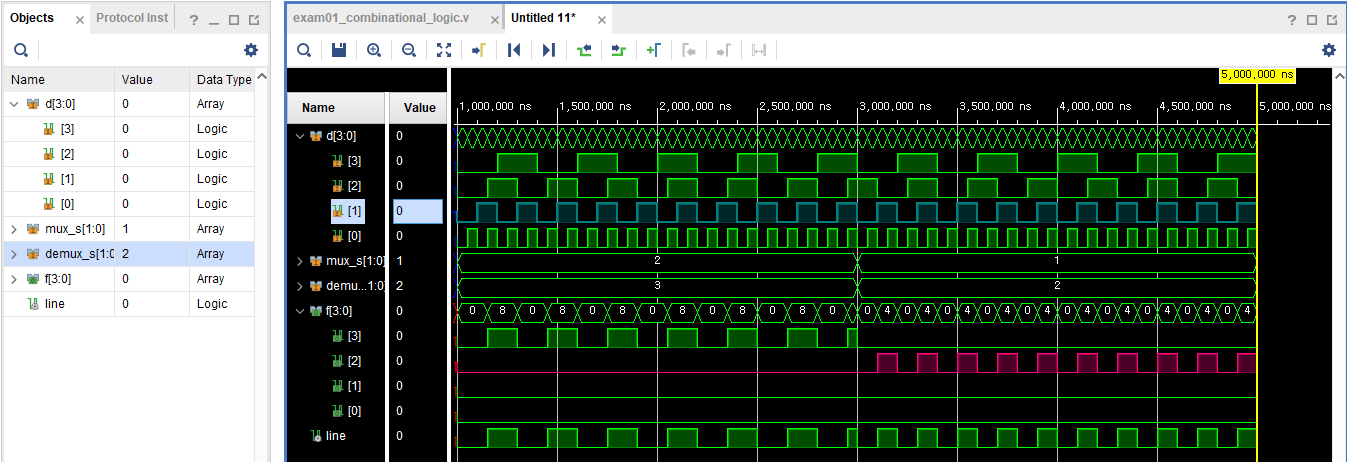

mux_demux

module mux_demux_test(

input [3:0] d,

input [1:0] mux_s, demux_s,

output [3:0] f);

wire line;

mux_4_1 mux(.d(d), .s(mux_s), .f(line));

demux_1_4 demux(.d(line), .s(demux_s), .f(f));

endmodule

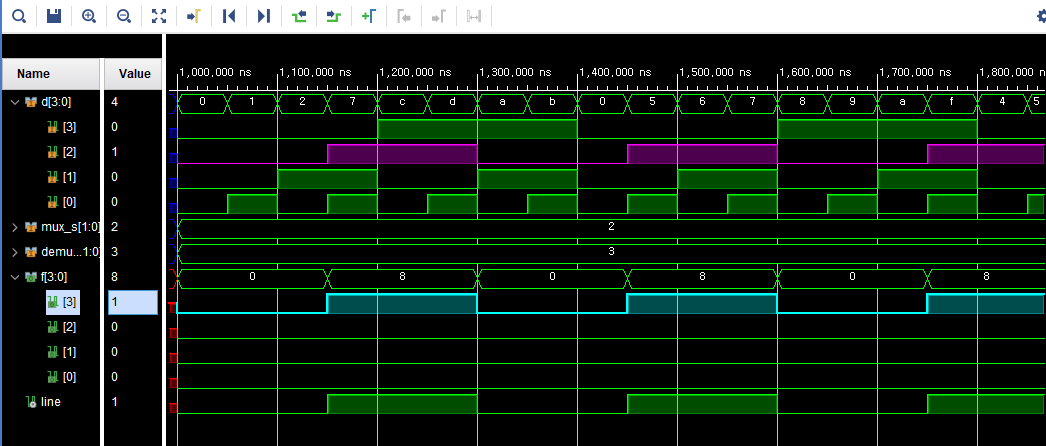

d[2]와 f[3]과 연결, mux의 force constant에 값2, demux의 force constant에 값3

d[1]과 f[2]연결, mux의 force constant에 값1, demux의 force constant에 값2

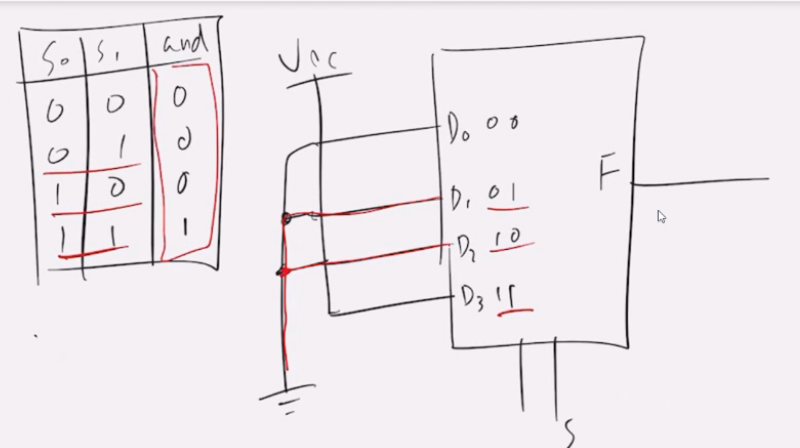

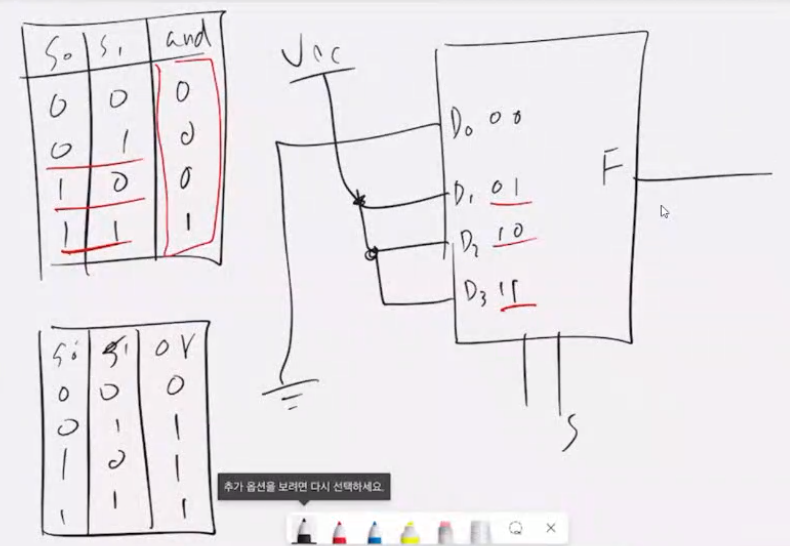

멀티플렉서를 이용한 조합회로 구현

mux로 AND구현

mux로 OR구현

진리표대로 Vcc와 Gnd연결, 조합회로는 모두 구현 가능

룩업 테이블, LUT(look-up table)

LUT는 미리 정의된 테이블로, 입력 신호 조합에 대한 출력 값을 저장한다.

위의 mux들과는 다르게 입력값(파형)은 5v 고정