(IP 추가 방법은 카테고리 vivado의 IP추가 관련 포스팅 참조)

내부 신호 추적을 위한 디버깅 IP

simulation은 만든 모듈을 사전에 시험하기위함이라면

ILA는 보드에 bitstream한 다음에 동작을 확인하기 위함

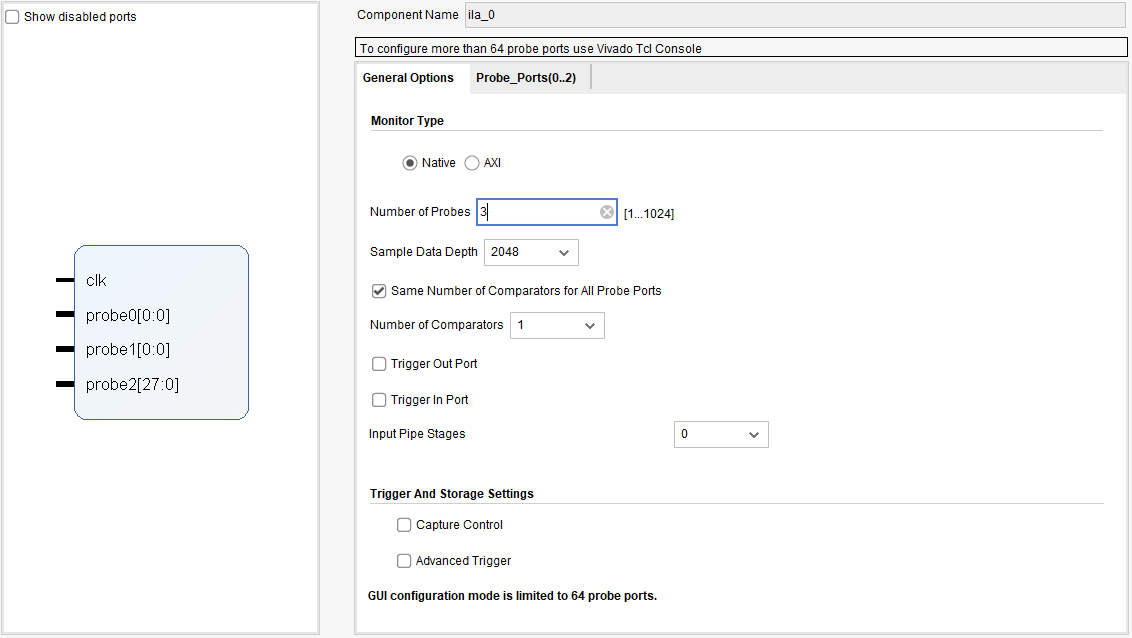

number of probes : 확인할 신호 수

sample data depth : 신호가 표시될 비트 크기 (시뮬레이션 창 처럼 신호의 high 또는 low가 표현되는데 이것이 표현되는 길이이다)

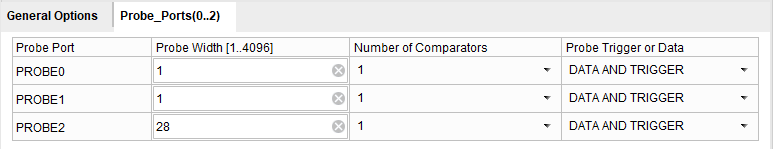

신호의 비트수

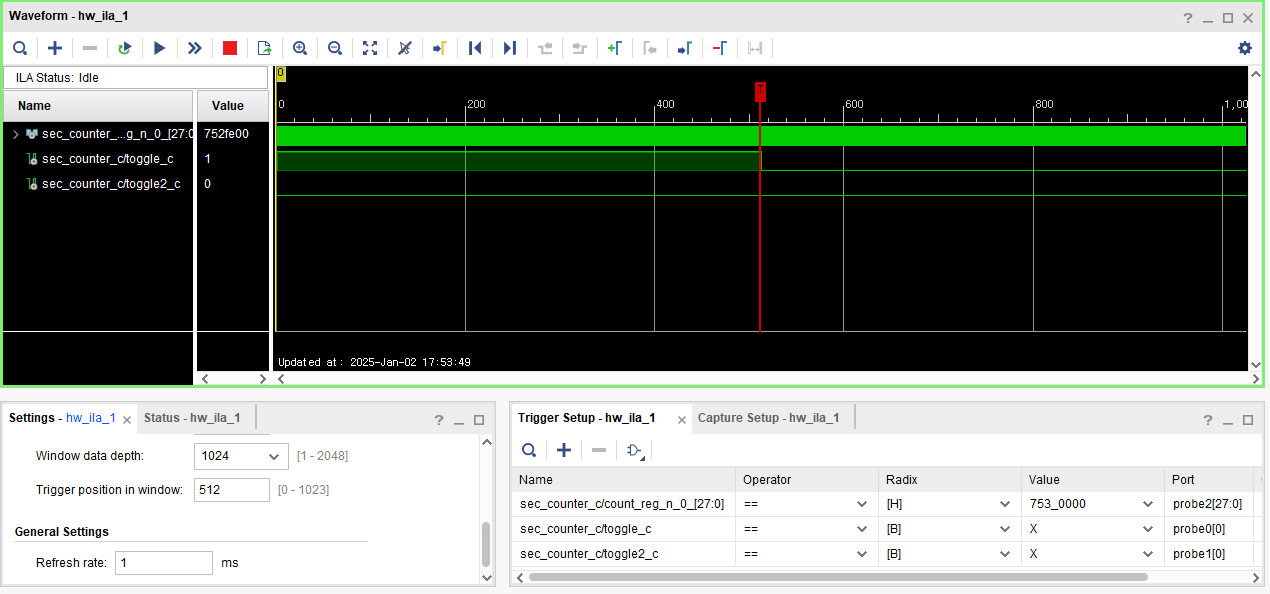

파형 좌측 : 선택한 프로브 이름(IP 프로브와 모듈의 신호와 연결되어있음)

좌 하단

- window data depth : 신호의 길이(IP 설정창에서 선택한것이 최대 길이이고, 줄이는것 가능)

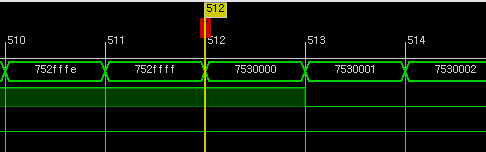

- trigger position in window : 트리거 위치(트리거를 기준으로 원하는 신호가 표현되는데 window data depth를 기준으로 어느 위치에 표시될 것인지를 정함)

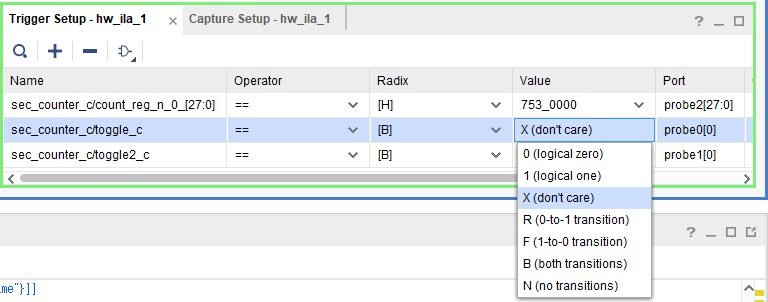

우 하단 : 트리거 결정(value탭을 기준으로 reg는 저장된 값, 비트 신호는 상승엣지 또는 하강 엣지 등을 트리거로 결정할 수 있다. (기준으로 하지 않을때는 don't care 선택))

simulation은 시간에 따른 클락의 진행 정도에 따라 순차적으로 보여주지만

ILA는 동작하고 있는 보드와 실시간 연동되어 보여지기 때문에 다음번 순서의 신호가 나오는 예상과 다르게 나올 수 있기때문에 조건식에 따른 정확한 신호값을 알고 있을때 유용할것이라고 생각된다.

예를 들어 if(a = 16'h753_0000)일때 led = ~led 이라는 토글되는 모듈을 만들었을때 a가 해당값이 될때 신호가 토글되는지를 확인하는 것 (그렇기 때문에 바로 다음번에 켜지는 순서이지만 ILA실행 창의 Run을 눌렀을때 보드의 led가 꺼지는 타이밍 이였다면 꺼지는 신호로 표시되는 것)