Vivado

1.implementation 합성 - black box 에러

저장경로에 소스코드가 있다해도 비바도에서 합성시 따로 인스턴스, 하위모듈을 불러와야한다 그렇게하면 소스코드 목록에서 ?표시가 사라진다

2.pin assignment

vivado에서 entity의 입출력포트 생성sythesis - open synthesized design - 우상단의 i/o planning - 하단 i/o port - package pin - i/o std 설정

3.Report Utilization

SYNTHESI - Report Utilization에서Utilization탭에서 좌측 Summary에서 이용가능한것 중에서 사용한 LUT, 플립플롭, I/O PLL등의 정보를 볼 수 있다.

4.실행시 log, jou 파일 생성X

vivado를 실행시킬때마다 생기는 log, jou파일을 생성되지 않게 하기 위한 방법메모장에작성후 확장자 .reg로 변경또는Try below:1\. Open command prompt.2\. Browse to location C:\\Xilinx\\Vivado\\201

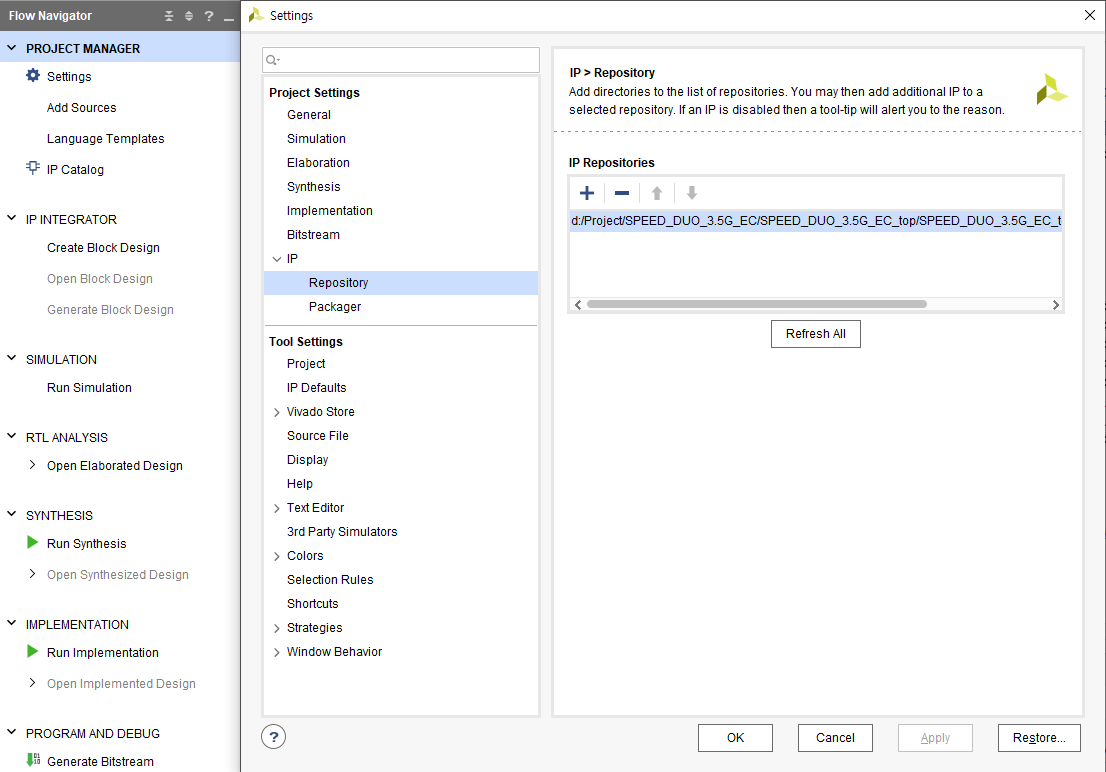

5.IP 추가

vivado 맨 좌측 메뉴에서settings -> IP -> Repository에 IP가 들어있는 폴더 경로 추가

6.Block Memory Generator (IP)

other options - .coe 파일 추가Block Memory Generator IP는 메모리 관련 IP, Ram과 Rom을 선택 가능Rom은 읽기 전용으로 최초에 읽을 데이터를 한번 써줘야 하는데 이것을 .coe 파일로 초기화 한다

7.Slack

요구된 시간(필요한 시간)과 실제 도달 시간(실제 신호가 도달하는 시간) 간의 차이를 나타냄슬랙이 양수(Positive Slack)일 경우: 신호가 요구된 시간보다 더 빨리 도달하는 경우로, 타이밍 제약을 만족하며 여유가 있는 상태.슬랙이 음수(Negative Slac

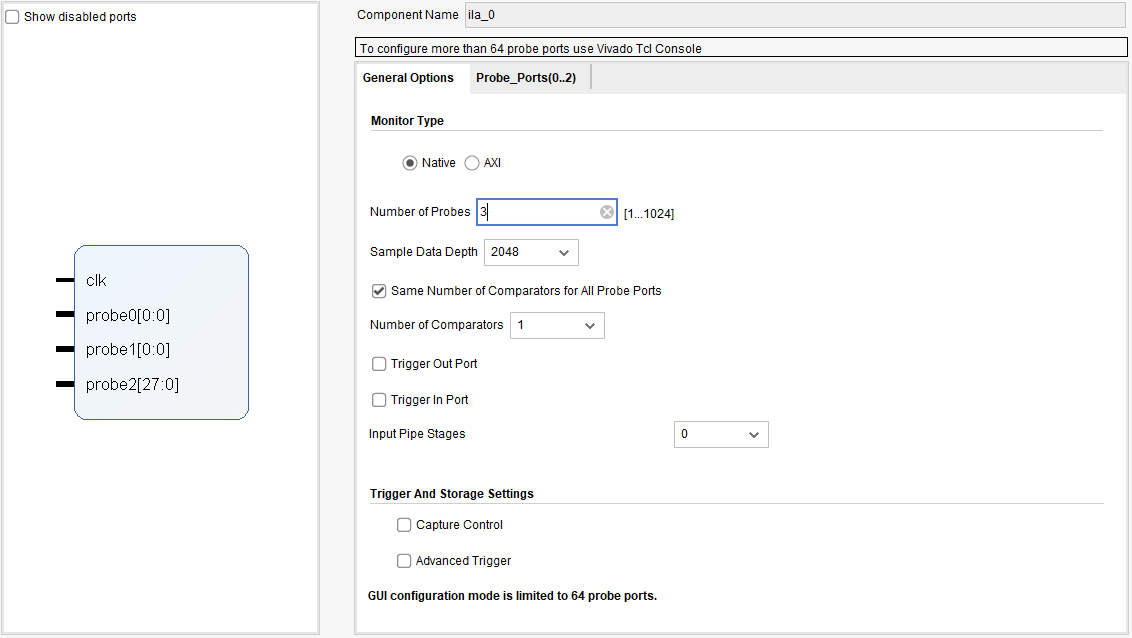

8.ILA

(IP 추가 방법은 카테고리 vivado의 IP추가 관련 포스팅 참조)내부 신호 추적을 위한 디버깅 IPsimulation은 만든 모듈을 사전에 시험하기위함이라면ILA는 보드에 bitstream한 다음에 동작을 확인하기 위함number of probes : 확인할 신호

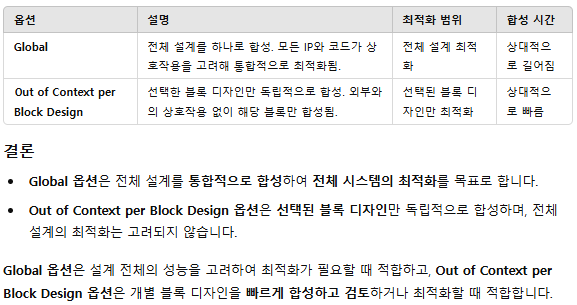

9.IP합성시 Synthesise Options

synthesise options에는 Global, Out of context per IP, Out of context per Block Design이 있다Global : 전체 설계(모든 IP와 사용자 코드)가 하나의 통합된 설계로 합성, 설계를 전체적으로 최적화Out

10.Block Design - AXI 주소 크기 조절

Address Editor 탭에서 크기 조절

11.모듈간 신호 할당시 주의

이렇게 TB에서 module로 연결되어 A값을 B에 할당한 신호가 있을때 B로 사용된 신호(조건문에 들어간다던가)를 변경하고 싶을 때 B에 값을 넣는 것이 아니라A값을 변경 해야 한다.

12.입력 clock과 clock xdc

xdc파일에 create clock을 통해 외부에서 들어오는 클럭을 정의할때, 이 신호를 모듈 안의 clock_wiz의 입력으로 사용하고 있다면 clock_wiz의 xdc파일에서 들어온 신호를 정의 하고 있기때문에 Top모듈의 xdc에서 정의한것과 중복되게 된다따라서

13.xdc파일에서 설정할 수 있는 것

14.VITIS사용하여 PL로직 교체

비트스트림 진행비트스트림 진행 후export hardware비트스트림 파일 포함하여 선택저장경로는 (project).srcs폴더에.xsa파일로 생성Workspace 경로를 (project).sw임의로 만든 폴더임 열기경고는 x눌러서 끔프로젝트 clean 진행캐쉬들 초기

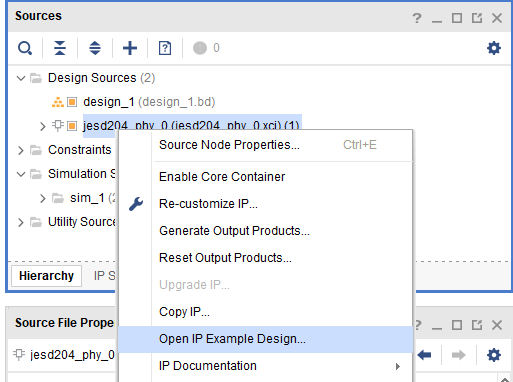

15.IP사용시 예제 얻는 법

IP를 일단 하나 생성한뒤

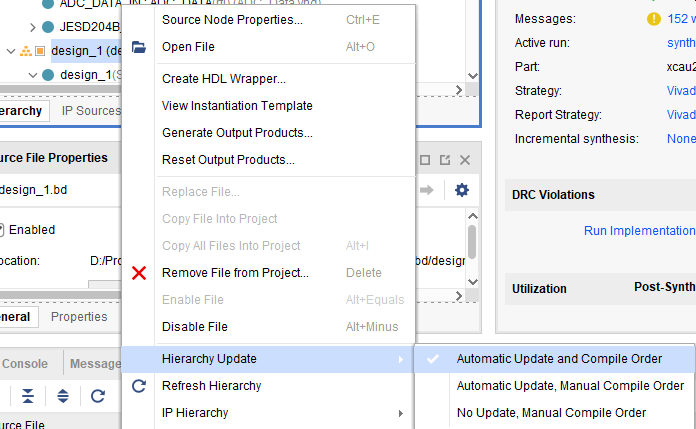

16.block design 옮기기

블럭디자인 공유하려면 .bd파일 옮겨라