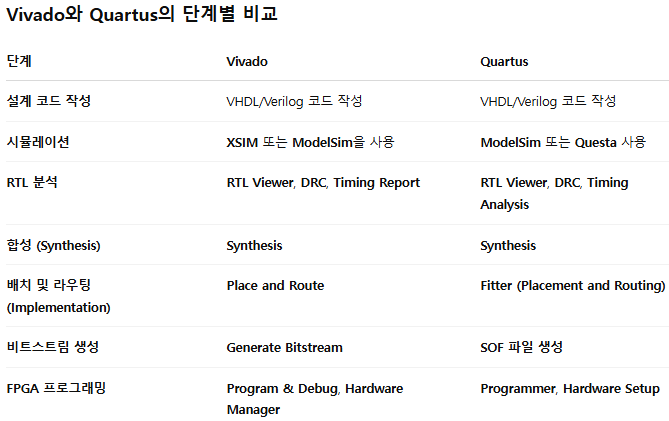

코드 작성 => 시뮬레이션 (실제 FPGA 내부에 디지털 회로로 합서하여 시뮬레이션 하는 것은 시간이 오래 걸리기 때문에 단순히 코드가 잘 되는지 빠르게 시뮬레이션하는 것) => synthesis(합성), netlist를 만든다, 코드로 있었던 것을 실제 디지털 회로로 구현하는 것이다 => implementation, 실제로 target FPGA에 디지털 회로를 배치하고 배선하게 되며 이를 place & route라고 한다 (Quartus에서는 fitter)

Vivado에서의 과정

설계 코드 작성 (VHDL/Verilog)

Vivado에서는 설계 코드 작성이 VHDL이나 Verilog로 진행됩니다. 새로운 프로젝트를 생성한 후, 이들 HDL로 설계 코드를 작성합니다.

시뮬레이션 (Simulation)

Vivado는 XSIM이라는 기본 시뮬레이터를 제공합니다. 또한 ModelSim과 같은 외부 툴도 사용할 수 있습니다.

Vivado Simulation을 통해 테스트 벤치를 작성하고 설계의 동작을 시뮬레이션하여 논리적 오류를 점검합니다.

RTL 분석 (RTL Analysis)

Vivado에서의 RTL 분석은 RTL Viewer와 Design Rule Check (DRC)를 통해 설계의 구조적 문제를 분석하고, Timing Constraints를 확인합니다.

Timing Report를 사용하여 설계가 타이밍 제약을 충족하는지 확인할 수 있습니다.

합성 (Synthesis)

Vivado의 Synthesis 단계에서 RTL 코드가 Netlist로 변환됩니다. 이때, Vivado는 설계를 FPGA 하드웨어 자원에 맞게 최적화합니다.

Synthesis Report를 통해 합성 결과를 확인하고, 자원 사용량, 타이밍, 오류 등을 점검할 수 있습니다.

구현 (Implementation)

Vivado에서의 Implementation 과정은 Place and Route 단계로 구성됩니다.

Place: 합성된 논리 소자를 FPGA의 자원에 배치합니다.

Route: 배치된 자원 간의 신호 연결을 최적화합니다.

Implementation Report에서 배치와 라우팅 결과를 확인하고, 필요한 경우 Timing Constraints를 조정하여 성능을 최적화합니다.

비트스트림 생성 (Bitstream Generation)

Vivado에서 비트스트림 파일을 생성하는 과정은 Generate Bitstream입니다. 비트스트림 파일 (.bit)을 생성하여 FPGA에 로드할 수 있도록 준비합니다.

FPGA 프로그래밍 (Programming)

Program & Debug를 사용하여 FPGA에 비트스트림 파일을 다운로드하고, 하드웨어에서 설계를 실행합니다.

Hardware Manager를 통해 FPGA에 비트스트림을 다운로드하고 디버깅을 할 수 있습니다.

Quartus에서의 과정

설계 코드 작성 (VHDL/Verilog)

Quartus에서도 VHDL, Verilog 등을 사용하여 설계 코드를 작성합니다. 새로운 프로젝트를 생성한 후, 이들 HDL로 설계 코드를 작성합니다.

시뮬레이션 (Simulation)

Quartus에서는 시뮬레이션을 위해 ModelSim 또는 Questa와 통합된 Simulation 도구를 사용할 수 있습니다.

Simulation을 통해 설계의 동작을 검증하고, 논리적 오류를 찾아냅니다.

RTL 분석 (RTL Analysis)

RTL Viewer를 통해 설계의 구조를 시각적으로 분석할 수 있습니다.

Design Rule Check (DRC)를 통해 설계 규칙을 점검하고, Timing Analysis를 통해 타이밍 제약을 확인합니다.

합성 (Synthesis)

Synthesis 단계에서는 RTL 코드를 Netlist로 변환합니다. Quartus는 이 과정을 통해 설계를 FPGA에 최적화된 논리 블록과 연결로 변환합니다.

Synthesis Report에서는 자원 사용량, 오류, 경고 등을 확인할 수 있습니다.

Fitter (Placement and Routing)

Fitter는 Placement와 Routing을 수행하는 과정입니다. 이 단계에서 Placement는 논리 소자를 FPGA의 자원에 배치하고, Routing은 그들 간의 연결을 최적화합니다.

Fitter는 설계의 성능을 최적화하고, 타이밍 요구 사항을 충족하는지 확인하는 중요한 단계입니다.

Fitter Report에서는 자원의 배치 및 라우팅 상태와 타이밍 분석 결과를 제공합니다.

비트스트림 생성 (Programming File Generation)

SOF (SRAM Object File) 파일을 생성하는 과정입니다. 이 파일은 FPGA에 프로그래밍할 수 있는 최종 비트스트림 파일입니다.

Convert Programming Files를 사용하여 필요한 파일 형식으로 변환할 수 있습니다.

FPGA 프로그래밍 (Programming)

Programmer를 사용하여 FPGA에 SOF 파일을 다운로드하고 설계를 실행합니다.

Hardware Setup을 통해 FPGA와 연결하고, Programmer를 사용하여 비트스트림을 다운로드합니다.

Vivado, Quartus