용어정리

1.용어정리

주파수 변환기피드백 구조와 증폭기를 이용하여 원하는 주파수로 주기적 파형 생성입력신호화 출력신호에서 되먹임된 신호와의 위상차를 이용해 출력신호를 제어출력신호의 주파수 조절이 목적입출력 신호의 위상차를 검출하여 입력전압 조절위상차가 동기되면 잠금상태인덕터의 일종이라고 볼

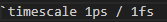

2.용어정리2

변조(modulation)란 보내고자 하는 정보 신호를 가지고 반송파(carrier)의 진폭, 주파수 및 위상을 변화시키는 것으로 정보 신호의 주파수 spectrum을 높은 쪽으로 옮기는 조작진폭 변화 변조방식주파수 변화 변조방식위상 변화 변조방식진폭과 위상을 같이 변

3.timescale

사용 기본 단위 / 최대 표현 단위

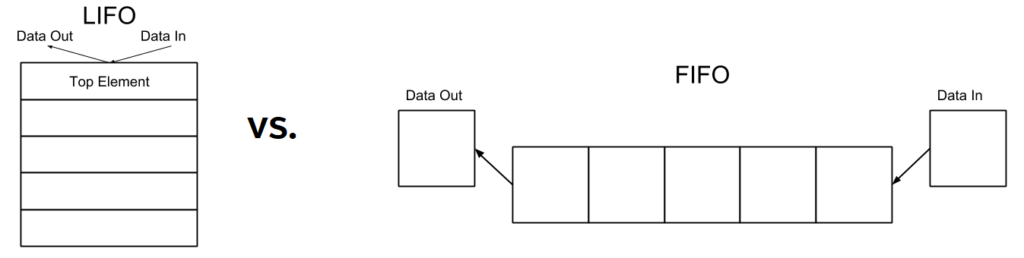

4.FIFO

First In First Out선입선출FIFO의 장점 중 하나는 단순성입니다. 이해하고 구현하기 쉬우므로 다양한 시나리오에서 널리 사용됩니다. 또한 FIFO는 데이터나 작업이 수신되는 순서를 보장하기 때문에 데이터나 작업을 처리할 때 공정성을 보장합니다. 또한 작업이

5.FFT에 의한 주파수 shift

원래의 주파수 신호 𝑥(𝑡)임의의 주파수 신호 cos(2𝜋𝑓LO𝑡) //(LO : Local Oscillator)시간 도메인 𝑦(𝑡)=𝑥(𝑡)⋅cos(2𝜋𝑓LO𝑡) ==FFT==> 주파수 도메인 Y(f)={1/2}{X(f−fLO)+X(f+fLO)}

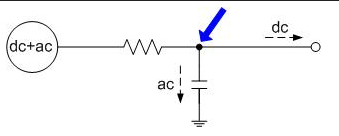

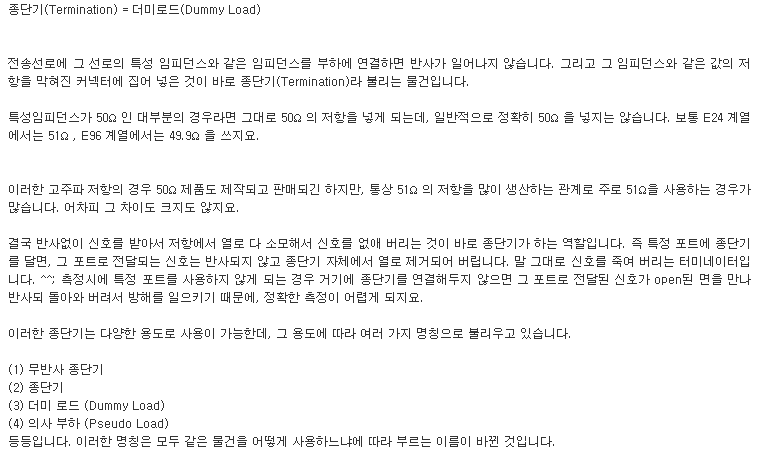

6.용어정리3

1. 텀

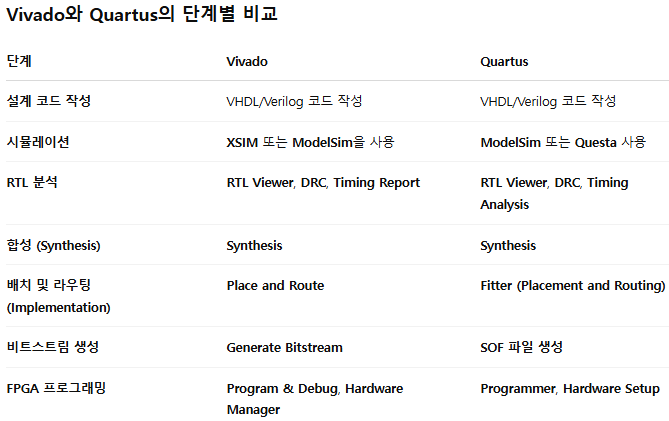

7.합성 과정

코드 작성 => 시뮬레이션 (실제 FPGA 내부에 디지털 회로로 합서하여 시뮬레이션 하는 것은 시간이 오래 걸리기 때문에 단순히 코드가 잘 되는지 빠르게 시뮬레이션하는 것) => synthesis(합성), netlist를 만든다, 코드로 있었던 것을 실제 디지털 회로로

8.clock source & sink

https://m.blog.naver.com/gc_na/223006131343clock source : 출력clock sink : 받는 곳