system verilog 문법 정리

interface: 여러 module간에 공통신호를 공유하여 사용 가능하게 함.

- 여러 신호를 하나의 단위로 그룹화(캡슐화)하여 모듈 간에 전달 가능

- 코드 재사용성, port 연결 단순화에 유리

interface adder_if(input logic clk);

logic [31:0]a;

logic [31:0]b;

logic [31:]result;

endinterface

- interface를 여러 module에서 사용할 때 in,out을 다르게 설정할 수 있음

- interface.modport a; 형태로 불러옴

interface adder_if(input logic clk);

logic [31:0]a;

logic [31:0]b;

logic [31:]result;

//port 선언

modport MASTER(input a,input b, output result);

modport SLAVE(input result, output a, output b);

endinterface

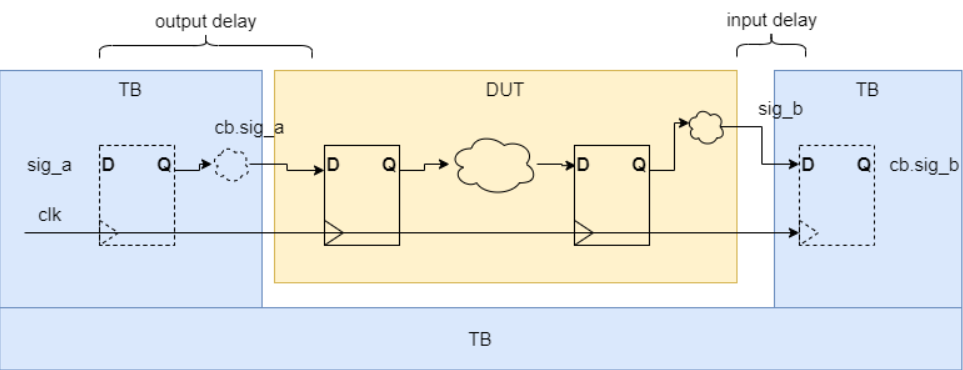

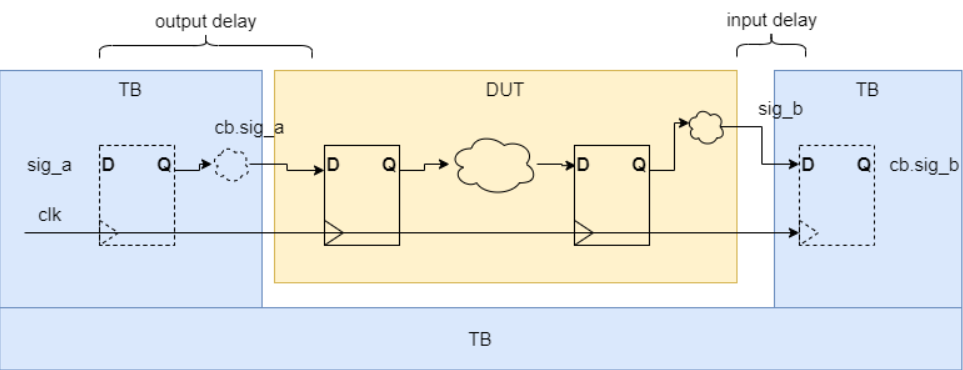

clocking block: signal의 값 변경을 정확히 clock edge에 동기화될 수 있게함.

- testbench에서 사용

- clk의 rising edge와 동기화 되어있음.

- clocking block의 output은 DUT의 input방향

- clocking block의 input은 DUT의 output방향

//interface 선언

interface adder_if(input logic clk);

logic [31:0]a;

logic [31:0]b;

logic [31:0]result;

modport MASTER(input a, input b, output result);

endinterface

//Design module

module adder(adder_if.MASTER add); //interface 불러오기

always @(posedge add.clk)

add.result <= add.a + add.b;

endmodule

//test bench

module top;

logic clk;

adder_if add_vif(clk); //adder_if interface 불러오기

adder u_adder(.add(add_vif)); //adder module 불러오기

initial begin

clk = 0;

forever #5 clk = ~clk;

end

initial begin

//clocking block 정의

clocking cb @(posedge clk);

input add_vif.result; //tb기준 input, DUT기준 output

output add_vif.a, add_vif.b; //tb기준 input, DUT기준 output

endclocking

cb.a <= 0;

cb.b <= 0;

#7;

cb.a <= 5; //posedge clk에서만 값이 변하므로 15일 때 a 값이 5가 됨.

end

endmodule

task, function

- 코드의 반복을 줄이기 위해 사용.

- interface내에서 subroutines(task,function) 정의 가능

- interface와 연결된 module에서 정의된 것을 사용 가능

//interface 선언

interface adder_if(input logic clk);

logic [31:0]a,b;

logic [31:0]result;

//task 선언

task calc(

input logic [31:0]a,b;

output logic [31:0]result

);

begin

result = a+b;

end

endtask: calculation

endinterface: adder_if

//Design module

module adder(adder_if a); //interface 불러옴

always @(posedge a.clk)

a.calc(a.a, a.b, a.result); //adder_if.calc를 불러옴

endmodule