논리회로 구조

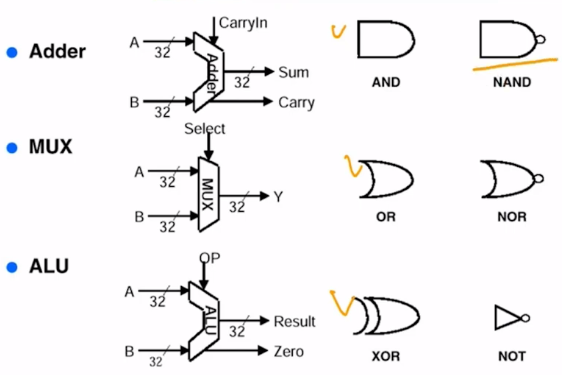

- Combinational 구조

입력이 같으면 -> 출력이 같다.

ex) and or nor ..

- Sequential 구조

입력이 같아도 -> 경우에 따라 다른 출력이 나올 수 있다.

=> 왜냐하면 이 구조에는 Combianitonal 구조에는 없는 메모리 구조가 있기 때문이다.

이 메모리 내부에 상태라는 것이 있으며, 외부에서 들어오는 것가 이 상태가 결합하여 다시 외부로 출력한다. 따라서 동일한 input이라도 다른 output을 낼 수 있는 것이다.

ex) 레지스터 렛지 등

이 순차적 구조는 다시 두 가지로 분류될 수 있다.

2.1 Asynchronous : Clock이 없는 순차회로

2.2 Synchronous : Clock이 있는 순차회로

순차회로에는 어떤 상태라는 값이 메모리에 저장되어 있다.

이 상태가 언제 바뀌느냐가 굉장히 중요한데, 이 상태의 변화를 clock이라는 외부신호를 통해 상태가 언제 바뀔지를 일괄적으로 정해준다. 이것이 동기적 순차회로라고 한다.

이 clock신호에 rising falling edge를 기준으로 회로의 상태를 한 번에 업데이트 한다.

순차회로의 핵심은 메모리라고 할 수 있다.

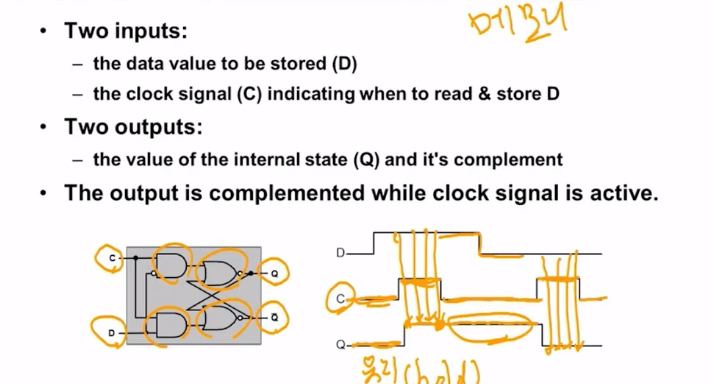

그리고 이 메모리의 가장 단순한 형태가 D-latch이다.

- D-latch

D-latch는 and gate와 nor gate로 이루어져 있으며, C와 D라는 데이터 신호 입력과 Q과 반대 Q라는 출력으로 이루어져 있다.

이 구조는 C가 0일 때는 Q가 즉, 기억하는 값이 변화하지 않는다.(과거의 기억을 유지한다. : hold)

C가 1이 될 때 D의 값이 Q로 지속적으로 업데이트 하게 된다.

다시 C가 0이 되면 그 때 부터 다시 기억하는 값이 변화하지 않고 hold한 상태로 유지된다.

이렇게 C에 따라 Q에 반영 여부를 정한다.

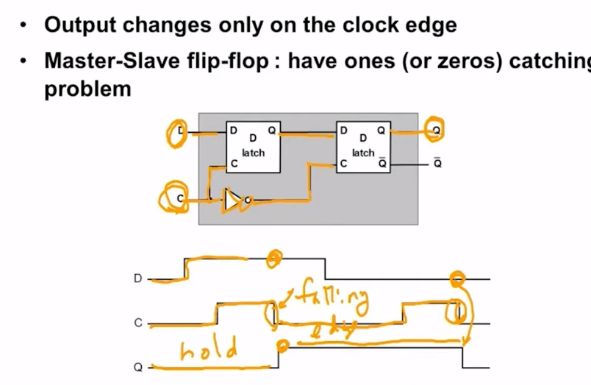

- D flip-flop (Master-Slave flip-flop)

D-latch를 직렬로 두 개 이어 붙인 것을 말하며, D-latch보다는 복잡하지만 제일 잘 쓰인다.

이제는 clock의 값의 여부가 아니라 clock신호의 변화 여부에 따라 업데이트를 진행하게 된다.

이 D flip-flop은 falling과 rising을 기준으로 변화 여부를 결정할 수 있는데, 떨어지는 것을 기준으로 한다면 falling edge를 기준으로 아래와 같이 업데이트 여부를 결정하게 된다.

나머지의 영역에서는 모두 변화하지 않게 되는 것이다. 이를 falling edge trigger D F/F 이라고 하며, 반대는 rising edge trigger D F/F 이라고 한다.

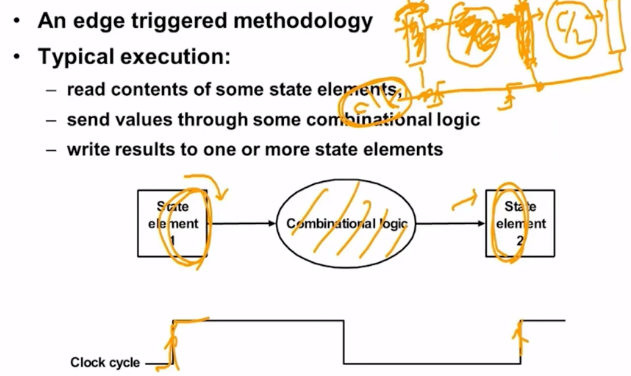

이번에는 일반적인 디지털 시스템을 살펴보자.

입력을 받아서 저장하는 레지스터가 있고, 이 레지스터의 출력을 받아서 계산을 진행하는 조합회로가 있다. 이를 다시 레지스터가 저장하고 다시 조합회로에 보내고 이러한 구조로 순차회로가 구성된다.

여기서 레스터들은 모두 같은 clock을 기준으로 한다.

예를 들어 rising edge를 기준으로 한다면 C의 rising edge부분에서 레지스터에 업데이트가 이루어지게 되고, 이 출력이 조합 회로를 통과해서 다시 이 출력을 저장하는 register에 도착하고, 일정한 시간이 머무른 후에 두 번째 clock의 이벤트가 발생하면 조합회로의 출력값이 두 번째 레지스터에 저장이 되는 것이다!

이와 같이 global clock을 통해 레지스터에 저장할 시점을 정해준다.

이와 같이 한 레지스터에서 값이 저장되고, 조합회로에서 값을 읽어 들여서 계산 후 다시 레지스터에 저장하는데, 이를 한 clock 주기가 걸린다고 했다.

따라서 이 동작을 빨리 하려면 clock 주기가 짧을 수록 회로의 업데이트가 빠르게 일어난다.

즉, clock의 frequency와 회로의 속도는 정비례하게 된다.이렇게 회로의 속도를 빠르게 하는 것이 컴퓨터의 성능을 높이는 것이기에 좋다고 할 수 있지만, 어쩔 수 없이 어느 정도까지만 가능한 huddle이 존재한다. 새로운 데이터가 들어와 계산을 마치고 다음 레지스터에 저장하는 데에는 한계가 있기에 당연하다.