컴퓨터구조 및 설계

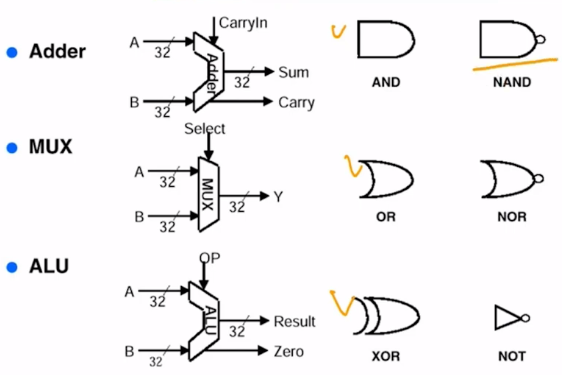

1.컴퓨터 구조 및 설계 - 논리 회로

Combinational 구조입력이 같으면 -> 출력이 같다.ex) and or nor ..Sequential 구조입력이 같아도 -> 경우에 따라 다른 출력이 나올 수 있다.=> 왜냐하면 이 구조에는 Combianitonal 구조에는 없는 메모리 구조가 있기 때문이다.

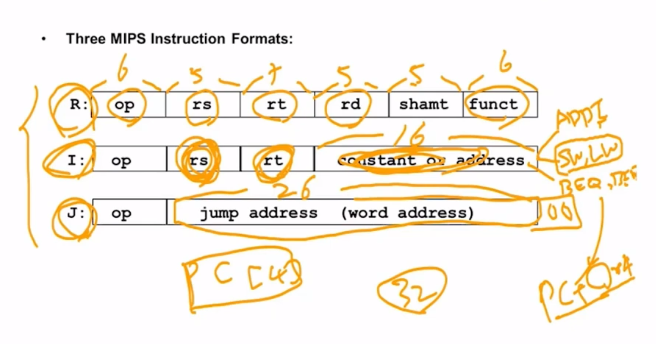

2.컴퓨터 구조 및 설계 - MIPS instruction format

MIPS instruction은 세 가지의 format형태를 가진다.R formatop코드(6비트)와 funct코드(6비트)로 어떤 연산을 진행하는 지 결정한다.rs, rt, rd, shamt(shift) : 각각 5비트I format피연산자 중에 레지스터 값이 아닌

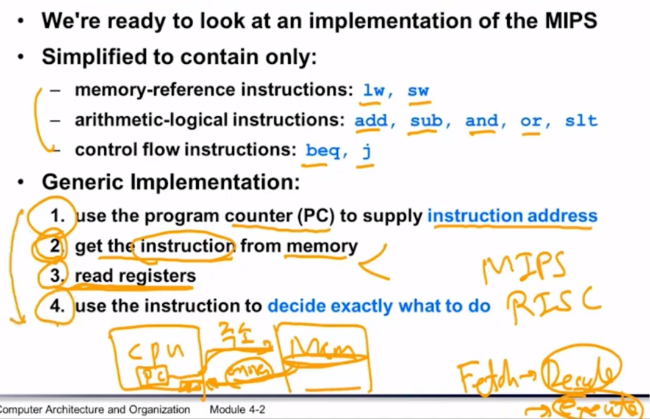

3.컴퓨터 구조 및 설계 - 명령어 별 마이크로 동작 분석

가장 basic한 path : 한 clock사이클 내에 모든 명령어가 끝난다.를 가정하고 진행해 보자. 이를 single clock cycle CPU라고 한다.지금부터 고려할 instruciton들은1) memory-reference instruciton : lw(lo

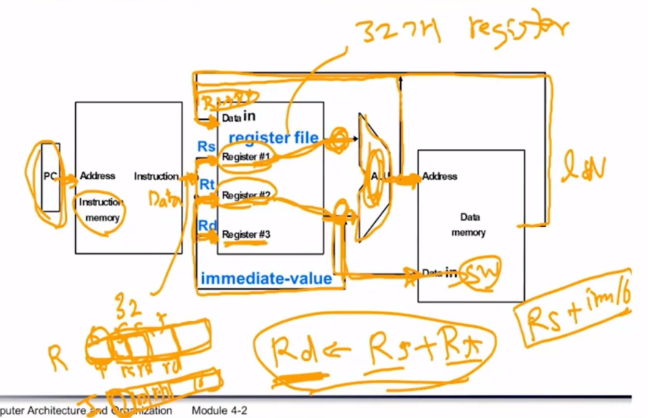

4.컴퓨터 구조 및 설계 - Simple Datapath

실제 하드웨어를 한 번 설계해 보자!PC가 있고, PC의 값을 주소로 하여 Instruction memory에 들어가게 된다.Instruction memory에서 나오는 address가 정해지면 그 위치에 있는 데이터가 나오며, 이 데이터가 instruction(32비

5.컴퓨터 구조 및 설계 - Datapath 구현을 위한 빌딩블록들

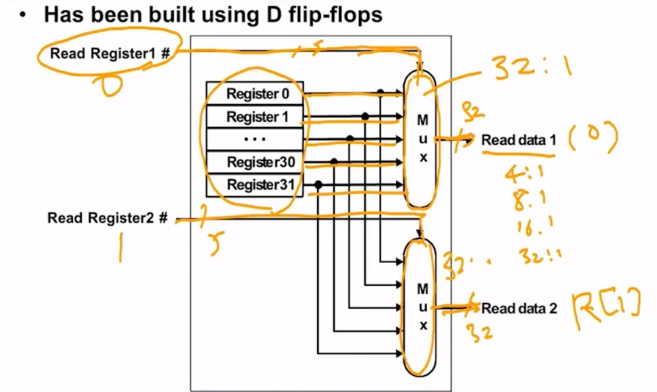

저번 포스터에서 전반적인 흐름을 살펴보았다.이 Datapath를 구성하기 위해 각각을 자세하게 한 번 살펴보자.Register File BlockRegister File은 32개의 레지스터가 들어가 있다.그리고 각각의 레지스터는 MIPS이기에 32bit가 된다.우선 레

6.컴퓨터 구조 및 설계 - 명령어별 Single Cycle Datapath 설계

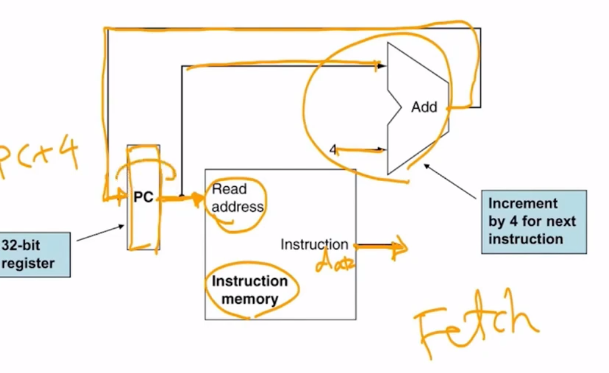

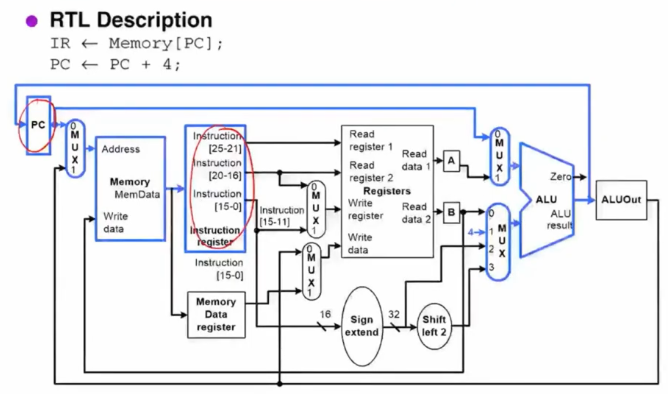

우선 Fetch만을 생각해 봤을 때, 어떤 연결이 필요한지 살펴보자.PC의 출력을 isntruction memory의 address port에 연결하여 isntruction memory에서 instruction(data)를 출력한다.위의 부분은 다음 clock cycl

7.컴퓨터 구조 및 설계 - Single Cycle 제어부

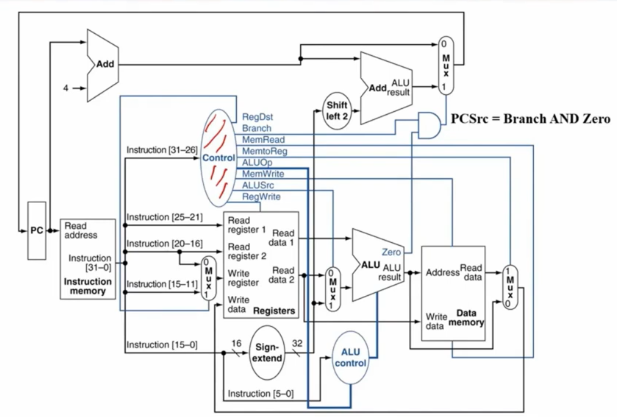

이제는 Single Cycle을 다루기 위한 제어부들을 한 번 살펴보자.control 신호들이 있는데, 우선 1) 레지스터에 필요한 읽기 쓰기 신호가 있고 2) Mux의 select 신호 3) 메모리의 읽기 쓰기 신호 4) ALU의 연산 5) branch여부에 대한 b

8.컴퓨터 구조 및 설계 - Multiple Clock Cycle

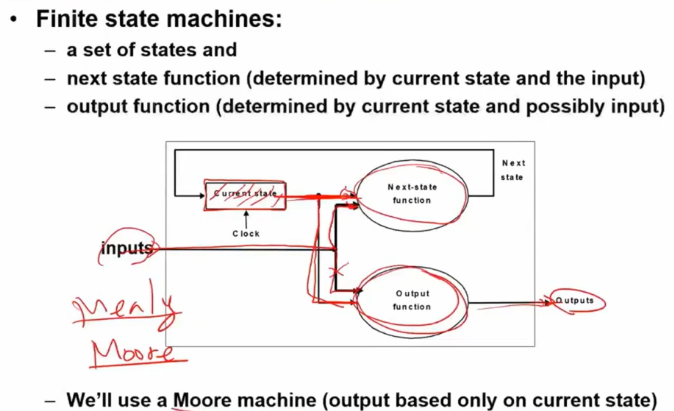

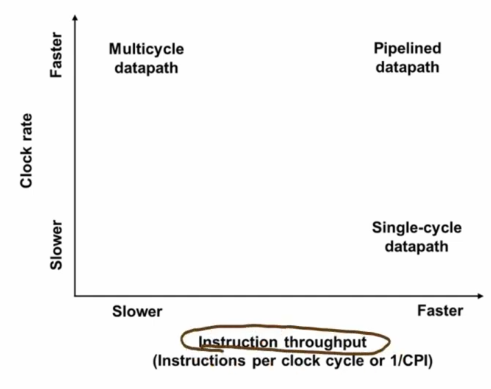

지금까지 Single Clock Cycle을 알아봤다.이는 한 clock cycle 안에 모든 작업을 수행해야 하기에 한 clock cycle의 주기가 굉장히 길었다는 단점이 있었다. 또한 한 번에 수행해야 하기에 ALU가 있음에도 add연산기가 추가적으로 필요했고,

9.컴퓨터 구조 및 설계 - 명령어별 Multiple Clock Cycle 실행

전반적인 step을 한 번 살펴보자!Instruction FetchInstruction Decode and Register FetchExecution, Memory Address Computation, or Branch CompletionMemory Access or

10.컴퓨터 구조 및 설계 - Pipeline

Pipeline 지금까지 Single Cycle과 Multiple Cycle에 대해서 알아 보았다. 이제는 이들의 장점들을 결합한 Pipeline에 대해 알아보자! CPU설계의 대부분은 Pipelining설계로 이루어져 있다. 이것을 쓰는 목적은 CPU의 성능을

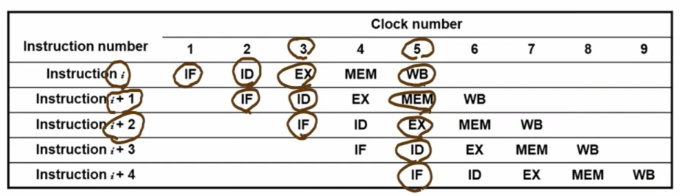

11.컴퓨터 구조 및 설계 - Pipeline Datapath, Control

저번 포스터에서 아래와 같이 파이프라이닝을 함으로 빠른 진행을 할 수 있었음을 확인했다.5개의 instruction이 각기 다른 stage에 동시에 머무를 수 있었다.이 때 다섯 가지의 stage로 나누었는데, 각각의 다른 하드웨어를 사용한다.주의할 점은 서로 섞이지

12.컴퓨터 구조 및 설계 - Pipeline Hazards : Data Hazard

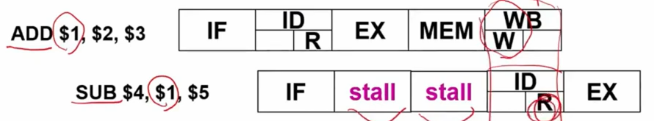

Pipeline의 Hazards는 세 가지 종류가 있었다.1) Structure hazard2) Data hazard3) Control hazard이 중에서 Data hazard는 언제 생길지에 대해 살펴보자.Data hazard는 data 간의 dependency가

13.컴퓨터 구조 및 설계 - Pipeline Hazards : Control Hazard

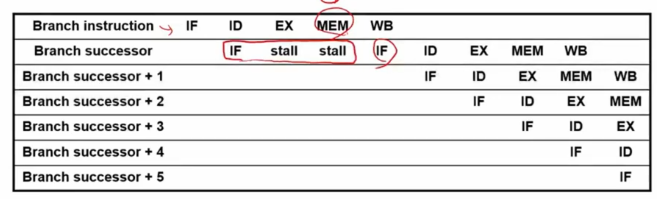

이번에는 Control Hazard에 대해 알아보자.이를 해결하는 방법은 총 네 가지가 있다.1) Stall2) Optimized branch processing3) Branch prediction4) Delayed branch1)의 stall은 앞의 data haza

14.컴퓨터 구조 및 설계 - Memory Hierarchy 1(메모리 계층구조)

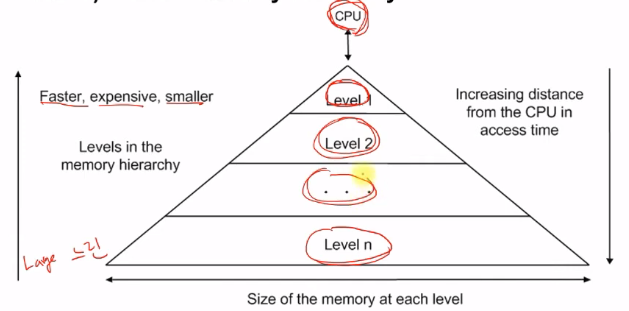

명령어를 빨리 실행하는 만큼 다음 빠르게 공급되어야 하는데, 메모리에서 CPU로 전달되는 속도가 bottel neck이 되는 현상이 지속되고 있다.이로 인해 빠른 CPU보다는 빠른 메모리의 요구가 대두되고 있다.메모리 계층구조에서 알아볼 내용은 크게 아래와 같다.1\.

15.컴퓨터 구조 및 설계 - Memory Hierarchy 2(메모리 계층구조)

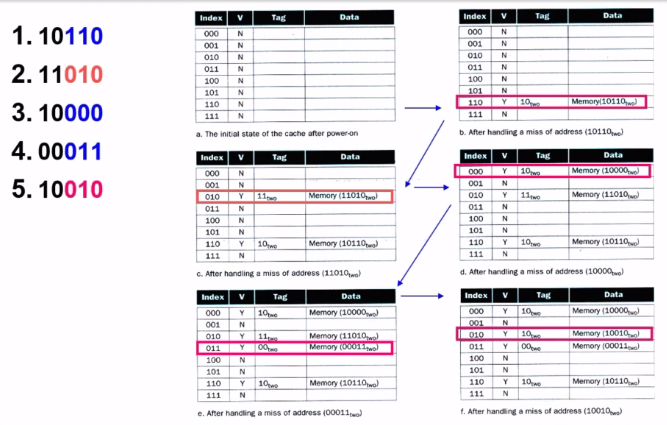

메모리 상단부의 Cache memory에 대해 알아보자!2\. Basics of cache\-Direct mapped cache operation\-Handling cache misses\-Write PolicyCache를 바라볼 때, 우리가 궁금해 하는 점이 두 가지