명령어별 Single Cycle Datapath 설계

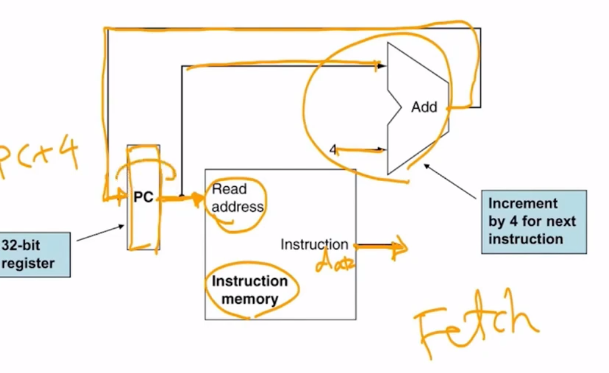

우선 Fetch만을 생각해 봤을 때, 어떤 연결이 필요한지 살펴보자.

PC의 출력을 isntruction memory의 address port에 연결하여 isntruction memory에서 instruction(data)를 출력한다.

위의 부분은 다음 clock cycle로 넘어갔을 때, 수행할 다음 명령어를 가져오기 위해 +4를 미리 동시에 하는 것이다.

다음으로 Fetch가 끝이 나서 instruction이 출력된 상황을 보자.

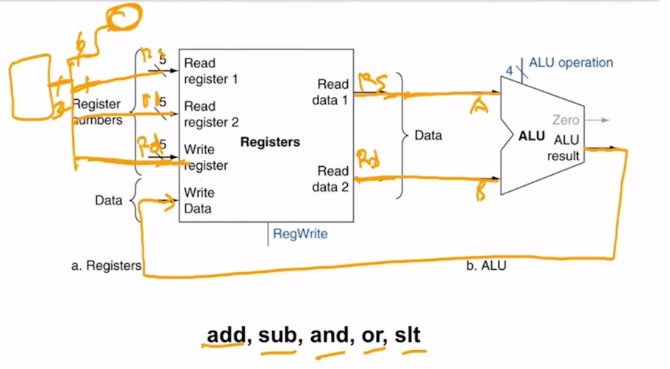

나온 instruction 32비트 짜리를 6(op코드로 어딘가의 제어부로 간다) 5(rs read register1) 5(rt read register2) 5(rd write register) 로 할당되며,

rs에서 나오는 read data1과 rd에서 나오는 read data2가 출력이 된다. 이 둘을 add, sub, and, or, slt등의 작업을 수행하기 위해 ALU의 A와 B port에 연결해준다.

여기서 나온 ALU result는 다시 write data입력으로 들어간다. 어디에 데이터를 저장할 지는 정해진 write data rd에 저장된다.

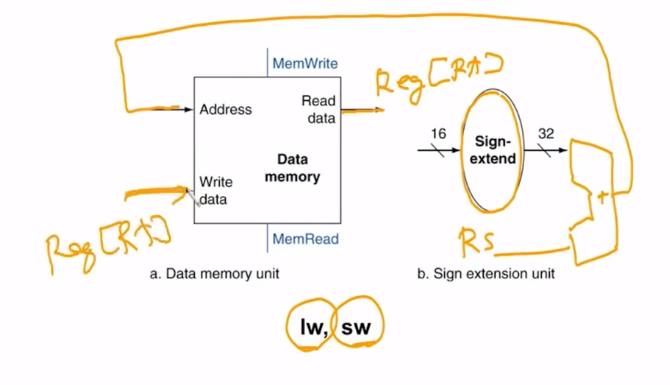

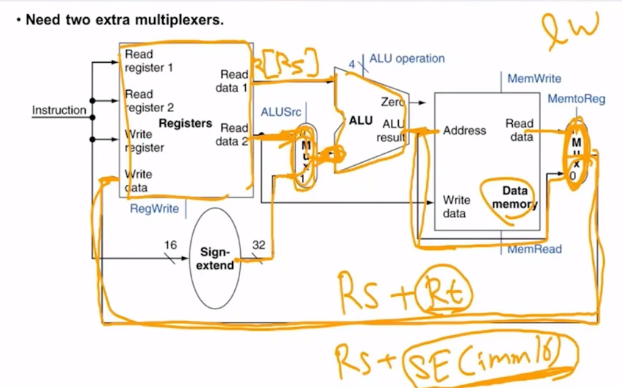

이번에는 load store memory를 살펴보자.

이를 수행하기 위해서는 data memory가 꼭 필요하다고 했다.

또한 주소를 계산하기 위한 sign extension이 있다.

Sign extension과 Rs에서 ALU에 들어가 그 결과가 address에 들어간다.

lw 명령어의 경우는 read data에서 나온 것이 R[rt]로 연결되고,

sw 명령어의 경우는 write data에 R[rt]로 연결되어 들어간다.

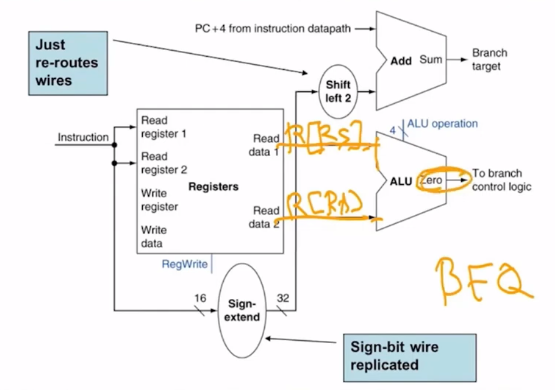

다음으로 beq의 경우는 R[rs]와 R[rt]의 값을 비교하여 빼서 0이면 branch를 수행한다.

아래는 R-type에 load와 store를 할 수 있게 만들어 본 것이다.

이제는 R[Rs]가 Rt와 결합하여 ALU로 들어가기도 하고, SE(immd16)과 결합하여 ALU에 들어가기도 한다.

=> 그렇기에 Mux을 통해 0과 1로 조정해주는 부분이 생겼다. (당연히 이를 제어해주는 제어 신호가 추가된다.)

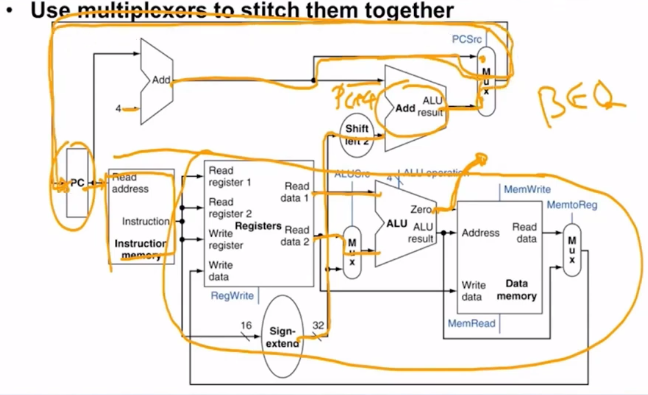

여기에 Branch명령어까지 추가하면 아래와 같다.

rs와 rt값을 ALU에서 비교하여 branch여부를 결정하고,

branch판단이 없으면 위에서 그냥 PC+4를 target주소로 하여 보내고,

branch 판단이 되면 PC+4에서 SignExtension에서 나온 16비트상수값을 더함으로 target주소를 계산하여 PC+4 대신 이 값을 보내게 된다.

이 모든 것들이 한 clock cycle에 진행된다. 즉 PC와 register file이 업데이트 되는데 하나의 clock을 통해 진행된다.