- mode shift register

1. module 생성

module shift_reg(DATAOUT, MODE, clk, rst, DATAIN);

input [1:0] MODE;

input clk, rst;

input [3:0] DATAIN;

output reg [3:0] DATAOUT;

always @(posedge clk)

begin

if (rst)

DATAOUT <= 0;

else

begin

case(MODE)

2'b00 : DATAOUT <= DATAOUT;

2'b01 : DATAOUT <= {DATAIN[0], DATAOUT[3:1]};

2'b10 : DATAOUT <= {DATAOUT[2:0], DATAIN[0]};

2'b11 : DATAOUT <= DATAIN;

endcase

end

end

endmodule

2. testbench 생성

`include "shift_reg.v"

`timescale 1ns/1ps

module shift_reg_tb;

reg clk, rst;

reg [3:0] DATAIN;

reg [1:0] MODE;

wire [3:0] DATAOUT;

shift_reg shift(.DATAOUT(DATAOUT), .MODE(MODE), .clk(clk), .rst(rst), .DATAIN(DATAIN));

initial

begin

clk =0; MODE = 2'b00; DATAIN = 4'b0000;

rst = 1; #10; rst = 0; #10;

$display("RSLT\tD == DOUT");

// Start testing Right Shift mode

MODE = 2'b00; rst = 1; #10; rst = 0; #10;

MODE = 2'b01; DATAIN = 4'b0011; #10;

// Start testing Left Shift mode

MODE = 2'b00; rst = 1; #10; rst = 0; #10;

MODE = 2'b10; DATAIN = 4'b0111; #10;

// Start testing parallel load mode

MODE = 2'b00; rst = 1; #10; rst = 0; #10;

MODE = 2'b11; DATAIN = 4'b1010; #10;

#20;

$finish;

end

always #5 clk = ~clk;

initial begin

$dumpfile("shift_reg_tb.vcd");

$dumpvars(0, shift_reg_tb);

end

endmodule

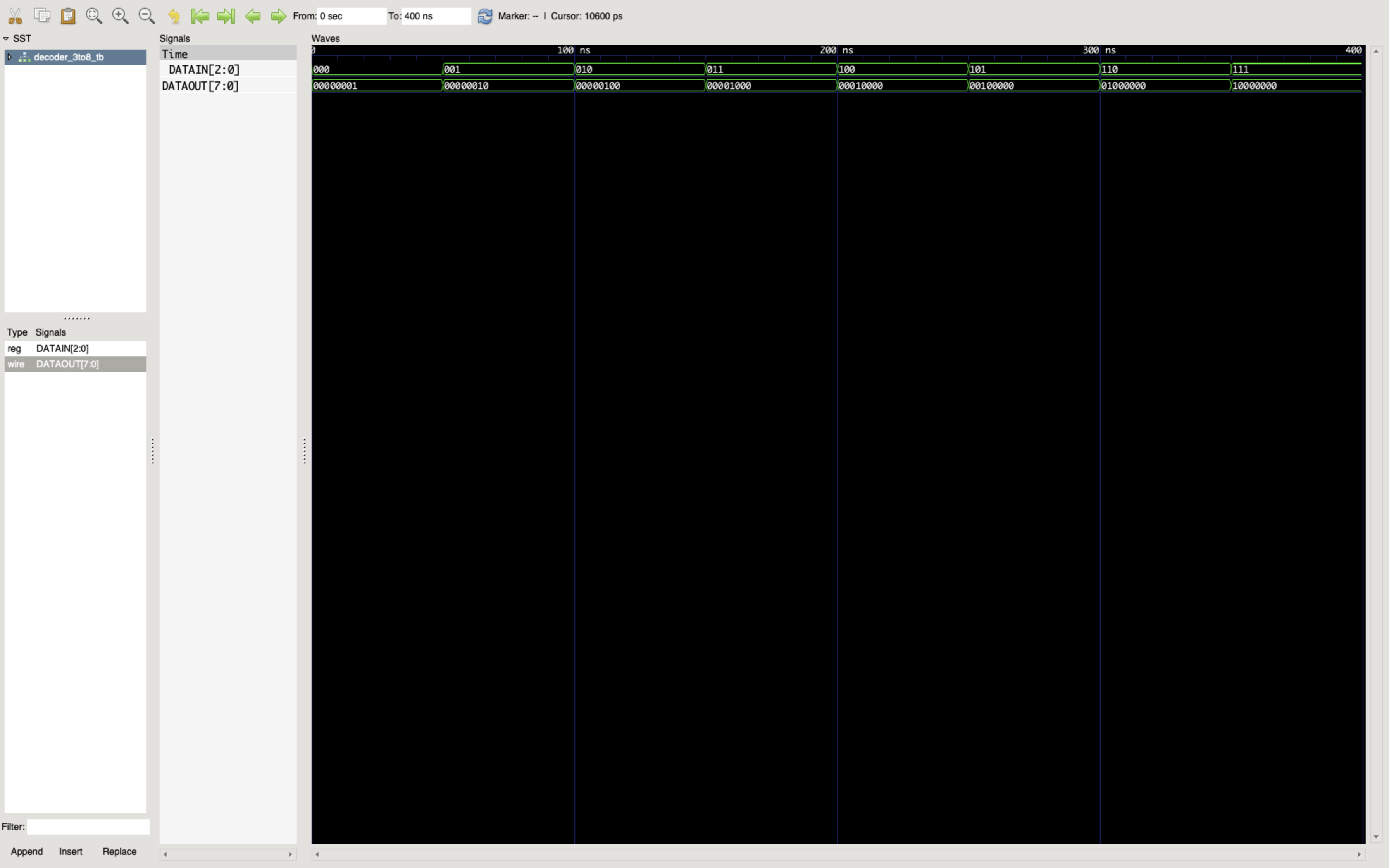

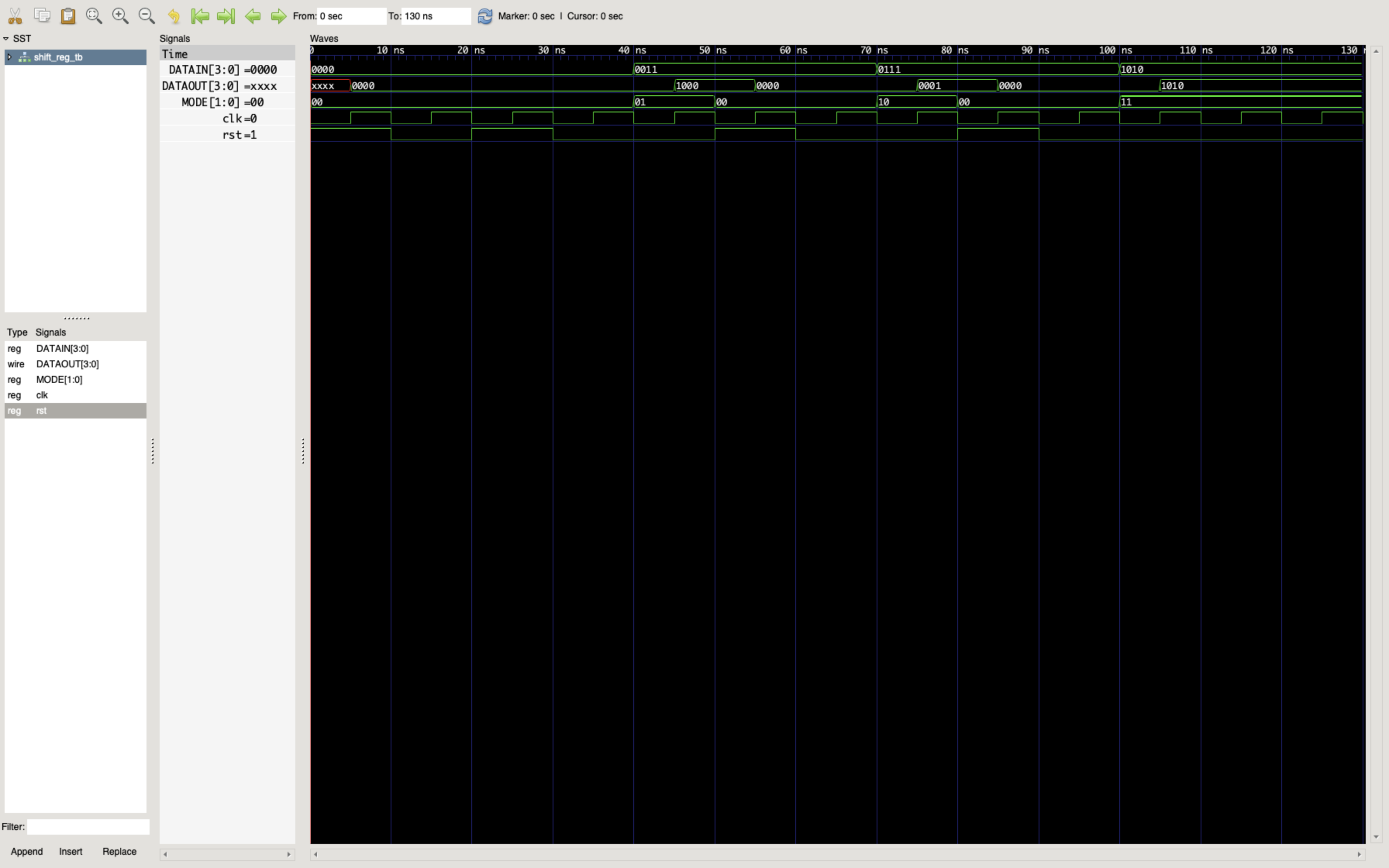

3. 결과 파형 확인

- 8 to 3 encoder

1. module 생성

module encoder_8to3(en, i, y);

input en;

input [8:0] i;

output reg[2:0] y;

always @(en, i)

begin

if(en == 1)

begin

if(i[7] == 1) y = 3'b111;

else if(i[6] == 1) y = 3'b110;

else if(i[5] == 1) y = 3'b101;

else if(i[4] == 1) y = 3'b100;

else if(i[3] == 1) y = 3'b011;

else if(i[2] == 1) y = 3'b010;

else if(i[1] == 1) y = 3'b001;

else if(i[0] == 1) y = 3'b000;

end

else y = 3'bzzz;

end

endmodule

2. testbench 생성

`include "encoder.v"

`timescale 1ns/1ps

module encoder_8to3_tb;

reg [8:0] i;

reg en;

wire [2:0] y;

encoder_8to3 enc(.en(en), .i(i), .y(y));

initial begin

en = 0;

#10;

en = 1;

i = 8'b00000001;

#10;

en = 1;

i = 8'b00001000;

#10;

en = 1;

i = 8'b00010000;

#10;

en = 1;

i = 8'b10000000;

$finish;

end

initial begin

$dumpfile("encoder_8to3_tb.vcd");

$dumpvars(0, encoder_8to3_tb);

end

endmodule

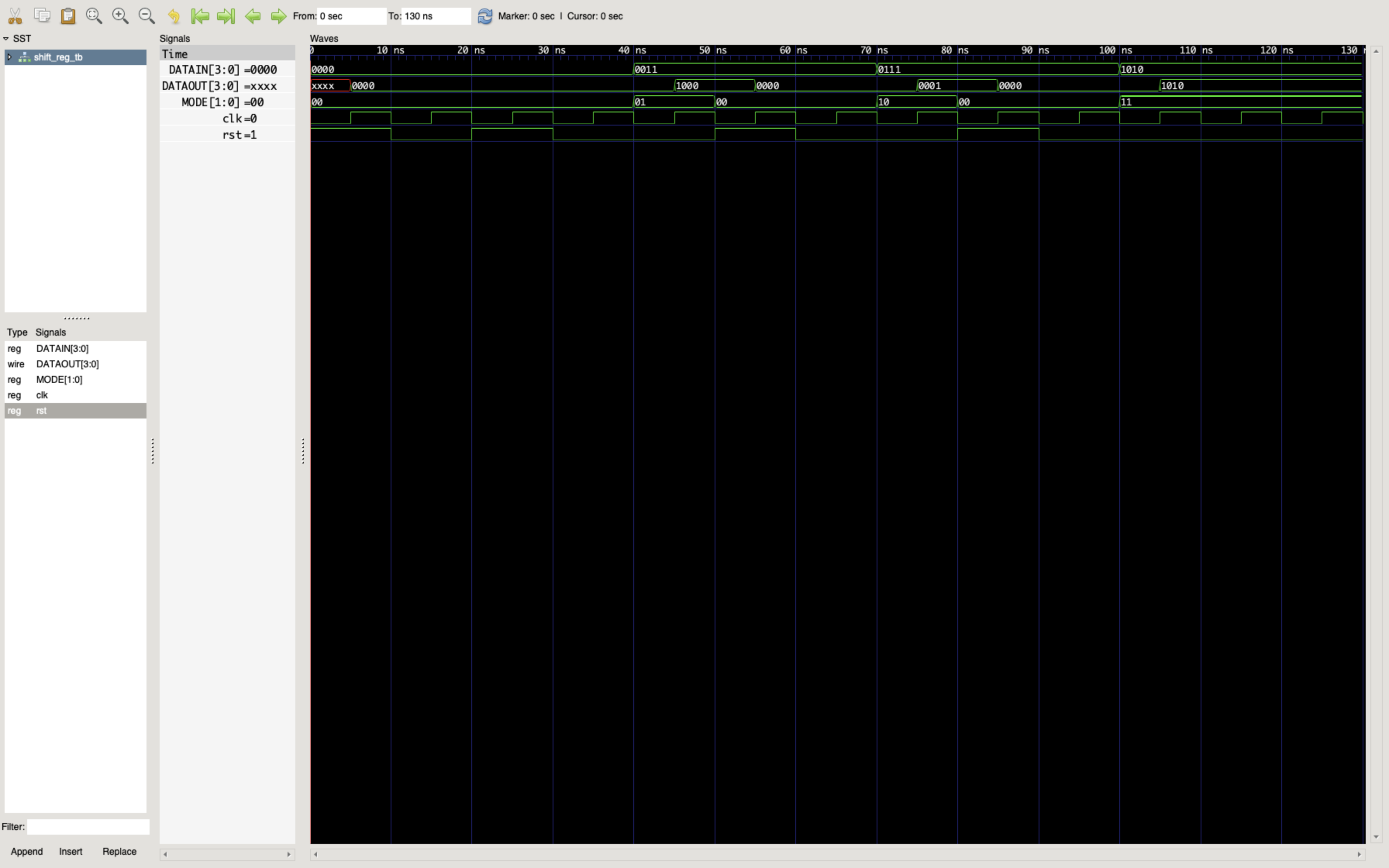

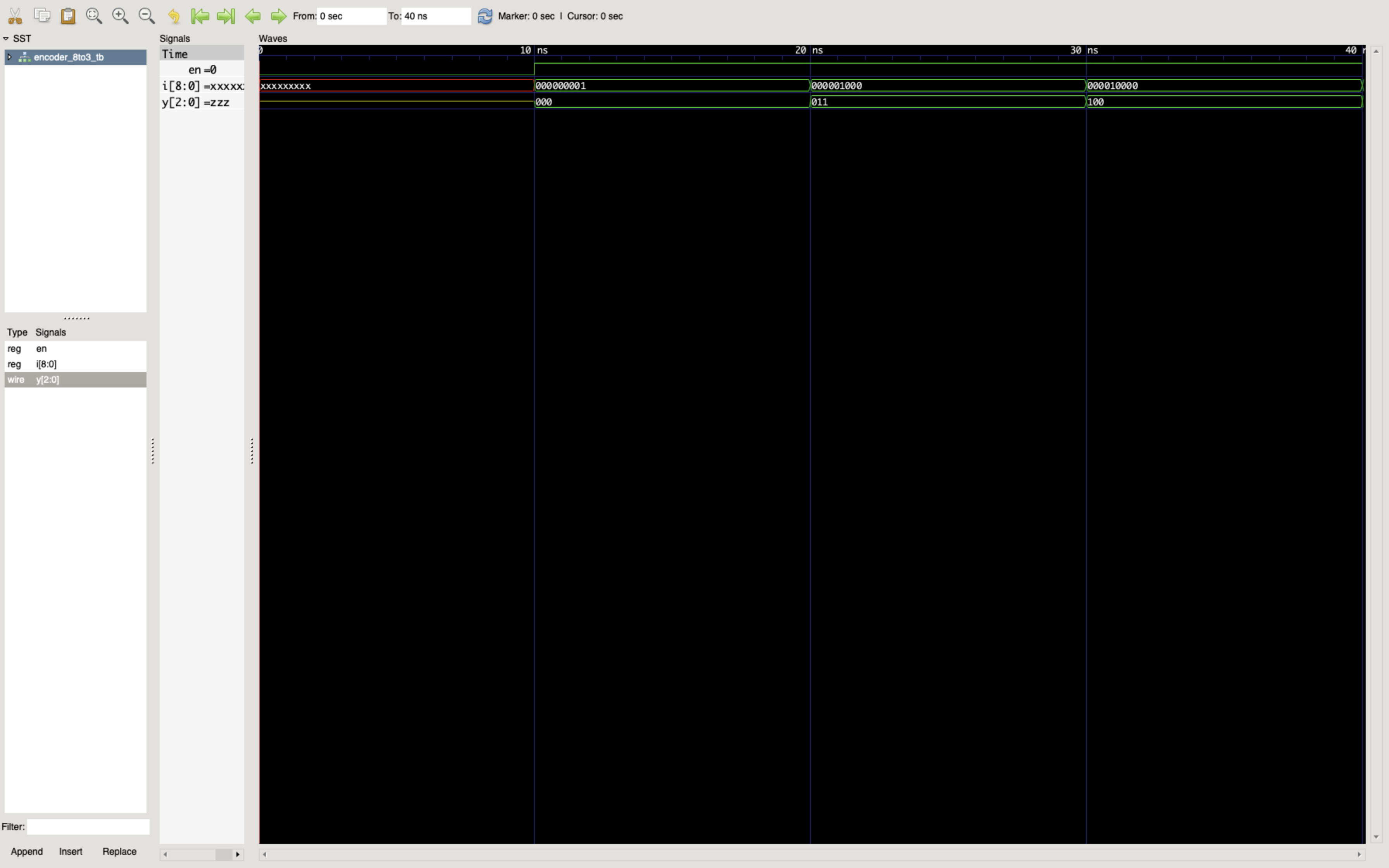

3. 결과 파형 확인

- 3 to 8 decoder

1. module 생성

module decoder_3to8(DATAIN, DATAOUT);

input [2:0] DATAIN;

output reg [7:0] DATAOUT;

always @(DATAIN)

case(DATAIN)

3'b000 : DATAOUT = 8'b00000001;

3'b001 : DATAOUT = 8'b00000010;

3'b010 : DATAOUT = 8'b00000100;

3'b011 : DATAOUT = 8'b00001000;

3'b100 : DATAOUT = 8'b00010000;

3'b101 : DATAOUT = 8'b00100000;

3'b110 : DATAOUT = 8'b01000000;

3'b111 : DATAOUT = 8'b10000000;

default : DATAOUT = 8'b00000000;

endcase

endmodule

2. testbench 생성

`include "decoder.v"

`timescale 1ns/1ps

module decoder_3to8_tb;

reg [2:0] DATAIN;

wire [7:0] DATAOUT;

decoder_3to8 dec(.DATAIN(DATAIN), .DATAOUT(DATAOUT));

initial begin

DATAIN = 3'b000; #50;

DATAIN = 3'b001; #50;

DATAIN = 3'b010; #50;

DATAIN = 3'b011; #50;

DATAIN = 3'b100; #50;

DATAIN = 3'b101; #50;

DATAIN = 3'b110; #50;

DATAIN = 3'b111; #50;

end

initial begin

$dumpfile("decoder_3to8.vcd");

$dumpvars(0, decoder_3to8_tb);

end

endmodule

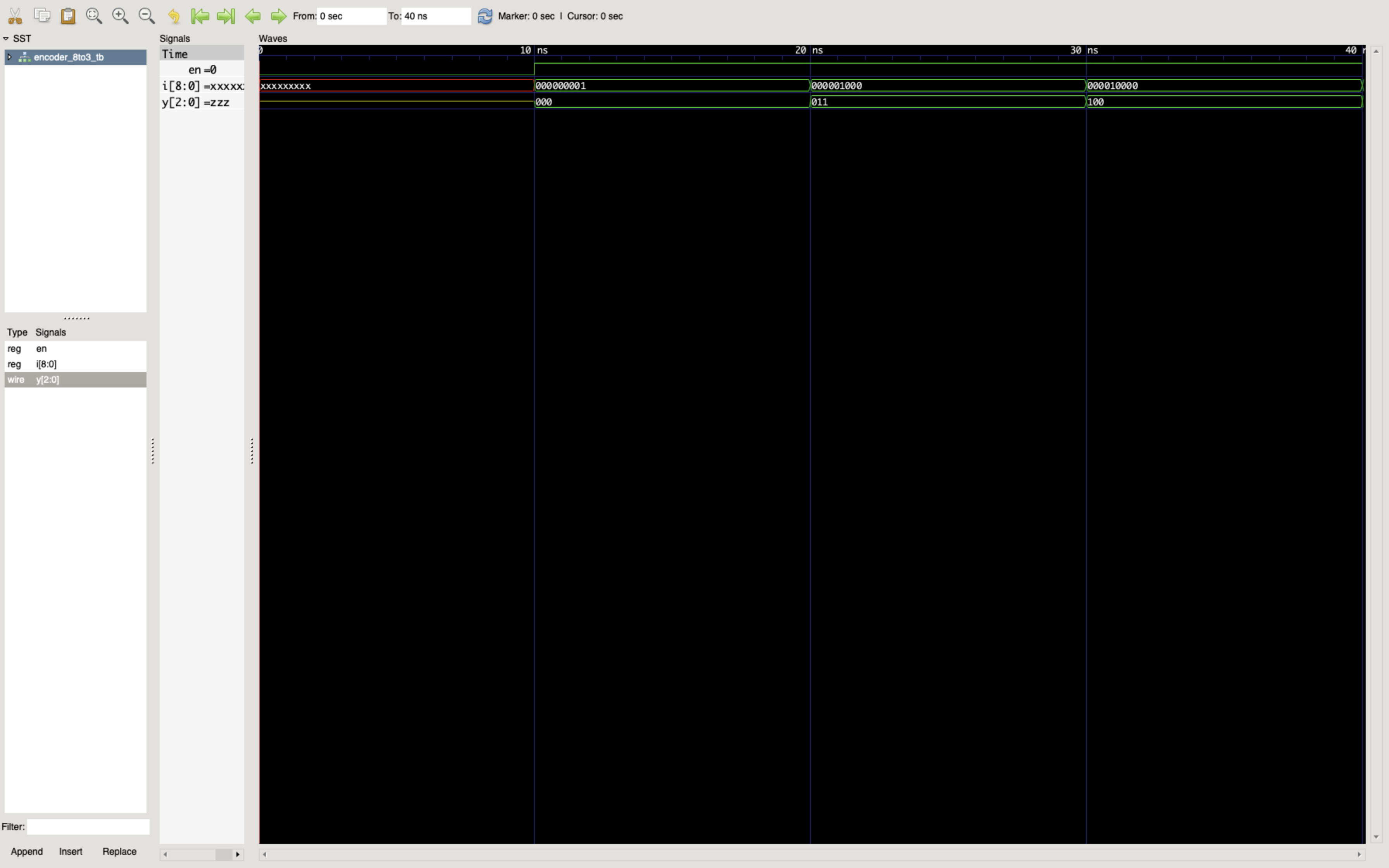

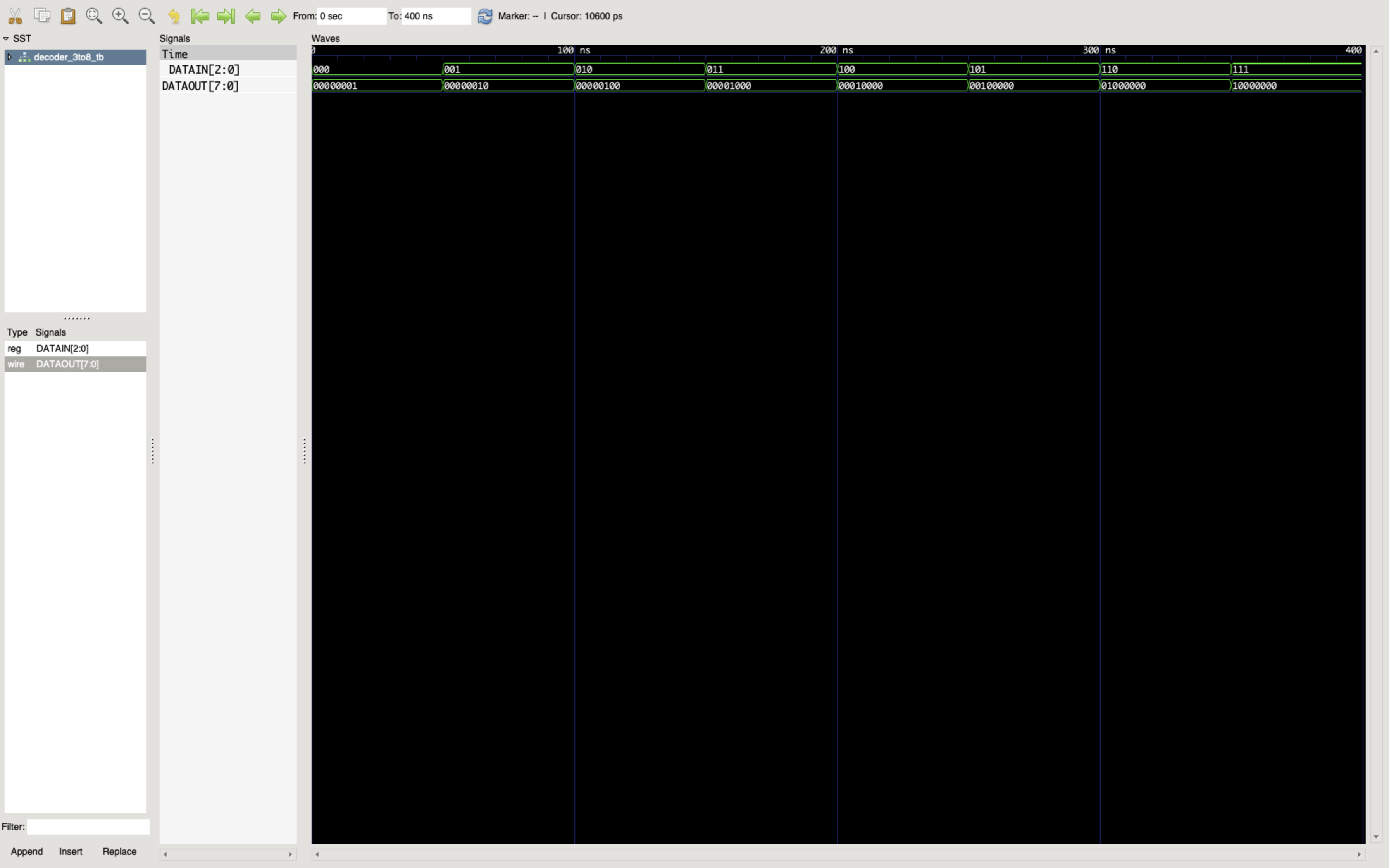

3. 결과 파형 확인