🤷♀️Make가 필요한 이유?

GCC 컴파일러를 활용해 컴파일을 하게되면, 매번 여러 명령어를 치는 귀찮음을 겪게 됩니다. 이런 귀찮음을 해결하고자 리눅스의 alias처럼 명령어 스크립트를 미리 저장해두고 컴파일을 자동화하

여 진행하는 툴을 make라고 합니다.

make 사용의 장점

- 각 파일에 대한 반복적 명령의 자동화로 인한 시간 절약

- 프로그램의 종속 구조를 빠르게 파악 할 수 있으며 관리가 용이

- 단순 반복 작업 및 재작성을 최소화

📁Makefile

Make를 실해하기 위해서는 프로젝트 폴더 루트 디렉토리에 Makefile이라는 파일을 만들어야 합니다. 이 파일은 Make가 어떻게 이 프로젝트를 빌드할 것인지 명시해 놓은 파일로, 정해진 문법에 맞게 작성해야 합니다.

💡예제를 통해 쉽게 이해해 보도록 합시다!!

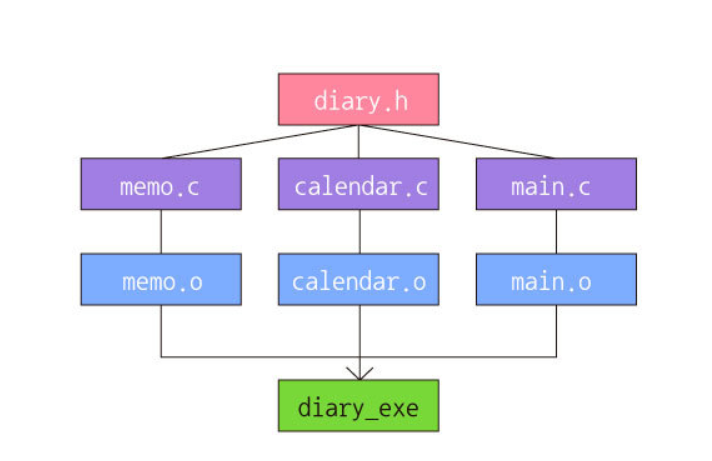

위의 관계로 diary_exe 실행 파일을 만들어 보도록 합시다.

1. c파일에서 obj파일 생성하기

gcc -c -o memo.o memo.c

gcc -c -o calendar.o calendar.c

gcc -c -o main.o main.c2.각 object파일을 묶어 컴파일을 통해 diary_exe 실행파일 생성하기

gcc -o diary_exe main.o memo.o calendar.o- 실행파일 확인

$./diary_exe만약 묶어서 컴파일 해야할 .c파일이 100개라면?!! 명령어에 100개의 파일을 모두 써주어야합니다😂

그래서 필요한 것이make와Makefile입니다!

➰Makefile의 구성

-목적파일(Target) : 명령어가 수행되어 나온 결과를 저장할 파일

-의존성(Dependency) : 목적파일을 만들기 위해 필요한 재료

-명령어(Command) : 실행 되어야 할 명령어들

-매크로(macro) : 코드를 단순화 시키기 위한 방법

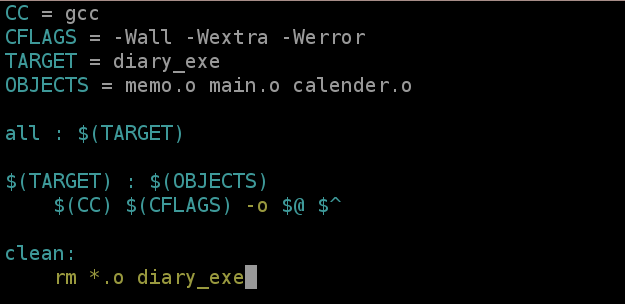

최종 Makefile입니다! 하나하나 뜯어볼까요?

최상단의 CC, CFLAGS, TARGET, OBJECTS는 매크로 정의에 해당하는 부분입니다.

💡매크로 정의 규칙

- 매크로를 참조 할 때는 소괄호나 중괄호 둘러싸고 앞에 ‘$’를 붙인다.

- 탭으로 시작해서는 안되고 , :,=,#,”” 등은 매크로 이름에 사용할 수 없다.

- 매크로는 반드시 치환될 위치보다 먼저 정의 되어야 한다.

매크로를 하나씩 살펴보면..

TARGET은 최종 목적 파일, OBJECTS는 targer을 만드는데 필요한 의존성 파일들을 의미합니다.

여기에서 특이한 기호가 눈에 띕니다.

$@, $^ 이것들을 내부 매크로라고 부릅니다.

💡내부 매크로

- "$@" : 현재 타겟의 이름

- "$^" : 현재 타겟의 종속 항목 리스트

이제 위의 코드를 해석하기 위해 알아야 할 것은 모두 알았습니다. 한 줄씩 의미를 해석하며 정리해 봅시다.

- gcc 컴파일러를 이용

- 사소한 오류까지 출력

- 최종 타겟 파일은 diary_exe

- OBJECT 로 정의할 파일들은 memo.o main.o calendar.o

- all 은 현재는 사용하지 않았지만 타겟 파일이 여러개 일때 사용됩니다.

- 타겟 파일을 만들기 위해 OBJECT 들을 사용한다.( 단 OBJECT 파일이 없다면 OBJECT 파일과 이름이 동일한 C파일을 찾아 OBJECT파일을 생성한다. )

- gcc -o diary_exe memo.o main.o calendar.o과 동일

- 더미타겟