1. Tricore란?

Tricore는 구 Siemens에서 개발한 32비트 마이크로컨트롤러 아키텍처로, 현재는 인피니언 테크놀로지스에서 개발하고 있다. 1999년에 처음 릴리즈되었고, Tricore 아키텍처는 꽤 오래된 기술이다. 이 글에서는 Tricore 아키텍처의 역사에 대해서 살펴볼 거다.

Tricore Architecture - Siemens

2024년 말 기준으로 인피니언에서 RISC-V 기반의 새로운 마이크로컨트롤러가 출시될 예정이라, Tricore는 아마 곧 역사 속으로 사라질 거다.

Tricore 아키텍처 특징 (1999 Handbook)

Tricore 아키텍처는 다음과 같은 특징이 있다.

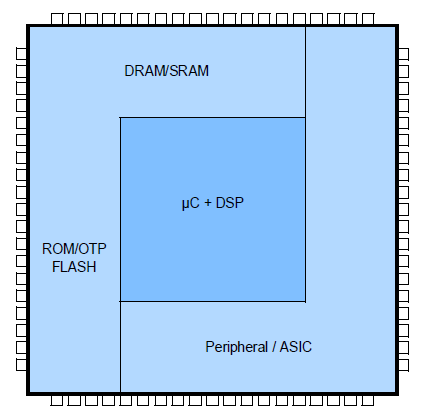

1. 마이크로컨트롤러와 DSP를 합친 구조로, 고성능 실시간 임베디드 시스템에 적합.

2. 빠른 Task Switching, 효율적인 인터럽트 처리, 고급 언어 컴파일러 지원. (1999년대에는 어셈블리어로 개발하는 마이크로컨트롤러가 많았기 때문에 C 언어 지원 자체가 큰 장점이었음)

3. 큰 용량의 On-Chip 메모리(RAM / ROM / DRAM / OTP / FLASH).

4. 빠른 Peripheral Access, OCDS 지원.

5. RISC-like한 레지스터 모델로 고급 언어 컴파일러 지원.

2. Tricore 구조

Tricore의 핵심 구조는 다음과 같다.

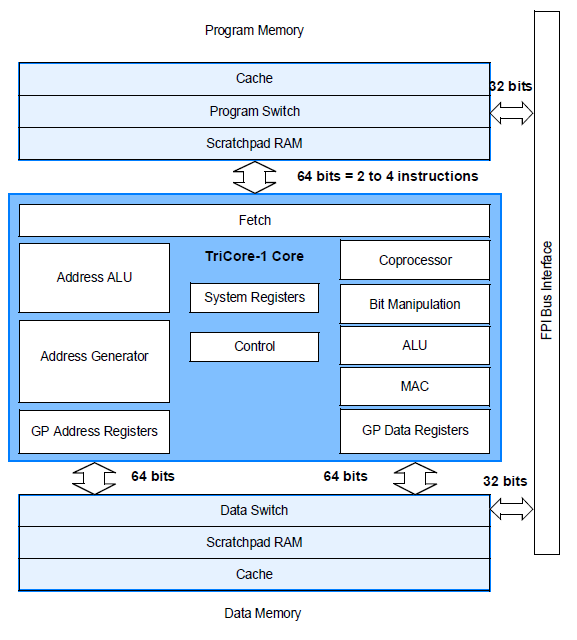

CPU Core (ALU, Control Register, GPR)와 Program Cache, RAM / Data Cache, RAM이 Flexible Peripheral Interface Bus로 연결되어 있다.

Tricore CPU Core 기본 구성

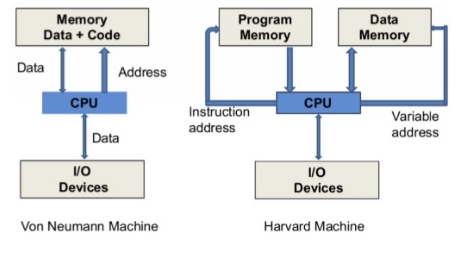

Harvard Architecture

Tricore의 CPU Core는 프로그램과 데이터 메모리 주소 및 버스가 분리된 하버드 아키텍처를 채택하고 있다. 이 구조 덕분에 instruction fetch와 data access가 병렬로 동시에 수행될 수 있다.

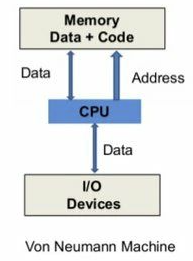

참고: 폰 노이만 및 하버드 컴퓨터 구조 차이

폰 노이만 구조 : 프로그램과 데이터가 메모리를 공유하며, CPU와 메모리 사이에 버스가 하나만 있는 간단한 구조다.

하버드 구조 : 프로그램 메모리와 데이터 메모리가 분리되어 있어, 동시에 두 가지 메모리 접근이 가능해 고속처리가 가능하다.

SuperScalar

Tricore는 슈퍼스칼라(SuperScalar) 아키텍처를 채택하여 한 클럭 사이클 내에 여러 명령어를 실행할 수 있도록 설계되었다. Tricore의 슈퍼스칼라 구조는 다음과 같다.

-

다중 파이프라인 구조

- 두 개의 주요 파이프라인이 있으며, 각 파이프라인은 4단계로 구성돼 명령어 처리 과정을 분할하여 수행한다.

- 보조 파이프라인이 하나 있어 반복문 제어를 담당한다. 반복문 관련 명령어 처리 최적화를 한다.

- 이 세 개의 파이프라인이 병렬로 동작하면서 한 클럭 사이에 세 개의 명령어가 동시에 처리된다.

-

명령어 병렬처리

- 여러 파이프라인이 동시에 작동함으로써, 독립적인 명령어들을 동시에 처리할 수 있다. 명령어 간 의존성이 없을 경우, 가능한 많은 명령어가 병렬 처리된다.

-

파이프라인 단계 효율성

- 각 파이프라인이 4단계로 나뉘어, fetch, decode, dispatch, execute의 과정을 동시에 실행한다. 루프 제어를 위한 보조 파이프라인 덕분에 병목 현상을 줄이고 전반적인 명령어 처리량을 증가시킨다.

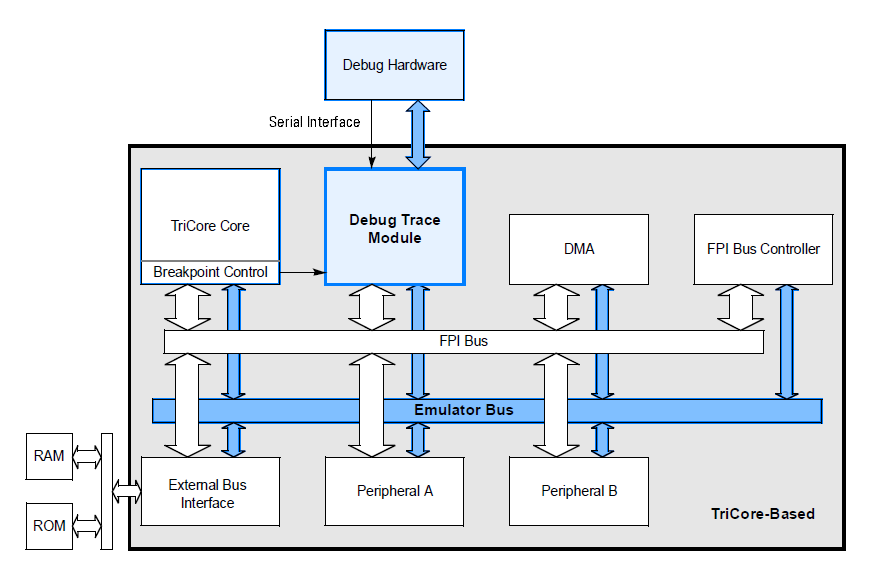

FPI Bus Interface

FPI Bus Interface는 메모리와 I/O 장치 사이에서 데이터를 주고받기 위해 설계된 데이터 버스다. 칩 안에 있는 각 블록들은 FPI Bus를 통해 연결되어 있다.

(https://velog.velcdn.com/images/lhjoon14/post/5c61fddb-9b86-4706-9d1a-bcf26e0e75b0/image.png)

Peripheral Control Processor(PCP) Module

PCP 모듈은 데이터 이동 및 조작을 위한 CPU 외의 다른 프로그래머블한 Peripheral이다. 이 Co-Processor(GTM/PCP)는 CPU가 개입하지 않고도 데이터를 전송하거나 가져올 수 있어서, CPU의 부하를 줄이고 작업이 끝난 뒤 인터럽트를 통해 Co-Processor들이 일을 분담할 수 있다.

OCDS (On-Chip Debug)

Tricore는 JTAG 인터페이스 외에도 DAP 인터페이스를 통해 고속 Debug가 가능한 프로토콜을 제공한다.

3. Tricore Programming Model

Architectural Registers

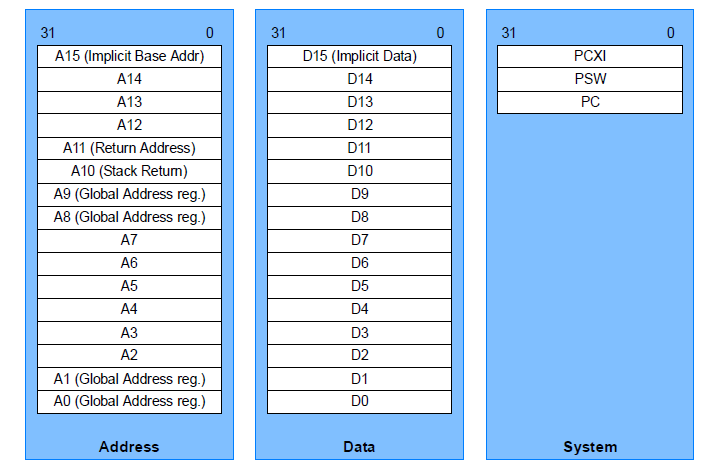

Tricore 아키텍처에는 세 가지 종류의 레지스터가 있다. 이 레지스터들은 프로그램을 실행하면서 데이터를 저장하고 관리하는데 사용된다.

-

GPRs (General Purpose Registers)

- 32개의 GPR이 있다. GPR은 데이터를 저장하고 계산하는 데 사용된다. 변수나 중간 계산 결과를 저장한다.

- GPR 중에는 특별한 기능을 수행하는 네 가지 레지스터가 있다.

- D15: 데이터 레지스터로 사용된다.

- A10: 스택 포인터 (SP)로 사용된다.

- A11: 리턴 주소 레지스터로, 함수가 끝났을 때 돌아갈 위치를 저장한다.

- A15: 기본 주소 레지스터로, 메모리에서 데이터를 읽거나 쓸 때 기본 주소를 가리킨다.

-

Special Registers

- PCXI (Program Counter Extension Index): 현재 실행 중인 명령어의 위치를 추적한다.

- PSW (Program Status Word): 프로그램의 상태를 나타내는 정보가 있다.

- PC (Program Counter): 다음 실행할 명령어의 주소를 가리킨다.

Memory Model

-

Memory

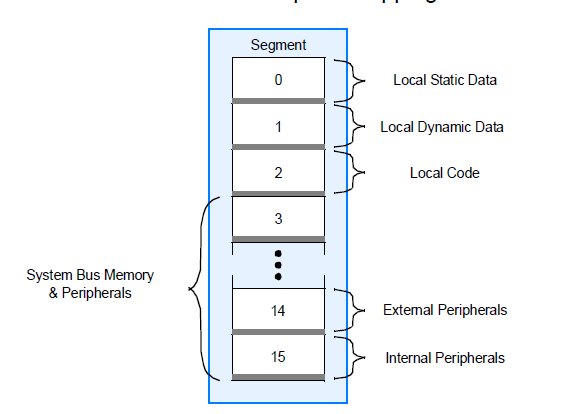

- Tricore는 32비트 프로세서로 최대 4GB 메모리(2^32)에 접근할 수 있다.

-

주소공간

- 4GB 메모리를 256MB씩 16개의 세그먼트로 분리하고, 주소의 상위 4비트(2^4)는 세그먼트를 결정한다.

- 4GB 메모리를 256MB씩 16개의 세그먼트로 분리하고, 주소의 상위 4비트(2^4)는 세그먼트를 결정한다.

-

주소 접근 방법

- 각 세그먼트의 처음 16KB는 두 가지 방식으로 접근 가능하다.

- 절대 주소 (Absolute Addressing): 특정 메모리 주소를 지정해 직접 접근한다.

- 절대 비트 주소 지정 (Absolute Bit Addressing): 비트를 설정하거나 지우는 명령어로 접근한다.

- 각 세그먼트의 처음 16KB는 두 가지 방식으로 접근 가능하다.

4. Tricore Task and Contexts

Task란?

-

Task: 독립적으로 실행되는 작업의 단위로, 두 가지 유형이 있다.

- Software Managed Tasks (SMTs): 실시간 운영체제(RTOS)나 커널의 도움으로 생성되며, 스케줄링 소프트웨어에 의해 관리된다.

- Interrupt Service Routines (ISRs): 특정 이벤트가 발생하면 자동으로 실행된다.

-

Task의 권한

- 각 작업은 그 기능에 따라 권한 수준(Permission Level)이 다르다. Permission Level은 PSW의 비트를 통해 활성화/비활성화된다.

Task의 Context

Context는 해당 Task의 상태를 정의하고, 실행할 수 있도록 하는 모든 정보를 포함한다.

- CPU General Register

- Program Counter (PC)

- 프로그램 상태 정보 (PCXI, PSW)

Context 저장 및 복원

Tricore는 CSA라는 공간을 사용해 Context를 저장한다. 각 CSA는 16개 Word로 구성된다.

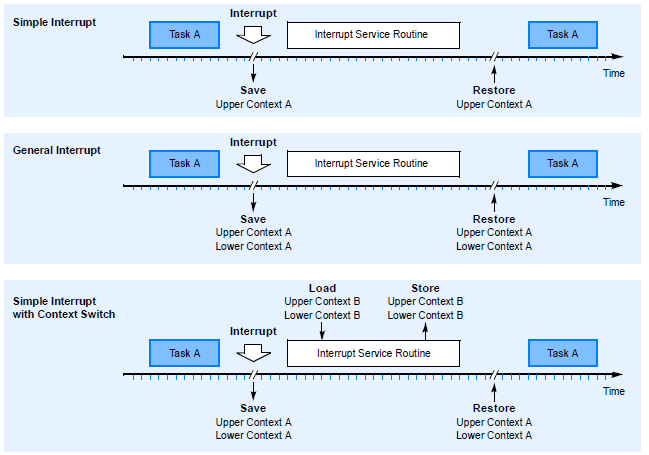

Context Switching

프로그램이 중단되고 새로운 작업을 처리해야 할 때 컨텍스트 스위칭이 일어난다.

5. Tricore Interrupt System

Interrupt 기본 개념

Tricore 아키텍처의 중요한 특징 중 하나는 프로그래머블한 SRN(Service Request Node)을 지원한다.

Service Request Handling

Tricore는 서비스 요청이 발생하면 코드 메모리의 벡터로 점프하여 더 빠르게 실행된다.

인터럽트 우선순위

ISR은 우선순위를 갖고 있으며, 중첩된 인터럽트가 발생하면 우선순위가 낮은 인터럽트가 중단된다.

컨텍스트 관리

- 간단한 인터럽트: ISR에 들어갈 때 상위 Context가 자동으로 저장되고, ISR 종료 시 Upper Context가 자동으로 복원된다.

- 일반 인터럽트: 상위 Context는 자동으로 저장되고, 하위 Context는 명시적으로 저장한다. ISR 종료 후 하위와 상위 Context를 모두 복원한다.

6. Trap System

Trap이란?

Trap은 Non-Maskable Interrupt, 명령어 오류, 잘못된 메모리 접근 등으로 발생하는 이벤트다.

Tricore Trap의 종류

Tricore에서는 다음 8가지 트랩을 분류한다. 각 트랩은 원인에 따라 분류되며, Trap Identifier Number로 구분된다.

- Reset

- Internal Protection

- Instruction Error

- Context Management

- Assertion

- System Bus / Peripheral Error

- System Call

- Non-Maskable Interrupt

7. 마치며

Tricore 아키텍처에 대해 간단히 알아봤다. 다음 글에서는 Tricore 개발환경 설정과 CPU Startup 과정을 살펴볼 예정이다.