개요

FPGA에서 구현한 Single Cycle Processor를 검증한다.

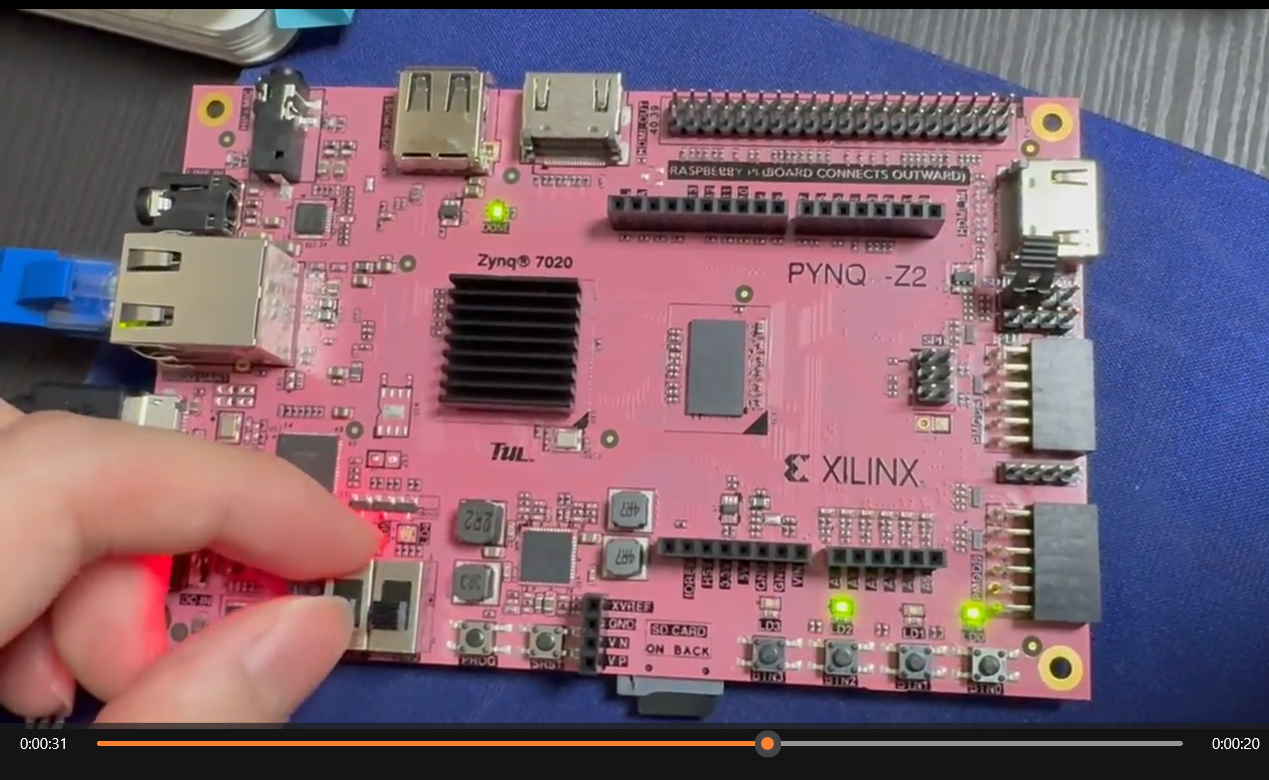

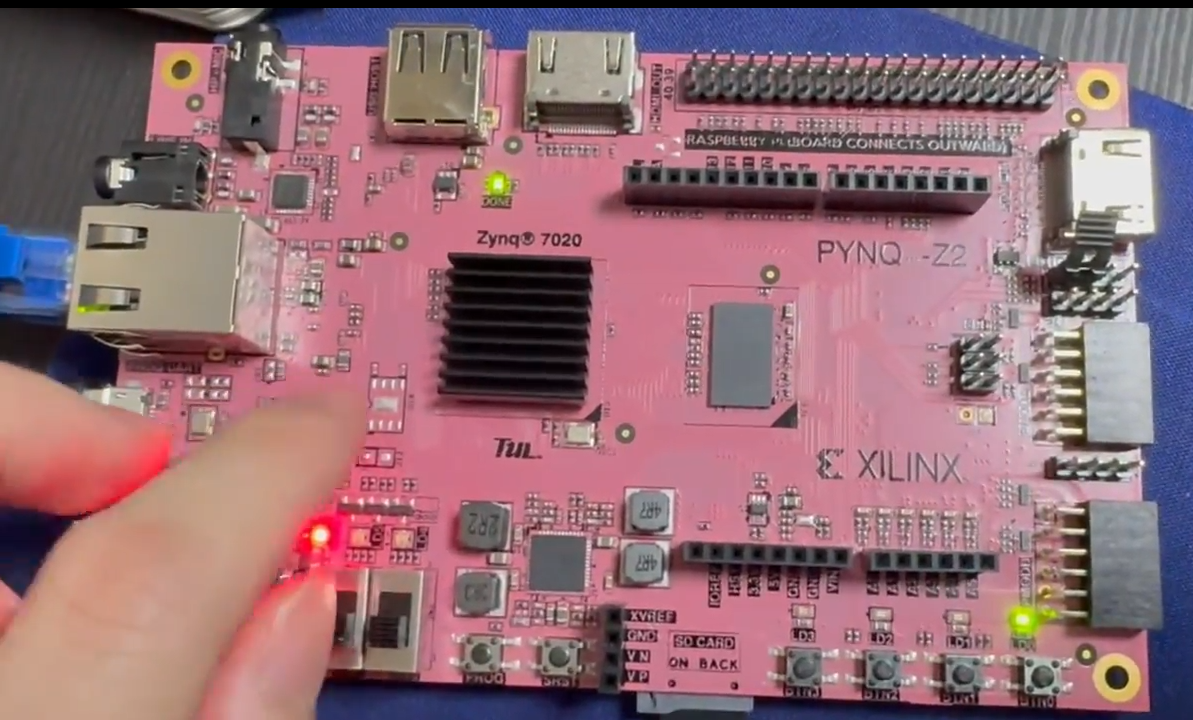

사용한 FPGA : PYNQ-Z2

방법

과정

1. Vivado에 프로젝트를 만들어, 만든 src code를 전부 올린다.

2. xdc 파일을 만들어 FPGA 포트와 내가 보고싶은 signal을 연결한다.

(https://github.com/Xilinx/PYNQ/blob/master/boards/Pynq-Z2/base/vivado/constraints/base.xdc)

3. Bitstream 만들어 FPGA에 올린다.뭐를 확인할거냐?

간단하게 RegWrite, MemWrite, MemtoReg 신호가 각 pc마다 잘 작동하는지 확인한다.

이유 : FPGA의 LED가 4개뿐이여서 확인할 수 있는 값이 별로 없음...

이후 공부를 더해 주피터 노트북으로 일반화된 검증을 시도해보겠다.

step wire를 추가해 switch로 작동시킨다. step은 pc를 하나 증가시키는 역할을 한다.

reset을 button에 연결해 cpu 초기화 담당한다.

Issuees

Step wire 추가 이유

CLK를 switch로 조작해 pc 값에따른 signal을 확인하려 했다. 그러나 다음과 같은 문제가 발생한다

-> 스위치 작동 원리 때문에 그렇다.

스위치는 on, off일 경우 voltage가 바로 0에서 threshold로 가 고정되는 것이 아니다.

주식시장 그래프처럼 threshold 근처를 엄청 왔다갔다 한다. 즉 posedge clk이 여러번 발생할 수 있음 !!!

Metastability

한편 step wire로 pc를 증가시킬때 다음과 같은 문제점이 발생했다.

메타스테빌리티

클럭 엣지 근처에 step이 바뀌면, FF 입력이 setup/hold를 위반해서 FF 출력이:

1. 0도 1도 아닌 애매한 전압 상태로 잠깐 머무름

2. 늦게 결정됨

3. 드물게는 다음 로직에 글리치를 만든다.

그래서 신호를 안정화 시키기 위해 2FF를 추가했다. 즉 신호를 받아드릴 여유 시간을 넣은 것이다.

이 step wire은 스위치에 연결되어 pc 값을 하나씩 증가 시키는 역할을 한다.

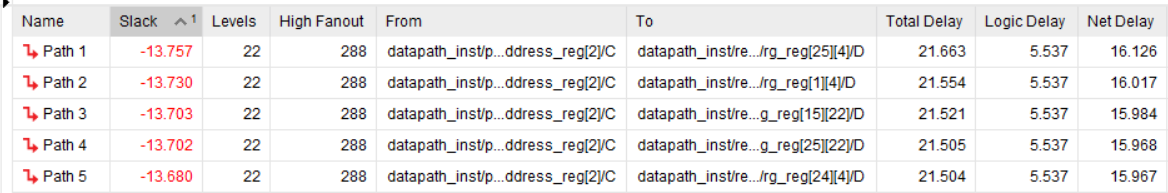

Slack < 0 발생

PYNQ-Z2의 고유 CPU clock은 125MHZ (=8ns/clk) 이다.

그런데 내 single cycle은 모든 step을 하나의 clk에 끝내다보니 slack이 음수로 발생했다.

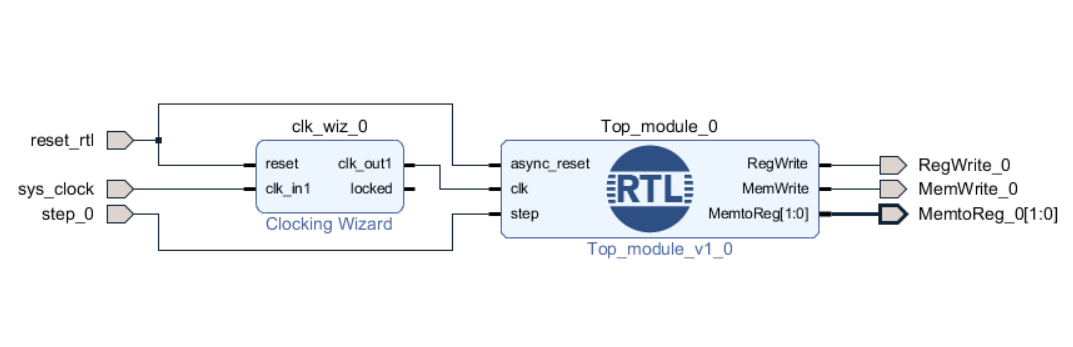

따라서 Clock Wizard를 사용해 Total delay time을 커버할 수 있는 25 MHZ (=40 ns/clk)로 바꾸어 주었다.

Block Design

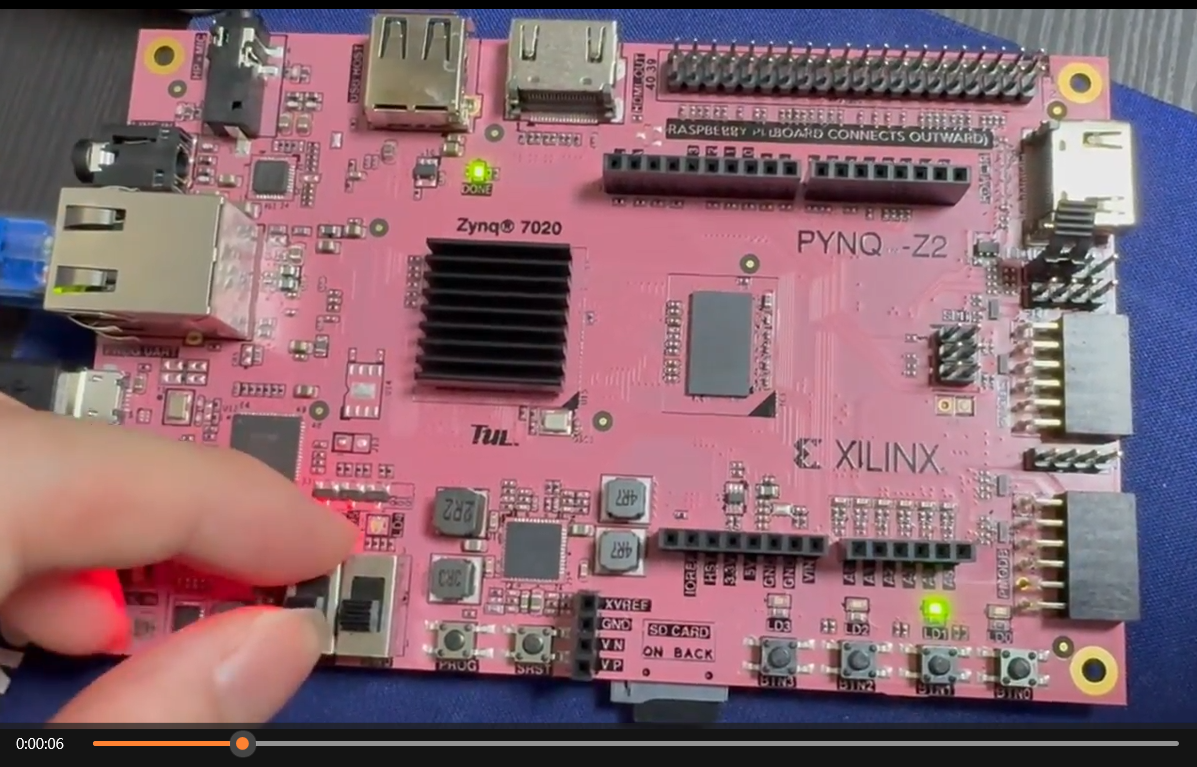

FPGA 검증 사진

다음은 FPGA 구현을 확인하는 사진이다.

영상을 올리려했는데 파일이 커 안올라가 사진을 대신 첨부한다.

Switch를 하나씩 키고 끄며 PC 값을 증가시켰다.

Simulation 결과와 하나씩 비교하며 맞는지 몇개만 check.

| LED3 | LED2 | LED1 | LED0 |

|---|---|---|---|

| memtoreg[1] | memtoreg[0] | memwrite | regwrite |

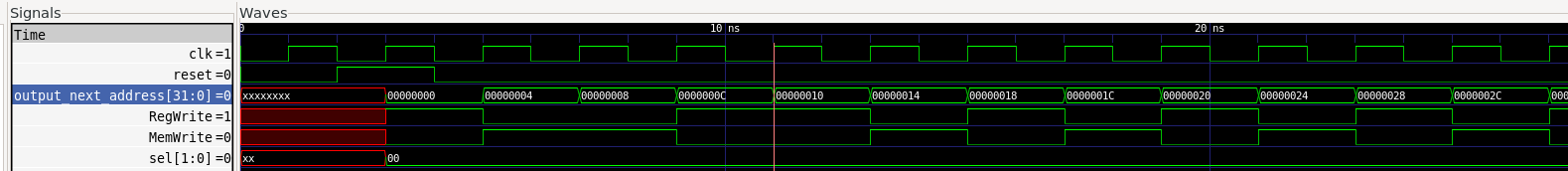

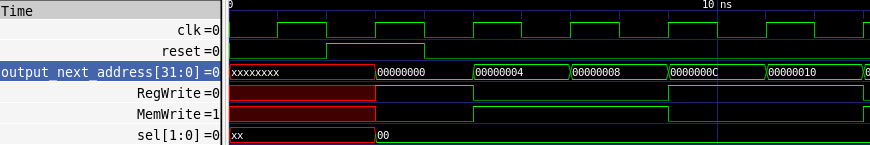

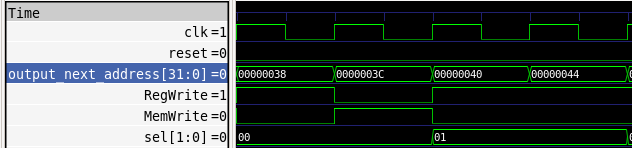

이건 비교할 Simulation 사진

reset일때 사진 regwrite만 켜져있다.

바로 다음 pc 값 사진. simulation 결과처럼 memwrite만 켜진다.

10번째 step, (pc=0x40) memtoreg을 보여줄 simulation 사진