RISC-V (RV32I Single Cycle Processor)

1.RISC-V Single cycle processor 구현 프로젝트

single-cycle CPU를 목표로 구현 RISC-V 중 RV32i을 구현.

2.Vs code에서 Verilog 개발 환경

Vs code에서 빠르고 쉽게 칩을 설계해보자

3.RV32I-ISA 이론 정리

0. Review ISA Definition > Interface between what the software commands and the what the hardware carries out. ISA specifies The memory orgniazio

4.RV32I - 비교기

Input : rs1, rs2 (32비트)output : branch_flag (1비트)논리식 : rs1==rs2구현 과정result=rs1-rs2 계산result의 포함된 비트를 서로 모두 OR 연산한다.만약 result=0 이면 모든 비트를 or했을때 0이 도출될

5.RV32I Architecture - Block Diagram Design

개요 이 글은 RV32I single-cycle processor의 기본 모듈과 Block Diagram 설계 과정을 다룬다. 먼저 single-cycle 구조에서 필요한 최소한 state 요소를 정리하고, 이후 설계철학을 바탕으로 각 Instruction type의

6.RV32I - Verilog code

https://github.com/liquetxnx/RV32I_single_cycle_processor

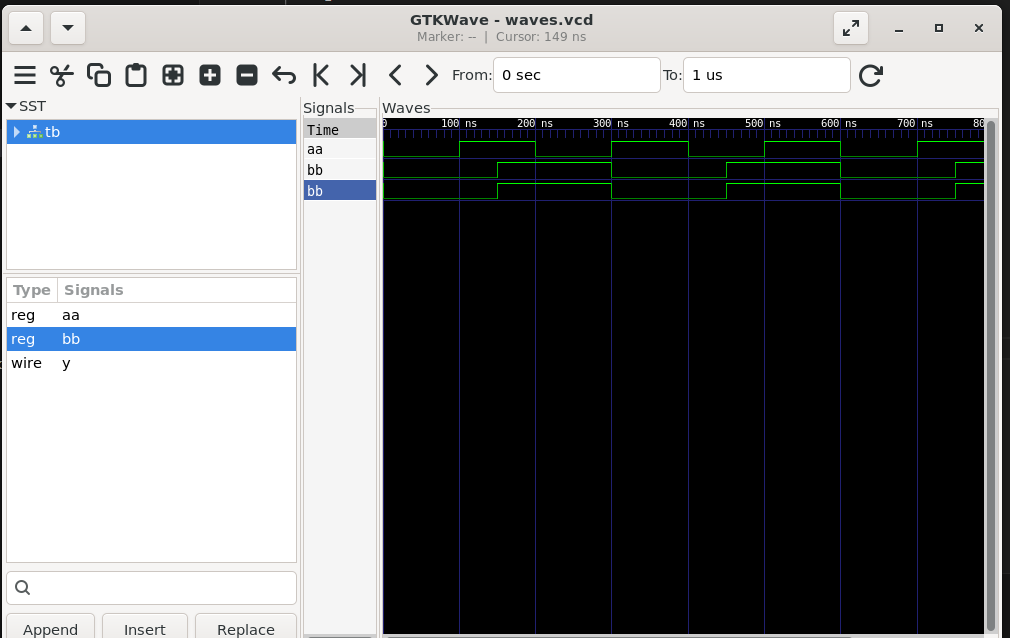

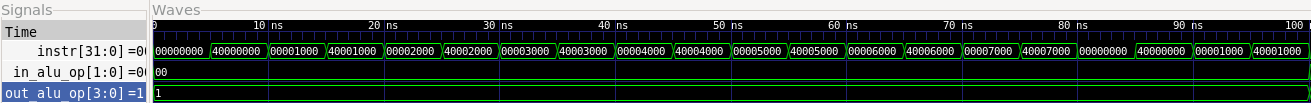

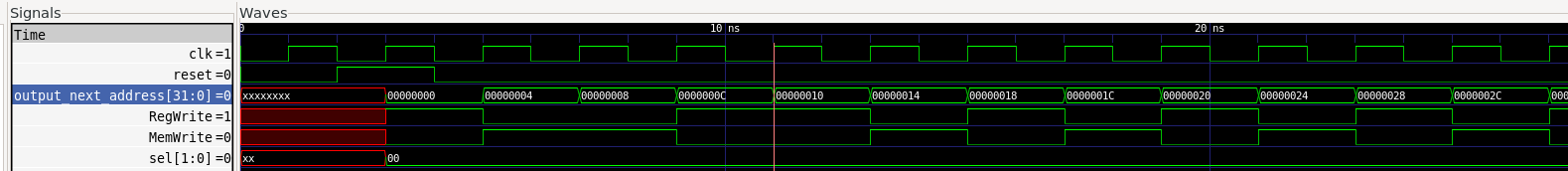

7.RV32I - Testbench 확인

0. Instroduction 구현한 RV32I verilog module들을 waveform으로 잘 작동하는 지 확인한다. Module ImmGen ALU 사용 Testbench skeleton 1. ImmGen 확인 1) ImmGen.v source cod

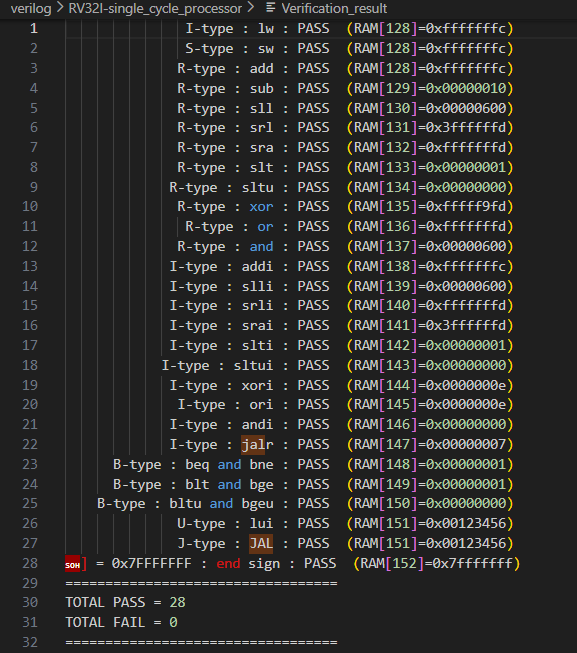

8.RV32I - Verification

Verification 방법을 설명한다.구현한 모든 명령어 타입을 검증한다. 코드 링크https://github.com/liquetxnx/RV32I_single_cycle_processorGoal : RV32I single-cycle CPU의 기능을 C 테스트

9.(Final) Explanation : RISC-V RV32I single cycle processr

지금까지 시간이 없어 포스팅은 제대로 하지 못했지만, 어느 정도 마음에 들게 구현했다. 구현 결과는 다음 링크에 있다. https://github.com/liquetxnx/RV32Isinglecycle_processor RV32I-singlecycleprocesso

10.FPGA (PYNQ-Z2) 사용법

https://blog.umer-farooq.com/a-pynq-z2-guide-for-absolute-dummies-part-i-fun-with-leds-and-switches-47dd76abf9a9

11.RV32I - FPGA 확인

개요 FPGA에서 구현한 Single Cycle Processor를 검증한다. 사용한 FPGA : PYNQ-Z2 방법 과정 Vivado에 프로젝트를 만들어, 만든 src code를 전부 올린다. xdc 파일을 만들어 FPGA 포트와 내가 보고싶은 sig