명령어

💡 연산코드(op-code) | 오퍼랜드(operand)컴퓨터에게 어떤 특별한 동작을 수행할 것을 알리는 비트들의 집합

연산코드(op-code)

- CPU가 수행할 연산을 지정

- n bit ⇒ 2^n개의 연산 실행 가능

- 제어장치 : 연산코드 해석(해독) 후 제어함수 발생(실행)

오퍼랜드(operand)

- 데이터가 저장된 주소 or 연산에 사용될 데이터

- k bit ⇒ 2^k개의 지정할 수 있는 기억장소

단어(word)

각 기억장소에 저장되는 데이터 단위

CPU에 의해 한 번에 처리될 수 있는 비트들의 그룹 : 2^n워드

주소지정방식

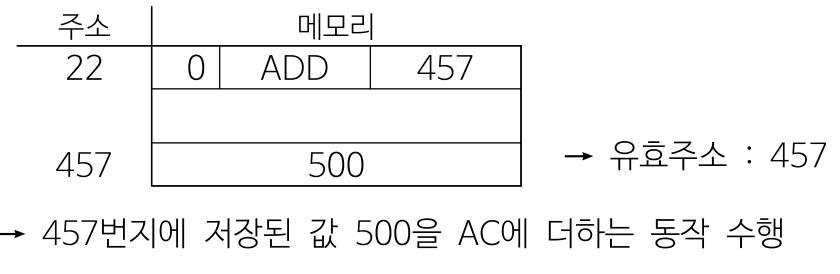

직접주소(direct address)

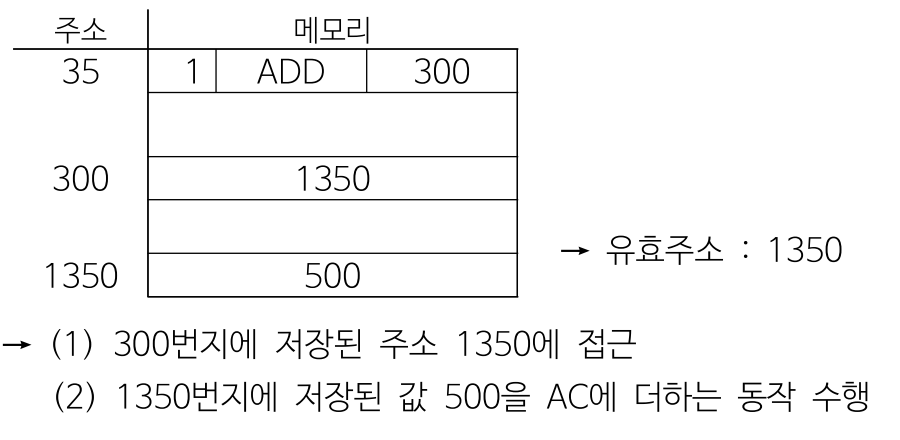

간접주소(indirect address)

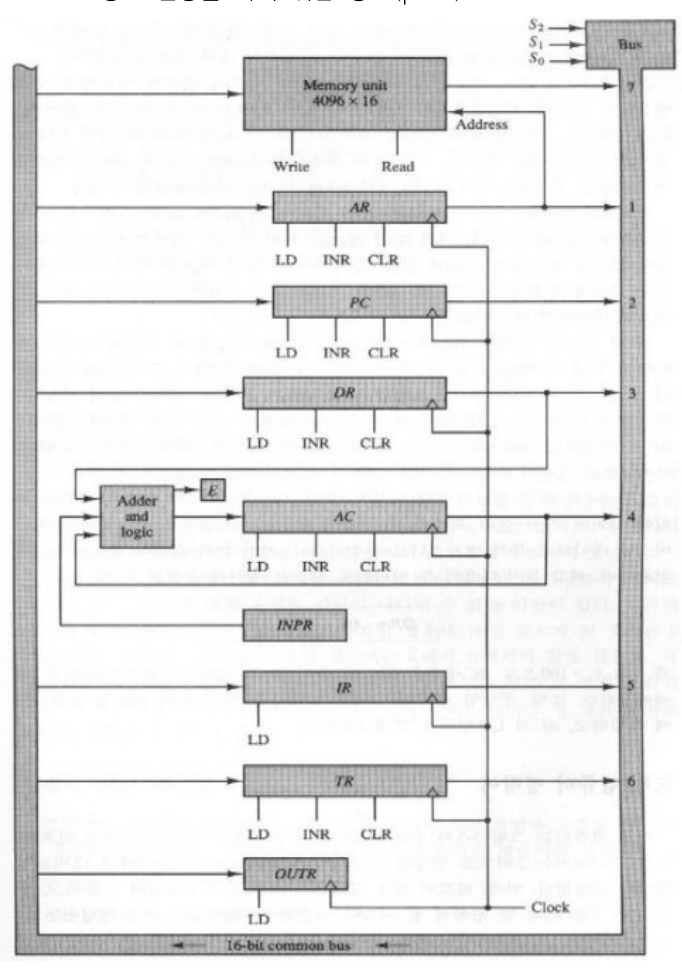

컴퓨터 레지스터

- PC(명령어 계수기)

- 다음에 인출할 명령어의 주소를 가지는 레지스터

- 명령어 인출 후 자동으로 명령어 길이만큼 증가

- AC(누산기)

- 데이터를 일시적으로 저장

- IR(명령어 레지스터)

- 가장 최근에 인출된 명령어가 저장

- MAR(메모리 주소 레지스터, 기억 레지스터)

- 메모리 주소가 버스에 출력되기 전 일시적으로 저장

- MBR(= DR)(메모리 버퍼 레지스터, 데이터 레지스터)

- 기억장치에 쓰거나 읽혀진 데이터 일시 저장

- TR(임시 레지스터)

- 임시저장

- INPR(입력 레지스터)

- 문자입력

- OUTR(출력 레지스터)

- 문자출력

공통버스 시스템

버스 : 레지스터 - 레지스터 or 레지스터 - 메모리 간의 정보 전송을 위한 경로

- 레지스터와 메모리 출력이 공통버스에 연결됨

- 선택입력 S2, S1, S0 을 통해 버스 위에 놓이게 될 출력이 선택됨 (2^3 = 8 = 버스에 연결된 레지스터 개수+메모리)

- INPR : 입력장치로부터 한 문자를 읽어와 AC로 전송

- OUTR : AC로부터 한 문자를 읽어와 출력장치로 전송

- 메모리 - MAR이 연결됨 : 별도 버스 필요없음

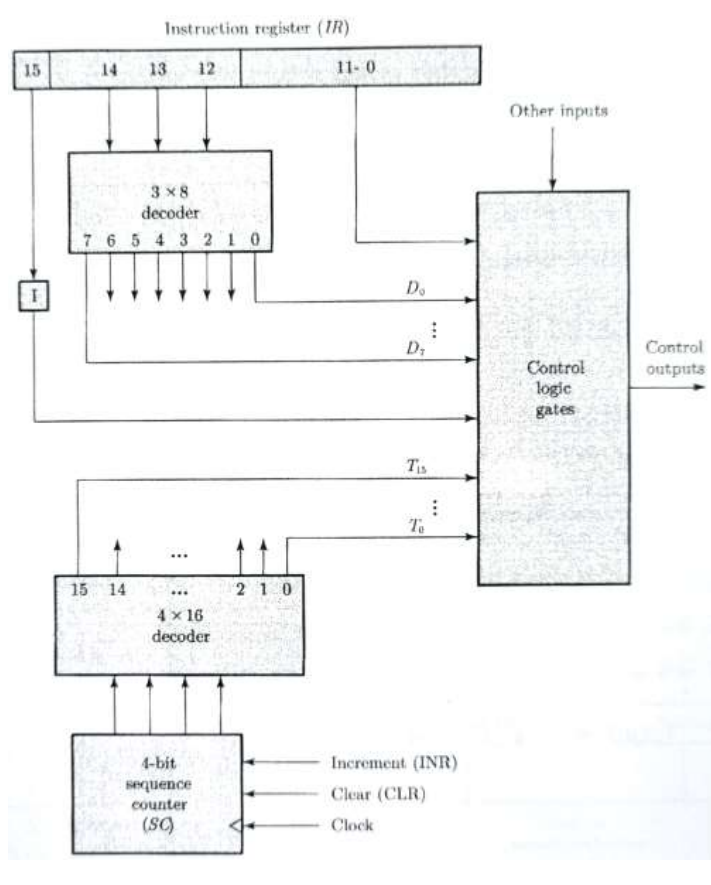

기본 컴퓨터의 제어장치

- 디코더 : n개 입력 ⇒ 개 출력

- 메모리 참조 명령

- 레지스터 참조 명령

- 입출력 명령

명령어 사이클

CPU가 한 개의 명령어를 실행하는데 필요한 전체 처리과정

- 인출(fetch) : 명령어를 메모리에서 가져온다

- 해독(decoding) : 명령어를 해독한다. 간접주소 방식일 경우 유효주소를 읽어온다.

- 실행 : 명령어를 실행한다

인터럽트 사이클

외부장치가 전송 준비가 되었을 때 컴퓨터(CPU)에게 이를 알리는 방법

인터럽트 실행 과정

- CPU는 프로그램 실행 중에 플래그를 체크X

- 플래그가 세트(=1)되면 컴퓨터는 샐행 중인 프로그램을 즉각 중지하고 입출력 실헹

- 일출력 실행이 끝나면 터럽트 전 실행하던 프로그램 실행

인터럽트 인에이블 플립플롭(IEN)

IEN이 세트(=1)될 때만 인터럽트 걸 수 있음

인터럽트 플립플롭(R)

인터럽트 유무 저장

메모리 참조 명령어

- AND

- AC와 메모리워드를 AND논리연산

- ADD

- AC + 메모리워드 → AC, 캐리값은 E플립플롭

- LDA

- 메모리 워드 → AC

- STA

- AC → 메모리 워드

- BUN

- 유효주소를 변경(분기 OR JUMP)