Logic Design의 Procedure

-

먼저 사람의언어로 표현된 specification을 state table 혹은 state diagram으로 작성

-

state를 최소화 한다.

-

state에 Binary state를 할당한다.(00, 01, 11, 10과 같이)

-

flip - flop을 몇 개 사용할지를 선택한다.

-

state equations와 output equations을 도출한다.

-

전체 logic diagram(회로도)를 작성한다.

Sequence Detector

- Sequence Detector은 1비트 input을 받아 1비트 output을 만들어 낸다.

- Sequence Detector은 bit string의 인풋패턴을 읽어서 아웃풋을 만들어낸다.

Specification

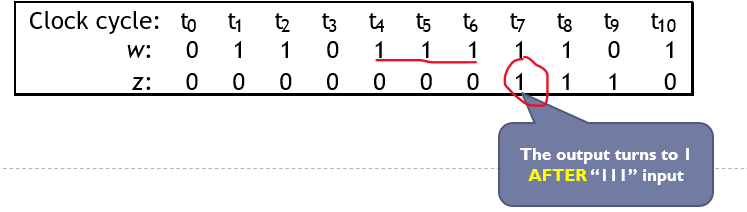

input 패턴이 '111'일 때 output이 1을 도출하는 Sequence Dectector을 Design해보자 (이때 output은 한 clock 뒤로 밀려서 나타나게 한다)

timing sequence

timing sequence는 다음과 같다.

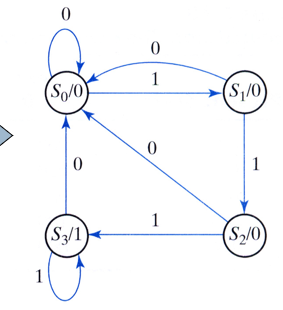

State Diagram

위와 같이 output이 한 clock뒤로 나타나면 moore타입으로 state diagram을 작성할 수 있다.

우선 initial state를 선정한 후 '1'이면 다음 state로 가게하고

'0'이면 initial state로 오게 한다.

state의 개수는 최소가 되도록 한다.

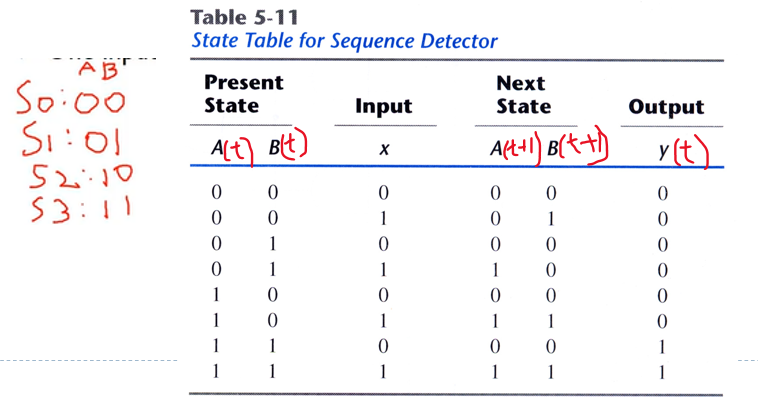

assigned binaty code for each state

-

S0, S1, S2, S3와 같이 표현한 state를 binary code인 0과 1로 assign한다.

-

S0 : 00, S1 : 01, S2 : 10, S3 : 11로 assign

State Table의 모습

output y가 Moore machine이기 때문에 현재의 state에만 depand 하는 것을 알 수 있다.

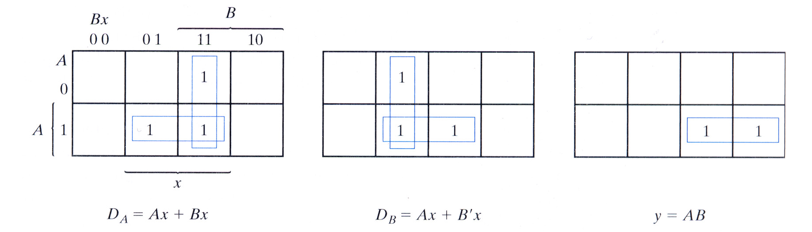

Equation 도출

위의 진리표를 통해 State equation과 output equation을 도출한다.

도출하는방법은 k-map을 활용한다.

Da = A(t+1)

Db = B(t+1)임

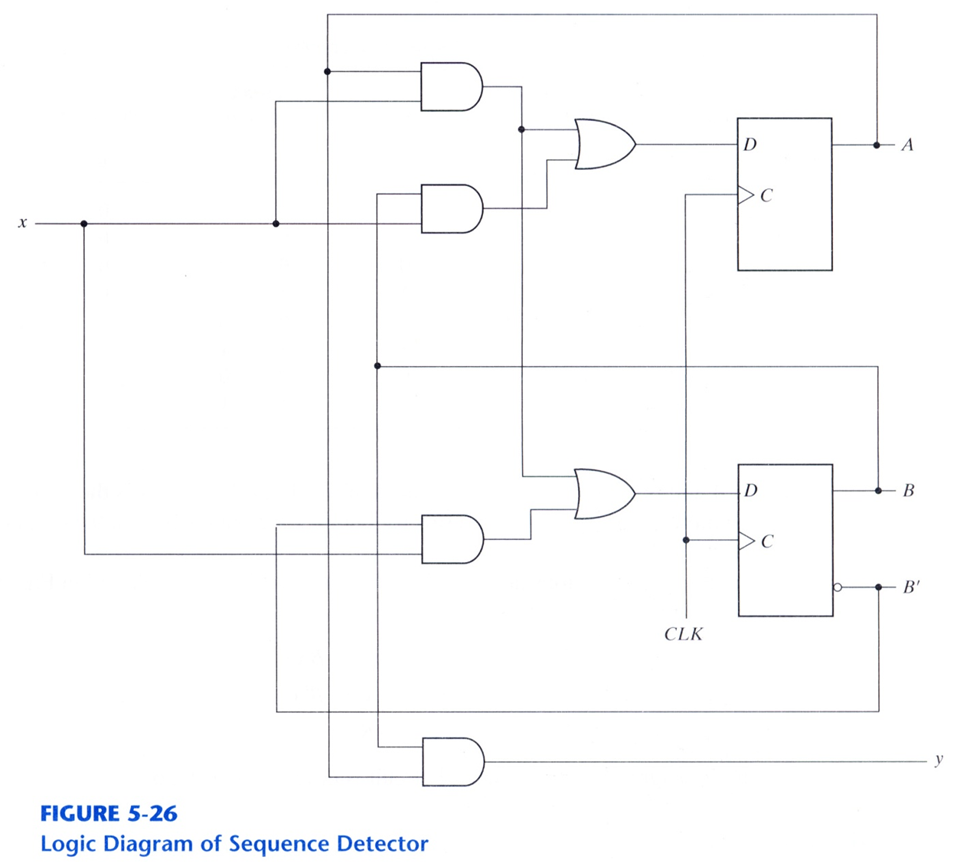

Logic diagram

Equation을 바탕으로 회로도를 작성한다.

위의 회로가 최종적으로 '111'을 detect하는 회로이다.(Moore Machine)

Reference 상명대학교 정진우교수님 강의 자료

.jpg)