1. ARM System

CISC and RISC

- CISC - Complex Instruction Set Architecture (ex.

x86)

n bytesize instruction. => PC +x(variable) - RISC - Ruduced Instruction Set Architecture (ex.

ARM,MIPS,RISC V)

fixed bytesize instruction => PC +N(fixed)

ARM ISA (Instruction Set Architecture)

- thumb-16 -

2 byte - thumb-32 -

4 byte - ARM -

4 byte - Jazzle -

1 byte

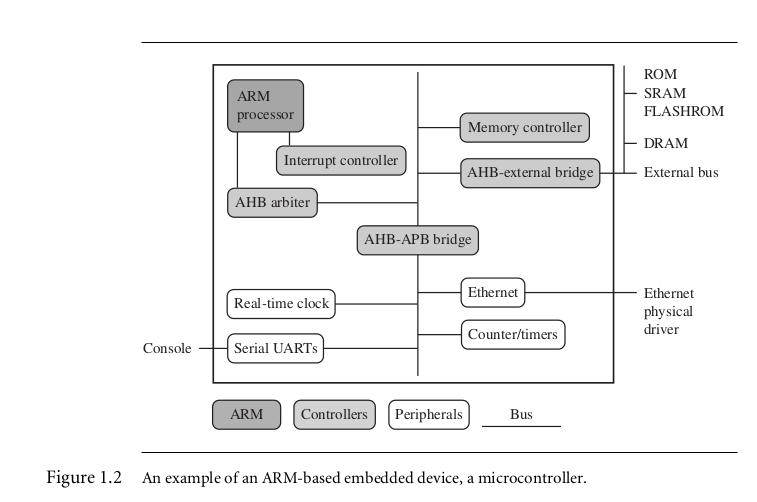

2. ARM Hardware

AMBA (Advanced Microcontroller Bus Architecture)

AHB Bus: Slow Bus

APB Bus: Slow Bus, But faster than AHB Bus

AXI Bus: Fast Bus (Main Bus)

CHI Bus: Coherent Hub Interface (newly added, 2013)

Why Bridge is needed ?

Bus synchronizes faster devices and slow devices.

Fetching Instruction Size

| Instruction size | 8-bit memory | 16-bit memory | 32-bit memory |

|---|---|---|---|

ARM 32-bit | 4 cycles | 2 cycles | 1 cycles |

Thumb 16-bit | 2 cycles | 1 cycles | 1 cycles |

.

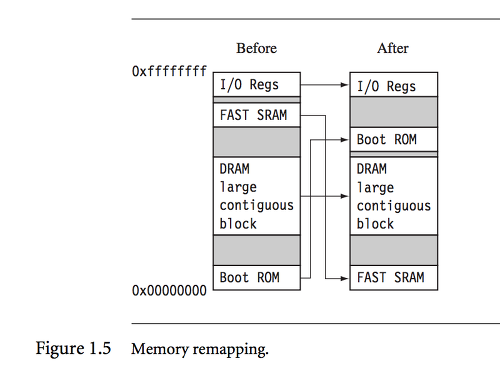

Memory Remapping

.

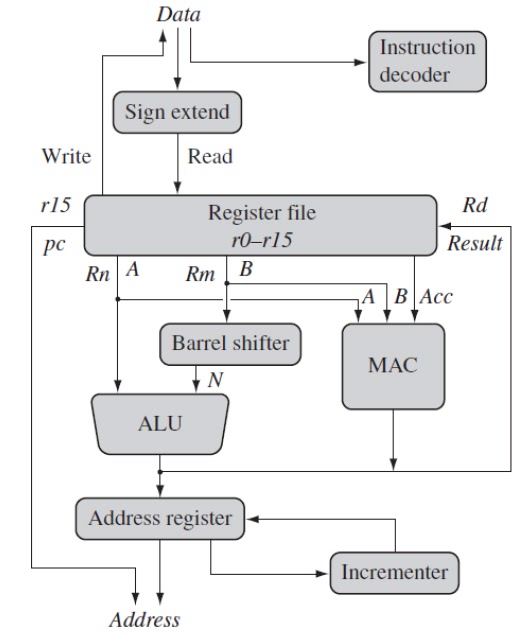

3. ARM Core

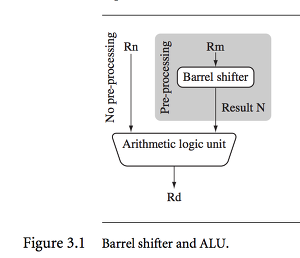

ALU: Arithmetic Logic UnitMAC: Multiply-AccumulateBarrel Shifter: Bit-shift unitAddress Register: Program CounterIncrementer: increase PC value to size of instructionSign extend: convert 8-bit and 16-bit numbers to 32-bit values.

Simple Code

simple C code

x = 10;

y = x;to ARM assembly

mov r0, #10

STR r0, [sp, #8]

LDR r0, [sp, #8]

STR r0, [sp, #12]상수가 크면? 값을 쪼개서 저장!

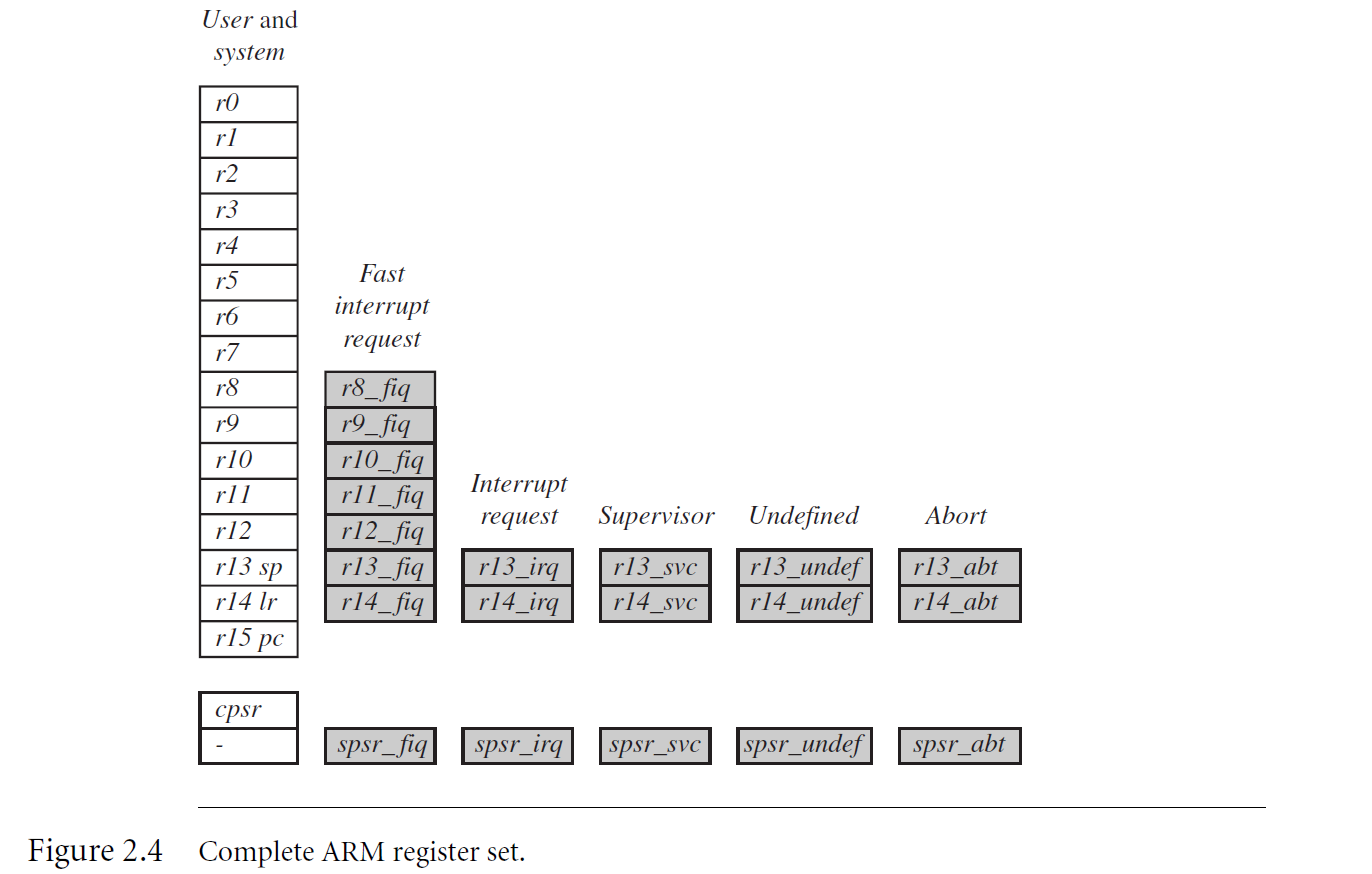

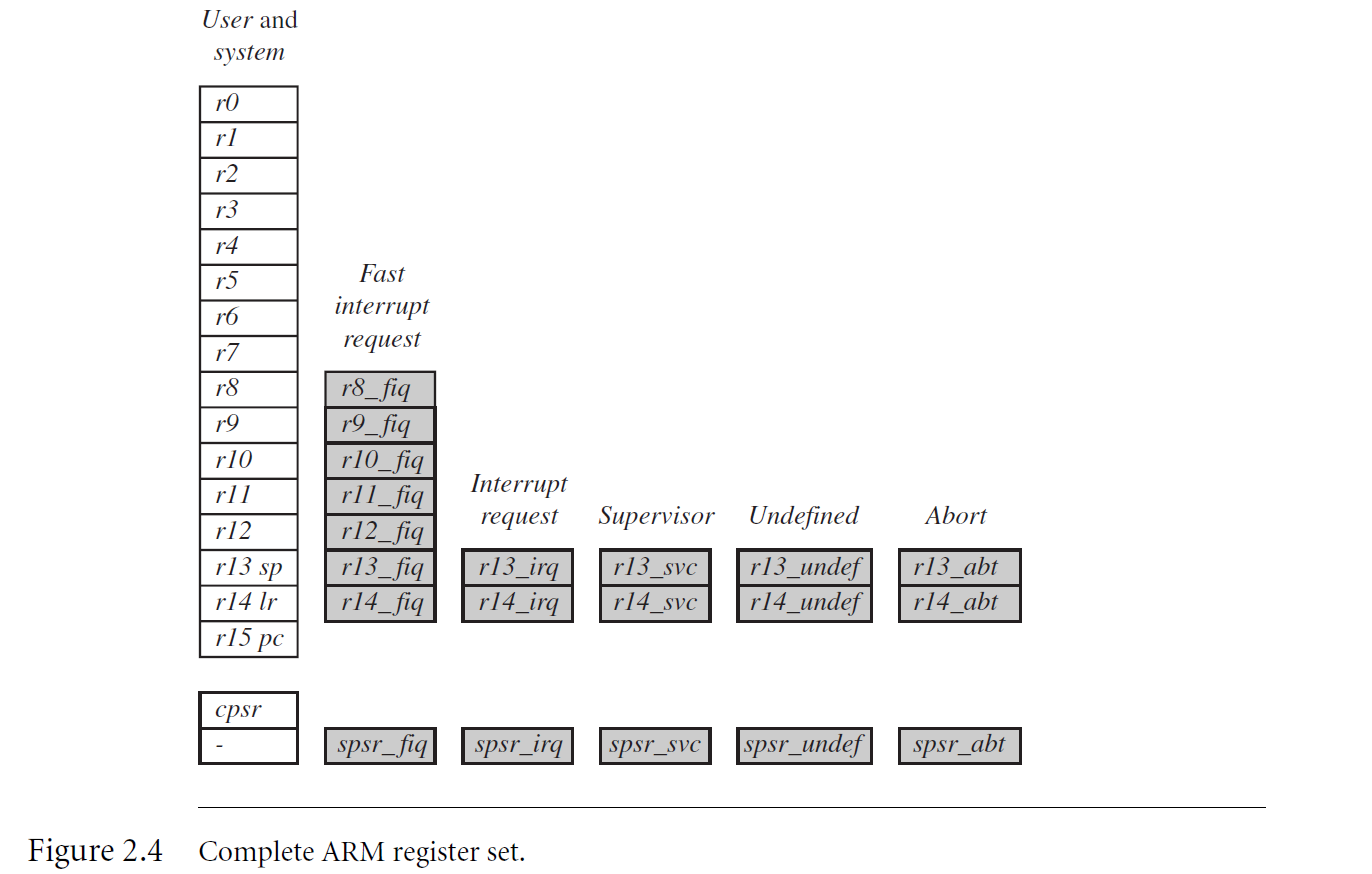

4. Register

General Purpose Register

r0~r12r13(sp) - Stack Pointerr14(lr) - Link Registerr15(pc) - Program Counter

sp, lr 을 사용하는 이유

- 지역 인수 저장

- 인자 전달

- 돌아올 PC 설정

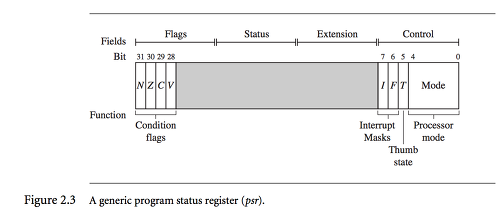

What is CPSR

Current Program Status Register

PSR (Program Status Register)

Condition flags

N: NegativeZ: ZeroC: CarryV: oVerflow

Interrupt Mask

F: FIQ maskI: IRQ mask

Thumb State

Thumb instruction that increases performance and reduces program size.

Mode

to the below

5. Mode

Name | Abbreviation | Privileged | Mode [4:0] |

|---|---|---|---|

| Abort | abt | yes | 10111 |

| Fast Interrup request | fiq | yes | 10001 |

| Interrupt request | irq | yes | 10010 |

| Supervisor | svc | yes | 10011 |

| System | sys | yes | 11111 |

| Undefined | und | yes | 11011 |

| User | usr | yes | 10000 |

.

6. Interrupt

x86

NMI- Non-Maskable Interrupt

**NEVER EVER** MaskableIRQ- Interrupt Request

ARM

FIQ- Fast Interrupt Request

Maskable, but handle faster thanIRQIRQ- Interrupt Request

7. Banked Register

A banked register maps one-to-one onto a user mode register. If you change processor mode, a banked register from the new mode will replace an existing register.

8. Condition mnemonics

| Mnemonic | Name | Condition flags |

|---|---|---|

| EQ | equal | Z |

| NE | not equal | z |

| CS HS | carry set/unsigned higher or same | C |

| CC LO | carry clear/unsigned lower | c |

| MI | minus/negative | N |

| PL | plus/positive or zero | n |

| VS | overflow | V |

| VC | no overflow | v |

| HI | unsigned higher | zC |

| LS | unsigned lower or same | Z or c |

| GE | signed greater than or equal | NV or nv |

| LT | signed less than | Nv nV |

| GT | signed greater than | NzV or nvz |

| LE | signed less than or equal | Z or Nv or nV |

| AL | always (unconditional) | ignored |

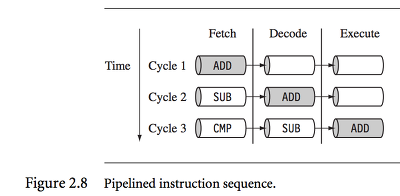

9. Pipeline

1. Fetch

fetch loads an instruction from memory

2. Decode

decode identifies the instruction to be executed

3. Execute

Execute processes the instruction and writes the result back to a register

Using a pipeline speeds up execution by fetching the next instruction while otheer instructions are being decodeded and executed.

10. Executions, Interrupts, Vector Table

| Exection / Interrupt | Shorthand | Address | High address |

|---|---|---|---|

| Reset | RESET | 0x00000000 | 0xFFFF0000 |

| Undefined instruction | UNDEF | 0x00000004 | 0xFFFF0004 |

| Software interrupt | SWI | 0x00000008 | 0xFFFF0008 |

| Prefetch abort | PABT | 0x0000000C | 0xFFFF000C |

| Data abort | DABT | 0x00000010 | 0xFFFF0010 |

| Reserved | - | 0x00000014 | 0xFFFF0014 |

| Interrupt request | IRQ | 0x00000018 | 0xFFFF0018 |

| Fast Interrupt request | FIQ | 0x0000001C | 0xFFFFFF1C |

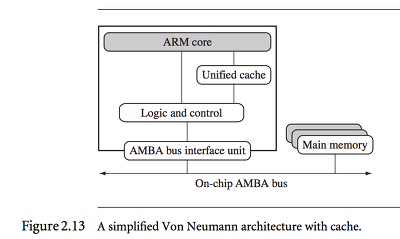

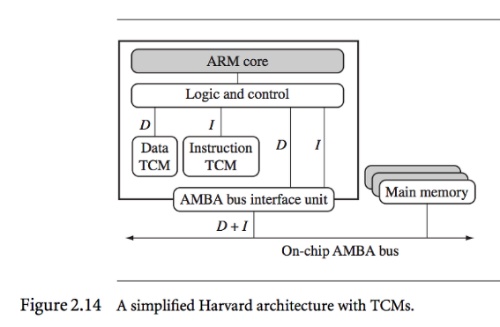

11. Cache

ARM has two forms of cache

Von Neumann style

It combines both data and instruction cache

Harvard Style

Harvard style core has separate caches for data and instruction

TCM (Tightly Coupled Memory)

TCM is fast SRAM located close to the core and guarantees the clock cycles required to fetch instructions or data.

12. Architecture Revisions

ARM {X} {Y} {Z} {T} {D} {M} {I} {E} {J} {F} {S}

- X - family

- Y - memory management / protection unit

- Z - cache

- T - Thumb 16-bit decode

- D - JTAG debug

- M - fast multiplier

- I - embeddedICE macrocell

- E - enhanced instructions (assumes TDMI)

- J - jazzle

- F - vector floating-point unit

- S - synthesizible version

최근에는 이러한 방식으로 네이밍 하진 않음.

13. ARM ISA

대표적으로 자주 사용되는 명령어

ADD- Add two valueAND- Logical bitwise AND two valueB- Branch relative +/- 32 MiBBL- Relative branch with linkCMP- Compare two valuesLDR- Load a single values from a virtual address in memoryMOV- move a value into a registerMRC/MCR- move coprocessor from an ARM register from a status register / converselyMRS/MSR- move to ARM register from a status register (CPSR or SPSR) / converselyMUL- multiply two valueORR- logical bitwise OR of two valueSUB- subtract two valuesSTR- store register to a virtual address in memorySWI- Software interruptTEQ- Test for equality of two valuesTST- Test for bits in a values

Barrel Shifter

MOV r7, r5, LSL #2 ; r7 = r5 << 2 = r5 * 4출처

[책] ARM System Developer's Guide (Andrew N. SLOSS, Dominic SYMES, Chris WRIGHT)

[이미지] https://bnmbiw.files.wordpress.com/2013/01/embedded-hardware.png

[이미지] https://theorycircuit.com/arm-processor-introduction/

[이미지] https://jiming.tistory.com/archive/201511?page=3

[사이트] https://en.wikipedia.org/wiki/Advanced_Microcontroller_Bus_Architecture

헐 이런 스터디가 있군요;;