오류 검출이란?

컴퓨터는 정해진 프로그램에 따라 움직이는데 이 과정에서 오류가 생기면 다양한 문제가 나타날 수 있다.

그래서 프로그램을 작성할 때는 반드시 오류 검출 과정을 거치게 된다. 즉, 컴퓨터가 처리한 데이터가 올바른지 검사를 하거나 하드웨어나 소프트웨어 상의 틀린 곳을 검출하는 것이다.

이 과정을 오류 검출이라고 한다. 컴퓨터의 오류는 프로그램을 작성할 때 이외에도 바이러스의 침투나 해킹으로 인한 데이터 변화 등에 의해서도 데이터에 오류가 나타나기도 한다.

오류 검출을 위한 패리티 비트 (Parity Bit)

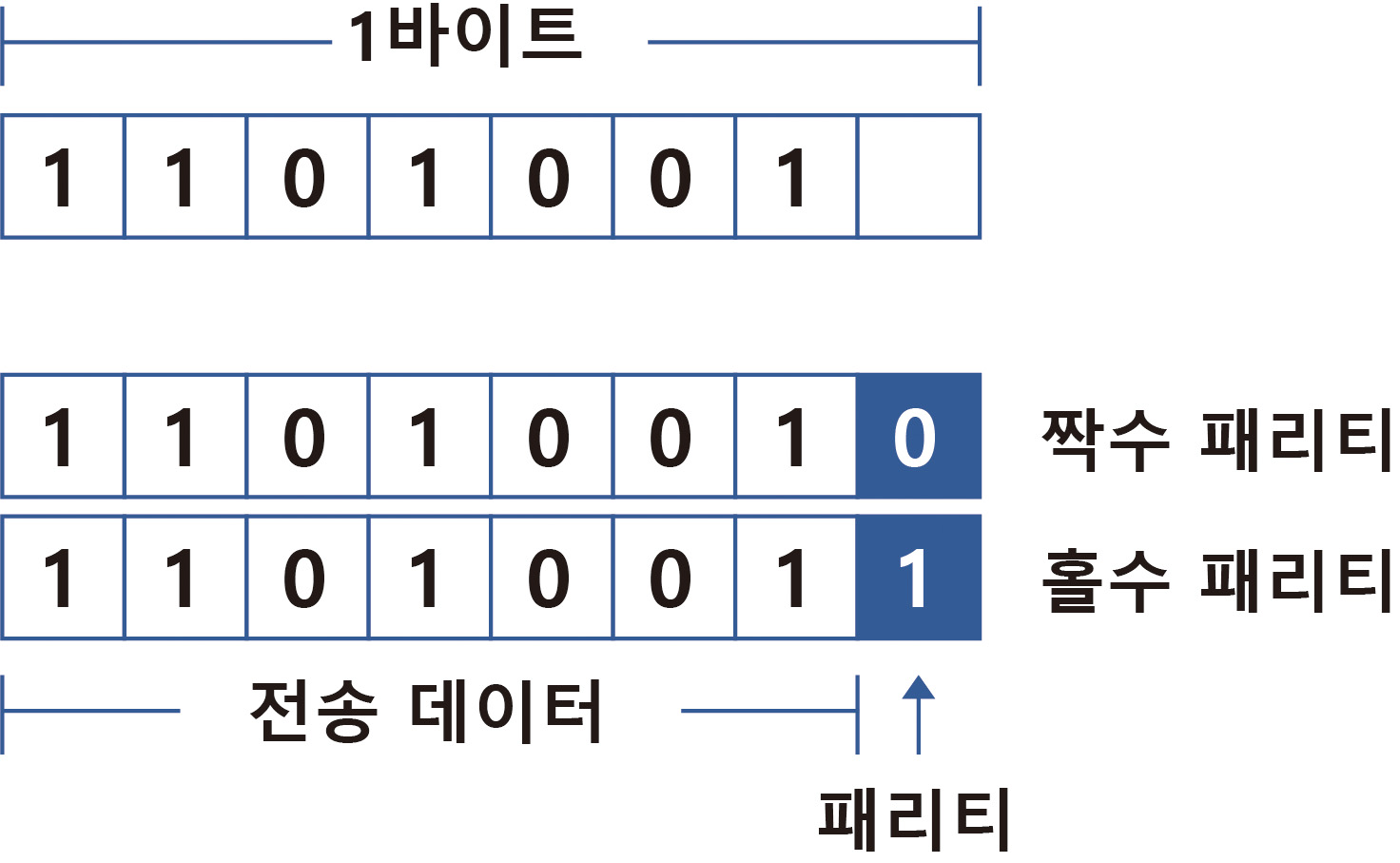

패리티 비트(Parity Bit)는 정보 전달 과정에서 오류가 생겼는 지 검사하기 위해 추가하는 비트를 말한다.

즉, 오류 검출을 위해 전송하고자 하는 데이터의 끝에 1비트를 더하여 전송하는 방법으로 1바이트(8비트) 구조에서 피리티 비트는 7비트 크기의 ASCII 코드를 제외한 나머지 1비트이다.

패리티 비트를 포함해 1의 개수가 짝수(짝수 패리티 비트)나 홀수(홀수 패리티 비트)가 되게하는 2가지 종류의 패리티 비트가 있다.

짝수/홀수 패리티 비트

오류 검출을 위해 추가적으로 붙게 되는 패리티 비트를 짝수 패리티로 설정할 것인지 또는 홀수 패리티로 설정할 것인지에 따라 붙게되는 패리티 비트의 값이 달라진다.

짝수 패리티라고 0으로 값을 고정하거나 홀수 패리티라고 값을 1로 고정하는 것은 아니다.

짝수 패리티(Even Parity)는 실제 전송하고자 하는 데이터의 각 비트의 값 중 1의 개수가 짝수가 되도록 패리티 비트를 정하는 방식이다.

즉, 데이터 비트에서 1의 개수가 홀수이면 패리티 비트를 1로 정하고, 데이터 비트에서 1의 개수가 짝수이면 패리티 비트를 0으로 정하는 것이다.

홀수 패리티(Odd Parity)는 짝수 패리티와 반대로 실제 전송하고자 하는 데이터의 각 비트의 값 중 1의 개수가 홀수가 되도록 패리티 비트를 정하는 방식이다.

위의 설명한 것과 반대로 데이터 비트에서 1의 개수가 홀수이면 패리티 비트를 0으로 정하고, 데이터 비트에서 1의 개수가 짝수이면 패리티 비트를 1로 정하는 것이다.

패리티 비트 작동 방식

컴퓨터의 하드디스크에 데이터는 실질적으로 0과 1 즉, 이진수로 변환되어 저장된다.

데이터는 기억장치에 특정한 크기 단위로 저장되는데 저장 또는 읽을 때는 주소를 통해 접근한다.

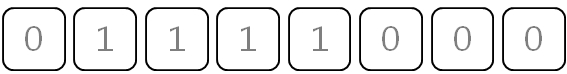

예를 들어 120이라는 값을 8비트 공간에 저장했다고 가정하자.

그럼 이 120이라는 값은 내부적으로 2진수로 바뀌어 특정 주소에 위치하게 된다.

120은 2진수로 1111000이며 데이터를 저장했을 때는 01111000으로 저장된다.

만약 이 상태에서 오류가 발생되어 첫번째 1이 0으로 바뀐다면 00111000이 되어 읽을 때는 56으로 원하지 않는 데이터가 될것이다.

이때 이 데이터에 짝수 패리티비트를 적용해볼 것이다.

이전 같이 120이라는 값을 이진수로 바꾸고 앞에 빈 공간 없이 채워넣은 뒤, 맨 뒤에 마지막 비어있는 비트를 패리티 비트로 사용한다고 하자.

짝수 패리티 비트의 경우 데이터의 합이 짝수가 되게 만들어야 한다.

현재 데이터는 1 + 1 + 1 + 1 + 0 + 0 + 0 으로 짝수이기 때문에 맨 뒤 패리티 비트는 0이 된다.

이 상태에서 첫번째 1이 오류로 소실된다 하더라도 패리티를 포함한 데이터의 합은 짝수이기 때문에 소실된 데이터가 1이라는 것을 예측할 수 있다.

이처럼 패리티 비트를 이용해 오류를 검출할 수 있다.

하지만 패리티 비트는 2개의 비트 오류가 발생할 경우 검출할 수 없다는 한계점도 가지고 있다.

왜 중요할까??

시리얼 통신을 하는데 있어서 패리티 비트를 추가해 데이터를 송수신하는 이유는 바로 데이터를 송수신하는 과정에서 각 비트를 단위시간당 하나씩 보내게 되어있는데, 이때 알 수 없는 요인에 의해서 비트의 값이 틀어져 1이 0으로 바뀌거나 0이 1로 바뀌었을 때 이를 확인할 수 있도록 하기 위해서이다.

즉, 패리티 비트를 정하여 데이터를 보내면 받는 쪽에서는 수신된 데이터의 전체 비트를 계산하여 패리티 비트를 다시 계산함으로써 데이터 오류 발생 여부를 알 수 있다. 그러나 패리티 비트는 오류 발생 여부만 알 수 있지 오류를 수정할 수는 없고 2개 비트 오류가 발생하면 검출할 수 없다는 단점이 있다.

시리얼 통신을 하면서 데이터가 손실되어 패리티에 의한 데이터 손실이 발생한 것을 알았을 때는 수신지에서 다시 데이터를 보내달라는 재송신 요청을 할 수 있도록 하는 좀 더 안정적인 통신을 위한 하나의 보호장치라고 할 수 있다.

패리티 비트의 경우 시리얼 통신의 거리가 상당히 멀 경우에 주로 적용이 되며, 송수신 거리가 짧을 경우 일반적으로 패리티 비트는 사용하지 않고, Checksum 데이터를 추가하는 방법으로 데이터의 오류 검출을 한다.

체크섬(checksum)은 중복 검사의 한 형태로, 오류 정정을 통해 전자 통신이나 기억 장치속에서 송신된 자료의 무결성을 보호하는 단순한 방법

참고 자료

https://www.nise.go.kr/sedu/pt/page1_05.html

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=ansdbtls4067&logNo=220886661657

https://ko.wikipedia.org/wiki/%ED%8C%A8%EB%A6%AC%ED%8B%B0_%EB%B9%84%ED%8A%B8

https://dololak.tistory.com/33

https://github.com/gyoogle/tech-interview-for-developer/blob/master/Computer%20Science/Computer%20Architecture/%ED%8C%A8%EB%A6%AC%ED%8B%B0%20%EB%B9%84%ED%8A%B8%20%26%20%ED%95%B4%EB%B0%8D%20%EC%BD%94%EB%93%9C.md