💡Concepts

-

SoC: Zynq-7000 AP SoC

-

내용 추가

-

Digilent와 AMD에서 제공하는 Reference Manual 기반으로 작성함.

1️⃣Zybo Z7 Reference Manual

2️⃣Zynq 7000 SoC Technical Reference Manual(UG585)

3️⃣Zynq-7000 SoC Embedded DesignTutorial (UG1165)

4️⃣Zybo-Z7-Master.xdc

📖Block Diagram & Term

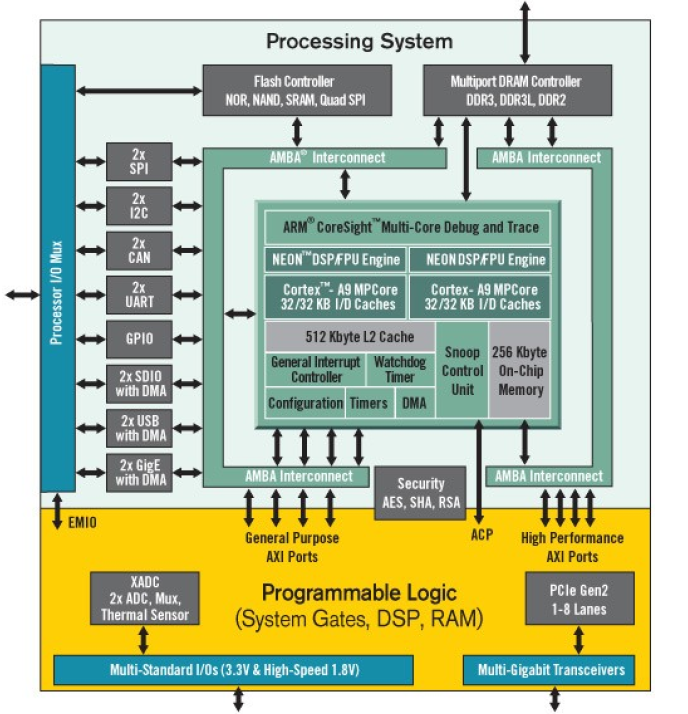

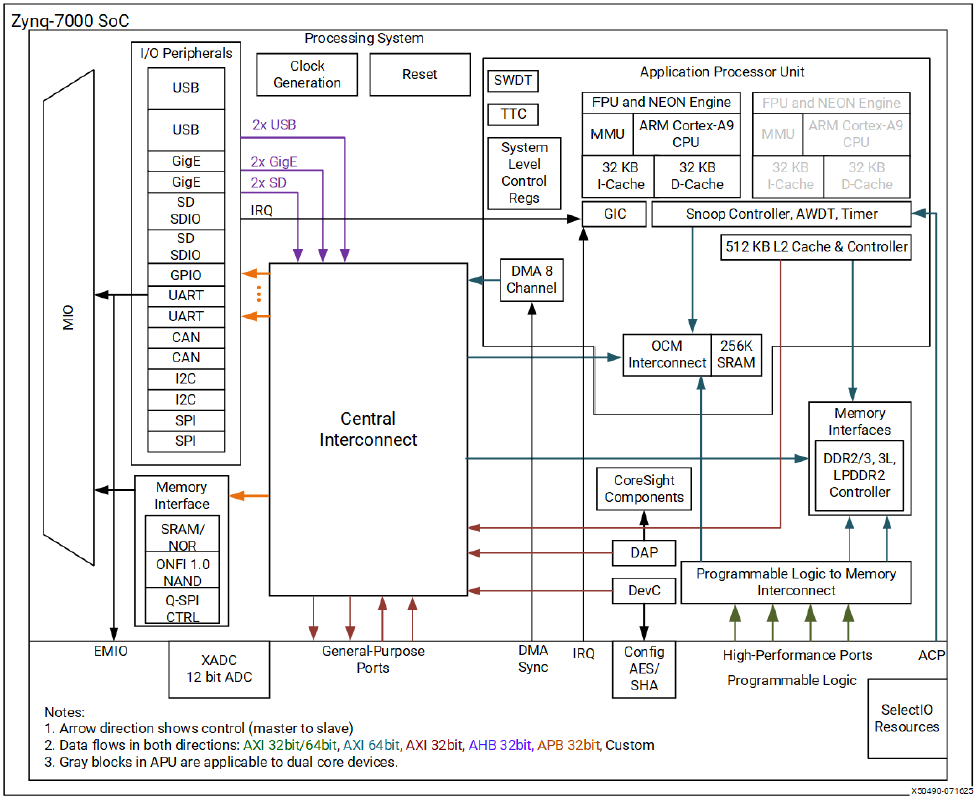

1️⃣Processing System(PS, CPU 영역)

- CPU / 연산 유닛

- ARM Cortex-A9 CPU: 메인 프로세서(듀얼코어)

- FPU (Floating Point Unit): 부동소수점 연산 가속

- NEON Engine: SIMD 벡터 연산(영상, 신호처리)

- SIMD(Single Instruction, Multiple Data): 하나의 명령어로 여러 개의 데이터(벡터)를 병렬 처리

- 메모리 관련

- L1 Cache (32KB I-Cache / 32KB D-Cache): CPU 바로 옆 초고속 캐시

- L2 Cache (512KB)

- OCM (On-chip Mem, 256KB SRAM): 칩 내부 RAM, 초저지연

- DDR Contoller (DDR2/3, LPDDR2): 외부 DRAM 제어

- 메모리 관리 / 시스템

- MMU (Memory Management Unit): 가상 메모리 / 주소 변환

- Snoop Control Unit: CPU 캐시 coherence 유지

- 인터럽트 / 타이머

- GIC (Generic Interrupt Controller): 인터럽트 관리

- Timer: 시간 측정

- Watchdof (AWDT): 시스템 멈춤 감지 후 리셋

- 데이터 이동

- DMA (Direct Memory Access): CPU 개입 없이 메모리 전송

- DMA 8 Channel: 8개 채널 동시 전송 가능

- 디버그 / 추적

- CoreSight Components: ARM 디버깅 시스템

- DAP (Debug Access Port): JTAG 디버깅 인터페이스

- 기타

- System Level Control Registers: 시스템 설정 레지스터

- IRQ: 인터럽트 리퀘스트 신호 라인

2️⃣I/O Peripherals (PS 내부 주변장치)

- 통신

- UART: 시리얼 통신

- SPI: 고속 동기식 통신

- I2C: 저속 디바이스 통신

- CAN: 차량 네트워크

- 네트워크 / 저장

- GigE (Ethernet): 네트워크

- USB: 범용 인터페이스

- SD / SDIO: SD카드 / 확장 인터페이스

- 제어

- GPIO: 일반 입출력

- 메모리 인터페이스

- SRAM / NOR / NAND / QSPI: 외부 Flash / 메모리 연결

3️⃣Central Interconnect (핵심 Bus)

- Central Interconnect

- AXI 기반 내부 데이터 고속도로

- CPU ↔ 메모리 ↔ 주변장치 ↔ FPGA 연결

4️⃣Programmable Logic (PL, FPGA 영역)

- 주요 구성

- Programmable Logic: 사용자 정의 회로 영역, 커스텀

- SelectIO Resources: FPGA I/O 핀 제어

- 연결 블록

- Programmable Logic to Memory Interconnect: PL ↔ DDR 연결 경로

5️⃣PS ↔ PL 인터페이스 (핵심 포트)

- GP (General Purpose Ports)

- 용도: 제어 신호

- 방향: CPU ↔ FPGA

- 특징: 느림, 레지스터 접근

- HP (High Performance Ports)

- 용도: 대용량 데이터 전송

- 방향: FPGA → DDR

- 특징: 고속 AXI

- ACP (Accelerator Coherency Port)

- 용도: CPU cache와 데이터 일관성 유지

- 특징: cache-coherent access

6️⃣외부 연결 핀

- MIO (Multiplexed I/O)

- PS에서 직접 핀으로 연결

- EMIO (Extended MIO)

- PS → FPGA → 핀

- FPGA 통해 확장

7️⃣아날로그

- XADC (12-bit ADC)

- 아날로그 → 디지털 변환

8️⃣보안 / 설정

- DevC (Device Configuration)

- FPGA 설정 (bitstream 로딩)

- Config AES/SHA

- 암호화 / 보안 부팅

9️⃣클럭 / 리셋

- Clock Generation

- 시스템 클럭 생성

- Reset

- 전체 리셋 제어