ASIC

- Application Specific Integrated Circuit

- 특정 app에 특화된 하드웨어

- 전용 하드웨어를 설계하는 경우에는 설계자의 의도에 따라 연산기의 수를 조절할 수 있기 때문에 보통의 경우 전용 하드웨어가 소프트웨어보다 빠름. → 병렬 연산

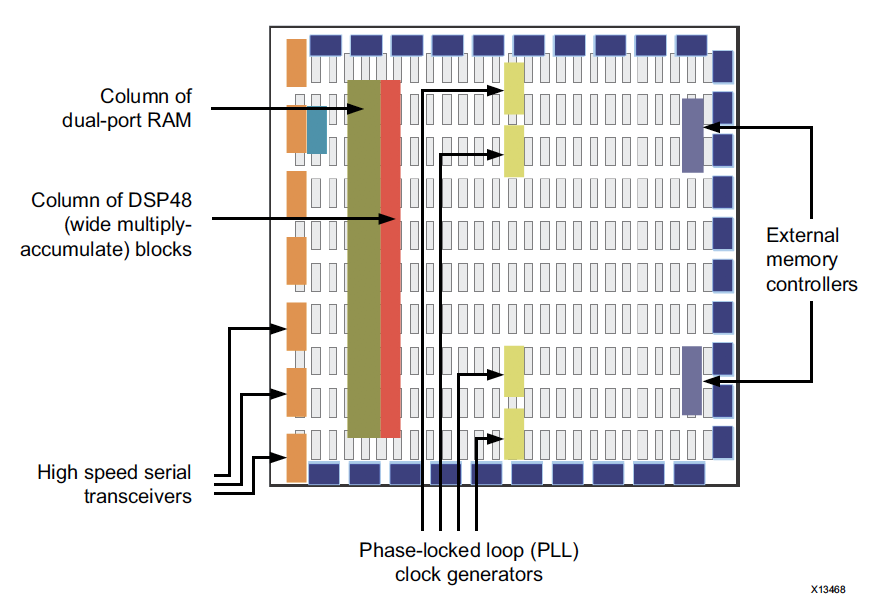

FPGA

- Field Programmable Gate Array

- 프로그래밍이 가능한 회로

- ASIC 과정에서 백엔드(Back-end)라고 불리우는 반도체 생산 공정을 생략

| 항목 | ASIC | FPGA |

|---|

| 개발 인력 | 수 백명 | 수 명 |

| 개발 일정 | 상대적으로 김 | 상대적으로 짧음 |

| 수정 여부 | 수정 불가능 | 수정 가능 |

| 생산 볼륨 | 100만개 이상 | 수 개 |

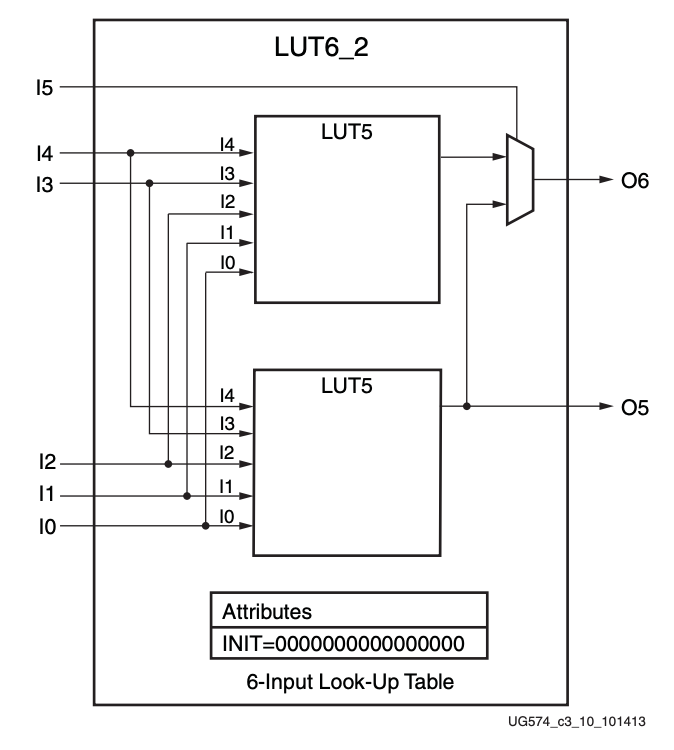

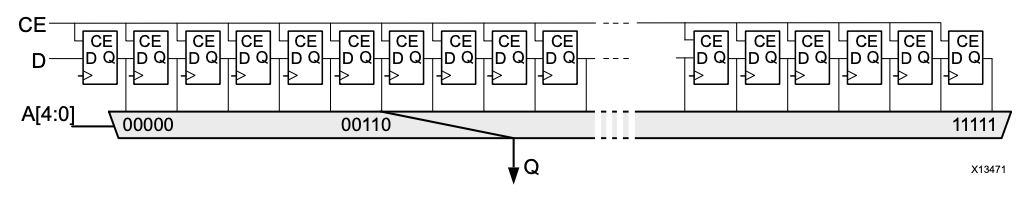

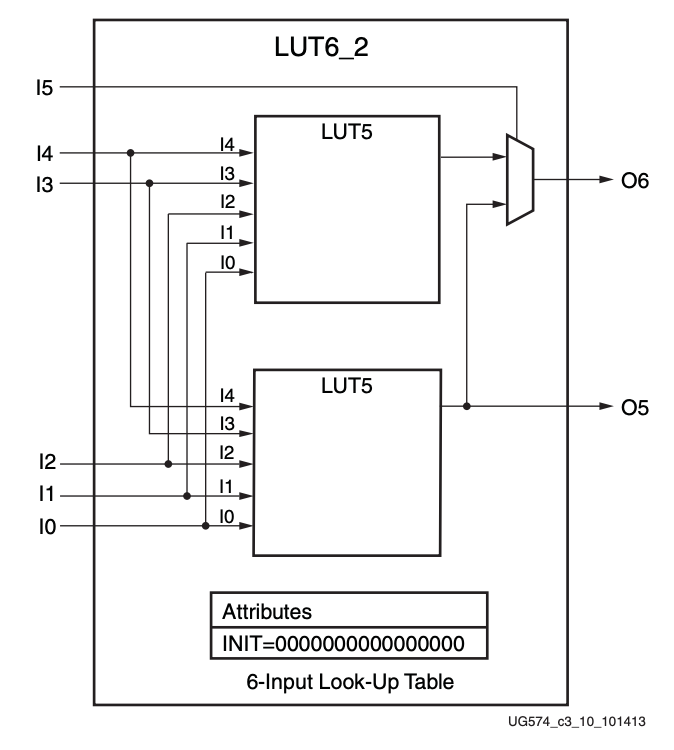

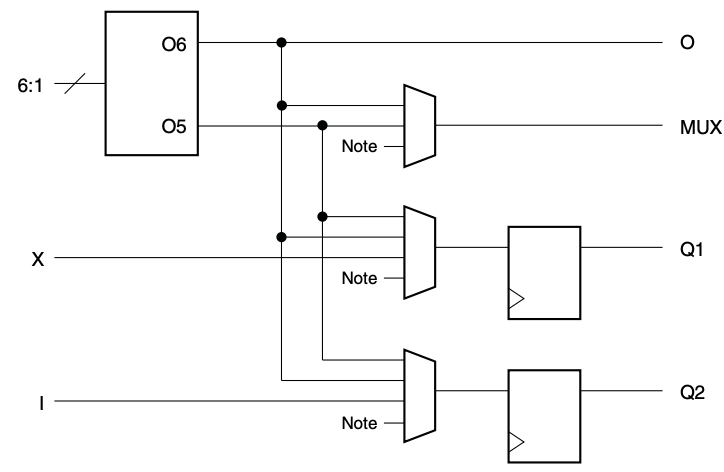

LUT

- Look-up Table

- FPGA에서 프로그래머블 하게 회로를 구성할 수 있는 핵심 원리

- MUX를 사용하여 LUT에서 출력 선택

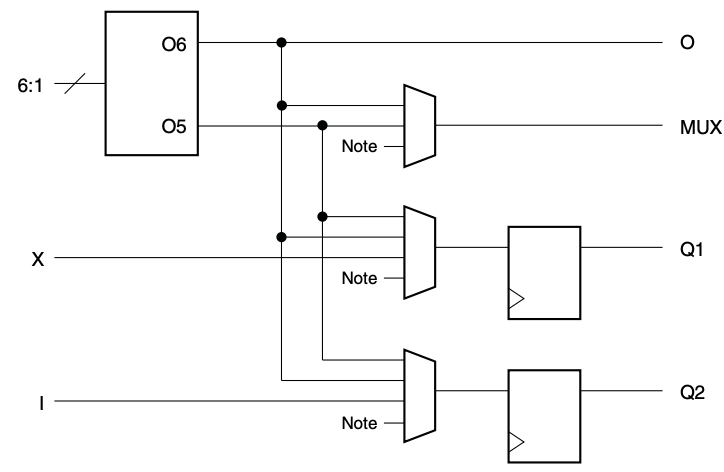

- LUT6의 출력은 바로 사용하거나 플립플롭으로 채서 사용 가능

- 슬라이스 Slice

- 8개의 로직 생성기 (Look-up tables) (6-input LUT)

- 16개의 플립플롭 (Storage elements) (=2x8)

- 멀티플렉서 (Wide-function multiplexers)

- 캐리 로직 (Carry logic)

- SLICEM (Memory)

- distributed RAM으로 데이터를 저장할 수 있는 기능과 시프트 레지스터 기능을 제공

- SLICEM 타입의 CLB를 CLE_M

- SLICEL (Logic)

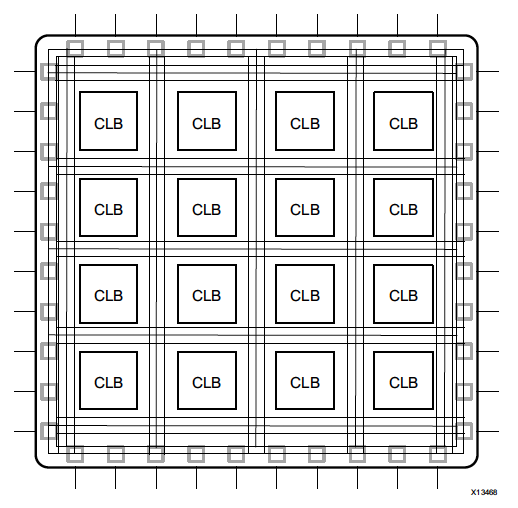

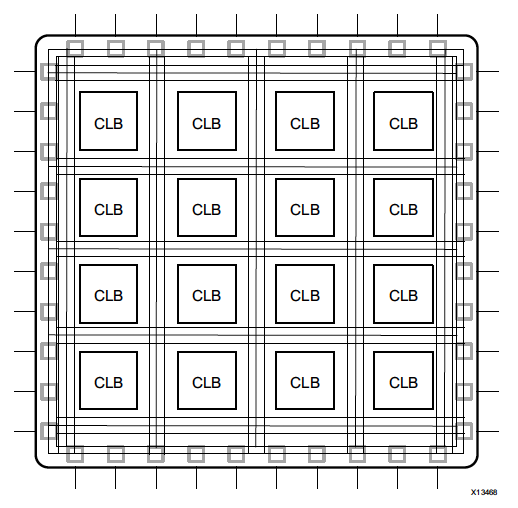

CLB

- Configurable Logic Blocks

- 하나의 슬라이스가 있음.

- Flip-Flop (FF)

- Look-up Table (LUT)

- Multiplexer

- Carray chain block

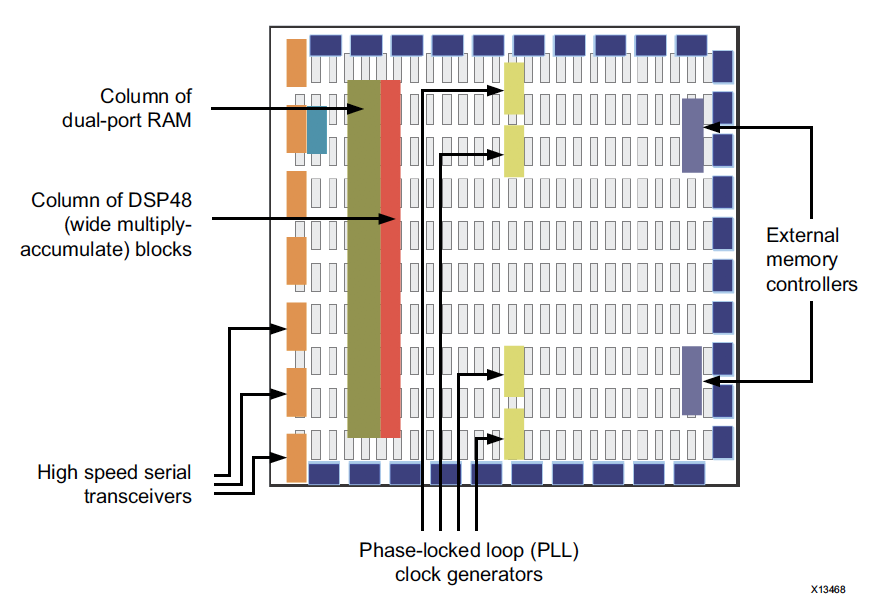

DSP

- Xilinux FPGA의 DSP 블록은 CPU에 있는 ALU (Arithmetic Logic Unit)과 같은 역할

- 덧셈기/뺅셈기

- 곱셈기 (Multiplier)

- 덧셈/뺄셈기/누산기 (Accumulator)

FPGA Storage Element

- Distributed RAM

- 6-input LUT에 있는 64개의 LUT를 사용하여 64비트 저장

- 한 슬라이스에는 8개의 6-input LUT가 있으므로 이를 사용하면 총 512비트의 값을 저장

- BRAM (Block RAM)

- On-Chip 메모리로 FPGA의 fabric 상에 위치하는 dual-port RAM

- dual-port RAM : 한 사이클에 2개의 주소로부터 값을 읽거나 쓰기가 가능

- 보통 BRAM 하나는 18K 비트나 36K 비트를 저장 가능

- 메모리가 칩 위에 있기 때문에 버스(Bus)를 사용하지 않고 바로 메모리에 접근할 수 있음

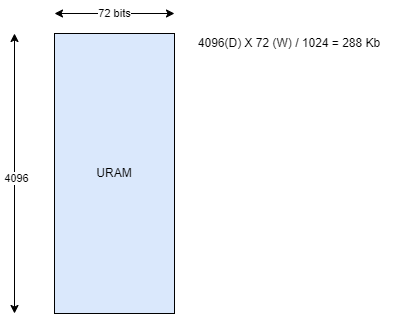

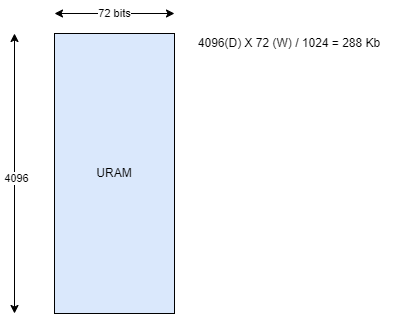

- URAM (Ultra RAM)

- UltraScale+ 이상의 제품군에만 있는 dual-porl On-Chip 메모리

- 288K 비트를 저장 가능

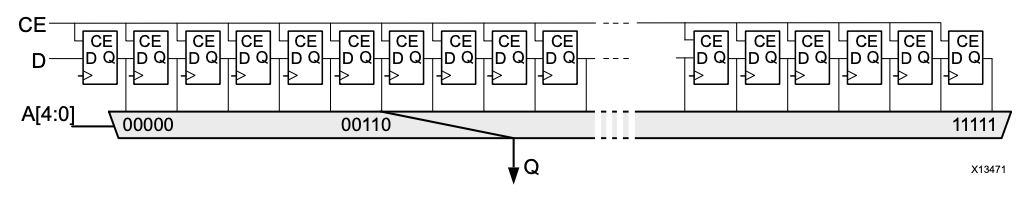

- Shift Register

- 레지스터들을 연결해둔 것

- 영상이나 음성처리에서 필터링을 수행하는 경우 이전의 입력을 사용하는 경우가 많은데 이 경우 이전 값을 효과적으로 저장하고 이를 재사용하기 위해 사용