💎 용량에 따른 주소 비트 수

-

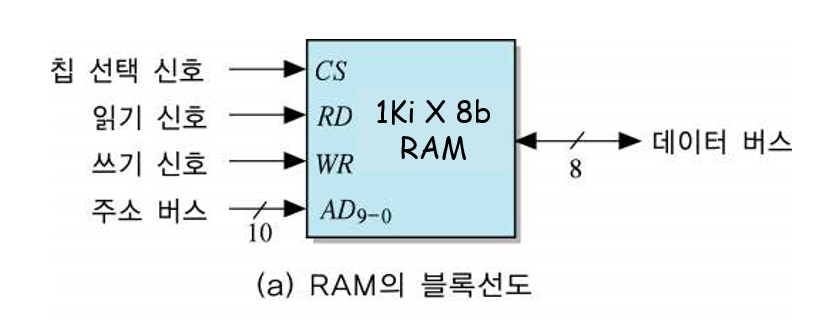

8Kib RAM : 1Ki * 8b 조직인 경우, 주소는 10b 필요 / 왜냐하면 8b는 현재 메모리의 가로이고, 1Ki가 메모리의 세로이기 때문이다.

-

1Mib RAM : 128Ki * 8b 조직인 경우, 주소는 17b 필요

-

1Gib RAM : 128Mi * 8b 조직인 경우, 주소는 27b 필요

💎 RAM의 내부 조직

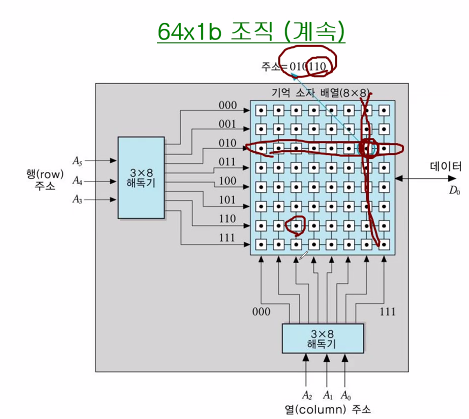

- 64x1b 조직으로 해독기를 두개로 나눴다. 64x1b 조직 같은 경우 6x64 디코더를 사용한다. / 장방형 배열

-

위처럼 해독기를 행주소, 열주소로 바꿔주게 되면 열결 선이 줄어들게 된다.

위처럼 선이 물리적으로 들어가게 되는데 이러한 칩은 작게 만들어야 한다. 그런 측면에서 선이 늘어나면 만들기가 쉽지 않기 때문에 위처럼 나누는 것이 좋다.

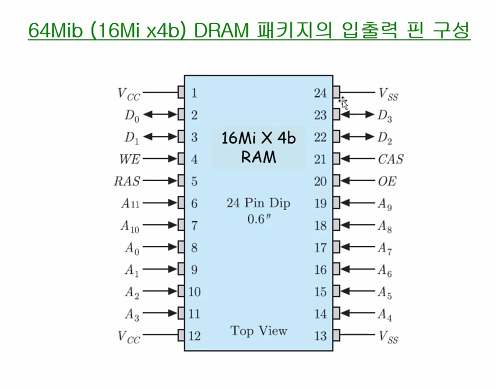

WE : 라이트 인에이블 (Write 읽기)

OE : 아웃풋 인에이블 (Read 읽기)

D : 데이터선(bit) -> 4개 있으면 4개 비트

A : 주소선 -> 3개를 통해서 8개의 주소를 표현함 -

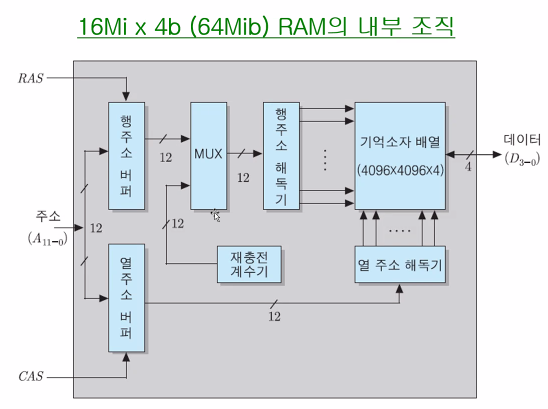

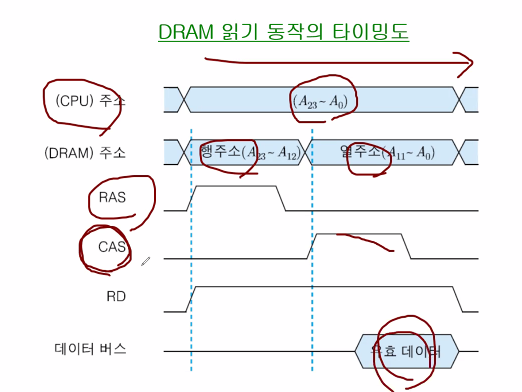

DRAM 일긱 동작의 타이밍도

RAS - 행 주소

CAS - 열 주소

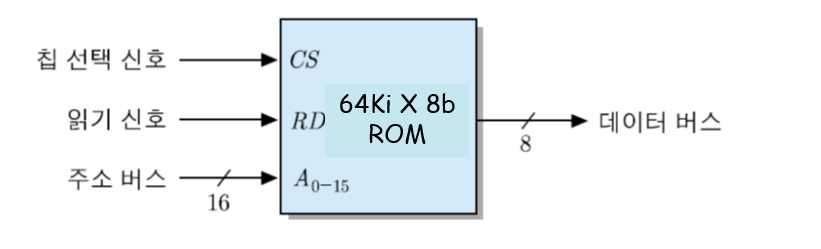

💎 ROM

-

영구 저장이 가능한 반도체 기억장치

-

읽는 것만 가능하고, 쓰는 것은 불가능(램과 다르게 쓰기 신호가 없다)

-

아래 내용들의 저장에 사용

1) 시스템 초기화 및 진단 프로그램(ex : PC의 BIOS 프로그램)

2) 빈번히 사용되는 함수들을 위한 서브루틴들

3) 제어 유니트의 마이크로프로그램

💍 ROM의 종류

1) PROM

2) EPROM

3) EEPROM

4) 플래시메모리

5) SSD : 반도체 보조저장장치(Nand Flash Memeroy로 구성) 임의접근을 하여 탐색시간 없이 고속으로 데이터 입출력 할 수 있으면서도 지연이나 실패율이 현저히 적음

💎 기억장치 모듈의 설계

💍 병렬접속

-

데이터 수가 많아진다.

-

기억장치 칩의 데이터 I/O 비트 수가 단어 길이보다 적은 경우에 사용

ex) 단어의 길이가 N이고 기억장치 칩의 데이터 I/O 비트수가 B라고 하면

N/B개의 칩들을 병렬접속 -

병렬 접속을 통해서 16x4를 두개를 사용하여 16x8이 동작하는 것처럼 만들 수 있다.

💍 직렬접속

- 주소 수가 많아진다.

출처 : 컴퓨터 구조론(개정5판)