본 글은 MSP430G2553 MCU를 기준으로 작성되었습니다.

세부적인 내용은 제품군마다 조금씩 다를 수 있습니다.

1. Basic Clock Module+ 이란?

Basic Clock Module+는 MSP430x2xx MCU에서 여러 가지 주파수의 클럭을 생성해내기 위해 지원하는 클럭 모듈이다.

2. BCM+ OSC & CLK 종류

아래의 4개의 클럭 소스를 이용하여 총 3가지의 클럭 신호를 생성해낼 수 있다.

- 클럭 소스

- LFXT1CLK - Low-frequency External Clock 1

- XT2CLK - External Clock 2

- DCOCLK - Digitally Controlled Oscillator Clock

- VLOCLK - Very Low Power Clock

XT1, 2는 보드 위에 XTAL 형태로 실장되어 있으며, DCO, VLO는 MCU 내부에 집적되어 있다.

- 클럭 신호

- MCLK - Master Clock

- SMCLK - Sub-main Clock

- ACLK - Auxiliary Clock

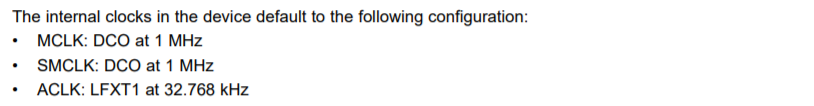

User guide 문서를 보면 아래와 같이 나와있다. 세부 내용이 궁금하다면 참고하자.

MSP430G2553에서는 클럭 초기값으로 아래와 같이 설정된다.

3. 클럭 다이어그램

각 클럭 신호가 만들어지는 방법은 아래와 같다. 원하는 클럭 소스를 선택한 후, 제산기를 거쳐 원하는 주파수의 클럭 신호가 만들어진다.

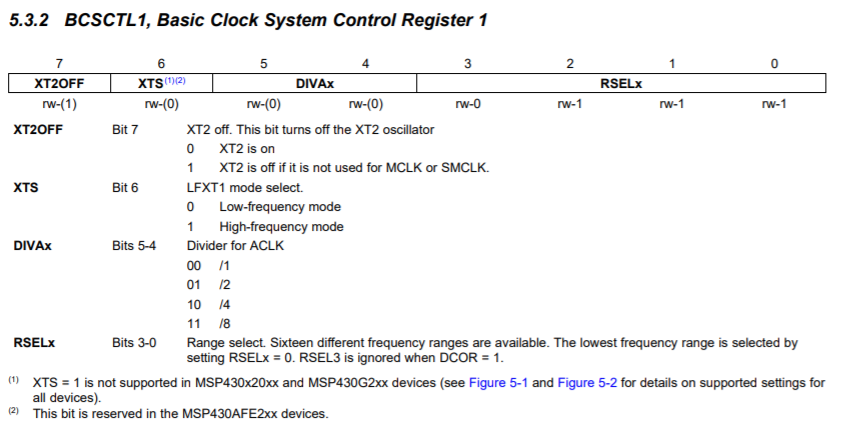

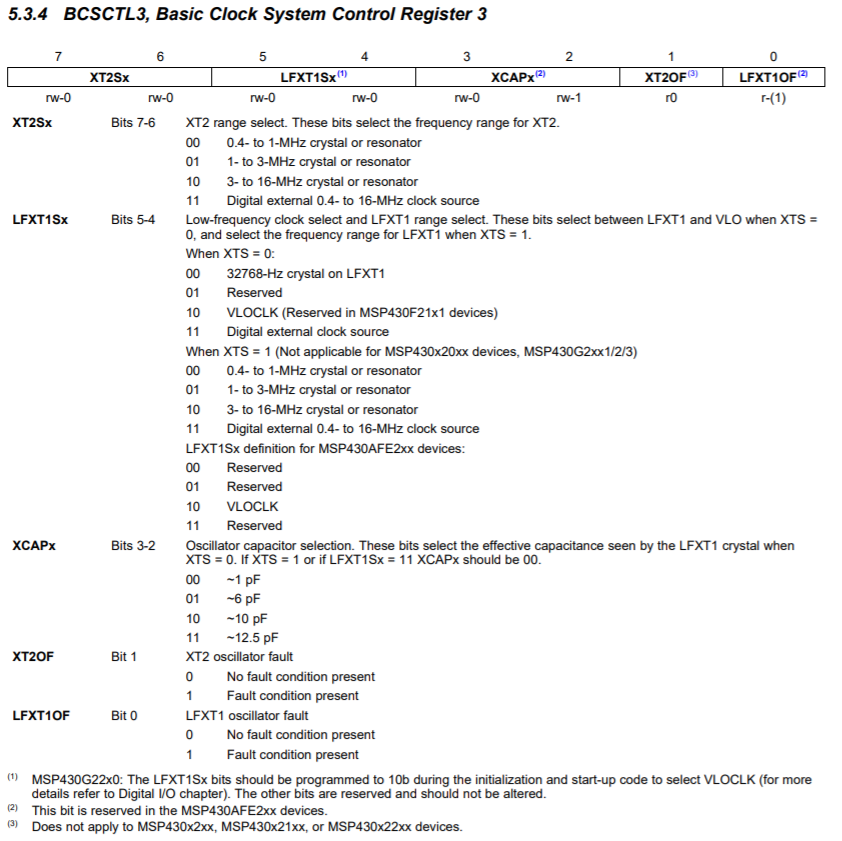

4. 관련 레지스터

사용자 입장에서 원하는 주파수의 클럭을 만드는 방법은 클럭과 관련된 레지스터를 이용하는 것이다. MSP430에서는 위에 나열한 클럭 소스의 선택, 제산기의 제수, 클럭의 활성화 여부를 레지스터 연산을 통해 제어할 수 있다.

MSP430x2xx에서 사용되는 레지스터는 총 6개로, 아래와 같다.

- DCOCTL - Digitally Controlled Oscillator Control Register

- BCSCTL1 - Basic Clock System Control Register 1

- BCSCTL2 - Basic Clock System Control Register 2

- BCSCTL3 - Basic Clock System Control Register 3

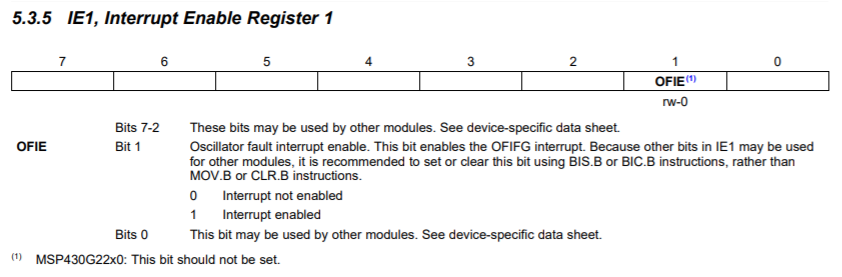

- IE1 - Interrupt Enable Register 1

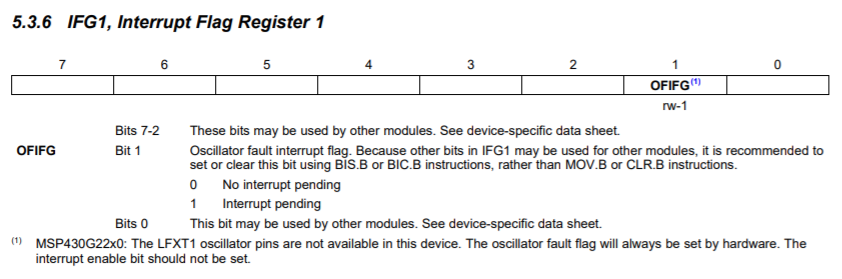

- IFG1 - Interrupt Flag Register 1

그리고 각 레지스터의 명세는 아래와 같다.

1. DCOCTL

2. BCSCTLx

5. IE1

6. IFG1

위 스크롤을 넘기고 왔다면 아마 누구나 이렇게 말할 것이다.

"으아 이게 대체 뭐람!? 클럭 좀 조절하고 싶으면 위의 레지스터들의 명세를 다 꿰고 있어야 한다는 거야!?"

필자가 보기에도 클럭 관련 설정들이 레지스터 안에 보기 좋게 정렬되어 있다는 느낌은 들지 않는다. 특히 어떤 비트가 다른 레지스터의 어떤 비트에 종속되어 적용되는 등의 부분들이 사용자가 보기에 한눈에 쉬워 보이진 않는다. 물론 명세를 모두 이해한다면 MSP430x2xx에서 제공하는 클럭에 관한 모든 기능들을 다룰 수 있는 것은 맞을 것이다.

이해하기 어렵다면 몇 가지 클럭 관련 소스 코드들을 레퍼런스로 삼아서 원하는 클럭 동작을 만드는 것을 추천한다.

5. 예제

MSP430Ware에서 제공하는 예제 두 개를 보자.

- 클럭 기본값을 확인하는 예제

- MCLK = 8MHz, ACLK = 32kHz로 설정하는 예제

- MCLK = VLO/8, ACLK = VLO, SMCLK = n/a로 설정하는 예제

1. 클럭 초기값 확인

TI MCU에서는 클럭을 특정 GPIO 핀을 통해 클럭을 출력할 수 있다. 이 기능을 이용하여 출력되는 MCLK, SMCLK, ACLK을 확인해보자.

참고로 POR 이후 아무 설정도 하지 않으면 MCLK, SMCLK, ACLK은 초기값으로 설정된다. 기본적으로 MCLK과 SMCLK은 DCOCLK을 소스로 사용하며, 주파수는 1MHz로 설정된다. ACLK은 LFXT1CLK을 소스로 사용하며, 주파수는 32.768kHz로 설정된다.

#include <msp430.h>

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // 와치독 비활성화

P1DIR |= 0x13; // P1.0, P1.1, P1.4를 output으로 설정

P1SEL |= 0x11; // P1.0, P1.4 핀을 AF로 설정

while(1)

{

P1OUT |= 0x02; // P1.1에 출력값을 1로 설정

P1OUT &= ~0x02; // P1.1에 출력값을 0으로 설정

}

}MSP430G2553은 P1.0, P1.4 핀에 특수 기능으로 각각 ACLK, SMCLK을 가지고 있다. 따라서 해당 핀의 속성을 output + AF로 설정하면 해당 핀으로부터 ACLK, SMCLK이 각각 출력되는 것을 볼 수 있다.

다만 MCLK은 MSP430G2553에서는 따로 AF로 할당된 핀이 없는데, 이는 메인 문에서의 while 루프를 통해 대체할 수 있다. 위 while 루프를 실행하면 실제로는 DCOCLK이 아니나 DCOCLK/10의 주파수로 LED가 깜빡이는 것을 볼 수 있는데, MSP430Ware에는 설명이 나와있지 않지만, 추측건대 while 루프를 처리하는 데에 드는 클럭이 총 10사이클이 들어서 그런 게 아닌가 싶다.

테스트 결과는 오실로스코프를 통해 확인할 수 있다. 다만 필자는 집에 오실로스코프가 없어서 파형을 찍어볼 순 없었다.. (있는게 더 이상하지만.)

2. MCLK = 8MHz

이번에는 MCLK의 주파수를 8MHz로 설정해보자.

#include <msp430.h>

int main(void)

{

WDTCTL = WDTPW | WDTHOLD;

if (CALBC1_8MHz == 0xFF || CALDCO_8MHz == 0xFF)

{

while (1);

}

BCSCTL1 = CALBC1_8MHz;

DCOCTL = CALDCO_8MHz;

while (1);

}위의 코드를 실행하면 BCS1, DCO 레지스터 연산에 의해 MCLK의 주파수가 8MHz로 설정된다. ACLK는 별도의 설정을 하지 않았으므로 32.768Khz를 유지한다.

3. MCLK = VLO/8, ACLK = VLO

이번에는 MCLK의 소스를 VLOCLK으로 선택한 후 8로 나누어서 사용하도록 해보자.

#include <msp430.h>

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // 와치독 비활성화

BCSCTL3 =|= LFXT1S_2; // LFXT1의 출력을 VLO로 선택

IFG1 &= ~OFIFG; // OSC Fault Flag 클리어

__bis_SR_register(SCG1 + SCG0); // DCO 정지 (안쓰는 OSC 끄려는 목적)

BCSCTL2 |= SELM_3 + DIVM_3; // MCLK = LFXT1/8 = VLO/8 로 설정

while (1);

}클럭 다이어그램과 관련 레지스터를 참고하여 위와 클럭을 설정할 수 있다.

이 밖에도 MSP430Ware에 여러 가지 예제가 있으니 필요하다면 참고하도록 한다.