1. UART 컨트롤러란?

UART 컨트롤러란 UART 통신 프로토콜에 맞춰 데이터를 송수신하기 위해 사용되는 하드웨어를 말한다. 보내고자 하는 데이터를 프로토콜에 맞춰 비트 단위로 변환하여 TX 라인으로 보내고, RX 라인으로 수신한 비트스트림을 데이터로 복원하는 기능을 한다.

2. UART 컨트롤러 구조

설계하기 나름이지만, UART 컨트롤러는 기본적으로 세 부분으로 이루어진다.

UART 컨트롤러 구성 요소

- 보레이트 생성기 (Baudrate Generator)

- 송신 모듈 (Transmitter)

- 수신 모듈 (Receiver)

각 부분에 대해 하나씩 살펴보자.

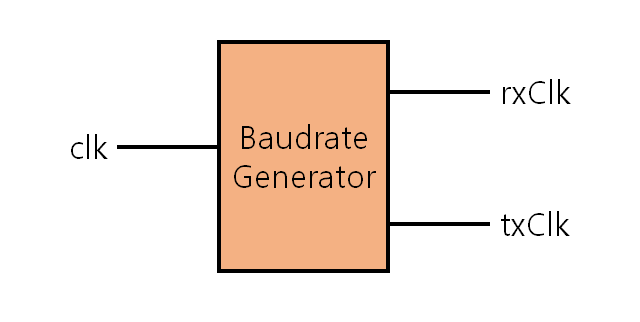

1. 보레이트 생성기 (Baudrate Generator)

보레이트 생성기는 외부 클럭 신호를 받아서 Tx, Rx 모듈에서 사용되는 클럭을 생성하는 역할을 한다.

그림으로 나타내면 아래와 같다.

외부 클럭에 보레이트 계산식을 적용하여 Tx, Rx 클럭을 내보내면 된다.

계산식은 아래와 같다.

(공식)

외부 클럭이 100MHz이고 보레이트가 115200이라면 생성되는 클럭 주기는 ?이다. 다만 Rx의 경우는 오버샘플링 사용 여부에 따라 더 짧은 주기가 사용되기도 한다.

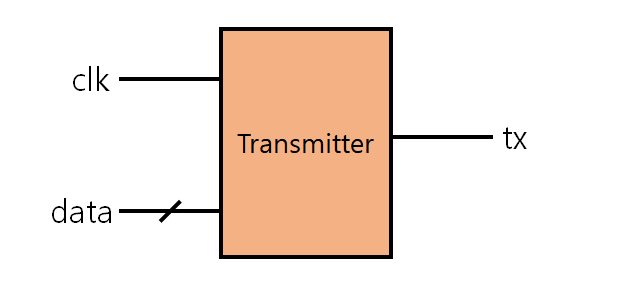

2. 송신 모듈 (Transmitter)

송신 모듈은 보내고자 하는 데이터를 UART 프로토콜에 맞춰 비트열로 변환하고, 입력되는 클럭에 맞춰 한 비트씩 Tx 라인으로 내보내는 역할을 한다.

그림으로 나타내면 아래와 같다.

모듈 내부에서 상태 머신을 이용해 동작이 제어되며, 보내고자 하는 데이터를 입력으로 받아 Tx 라인으로 출력한다. 데이터 라인 외에 busy나 done 같은 제어 라인도 있을 수 있다.

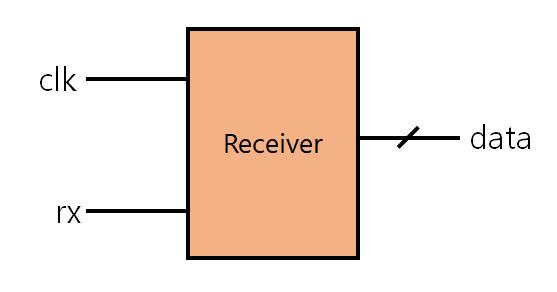

3. 수신 모듈 (Receiver)

수신 모듈은 Rx 라인으로 신호를 수신하여 이를 원래의 데이터로 복원하는 역할을 한다.

그림으로 나타내면 아래와 같다.

모듈 내부에서 상태 머신을 이용해 동작을 제어하며, Rx 라인으로 수신한 신호를 원래의 데이터로 복원한다. 데이터 라인 외에 busy나 done, err 같은 제어 라인도 있을 수 있다.

상용 UART 컨트롤러는 Prescaler나 Bus Interface 등이 더 붙기 때문에 좀 더 복잡하게 생겼지만 위에는 핵심 구성 요소만 설명하였다.

그리고 아래 내용 추가해야 함.

UART Configuration

- Baudrate

- Word length

- Stop bits

- Parity

- Duplex

- Oversampling