Verilog

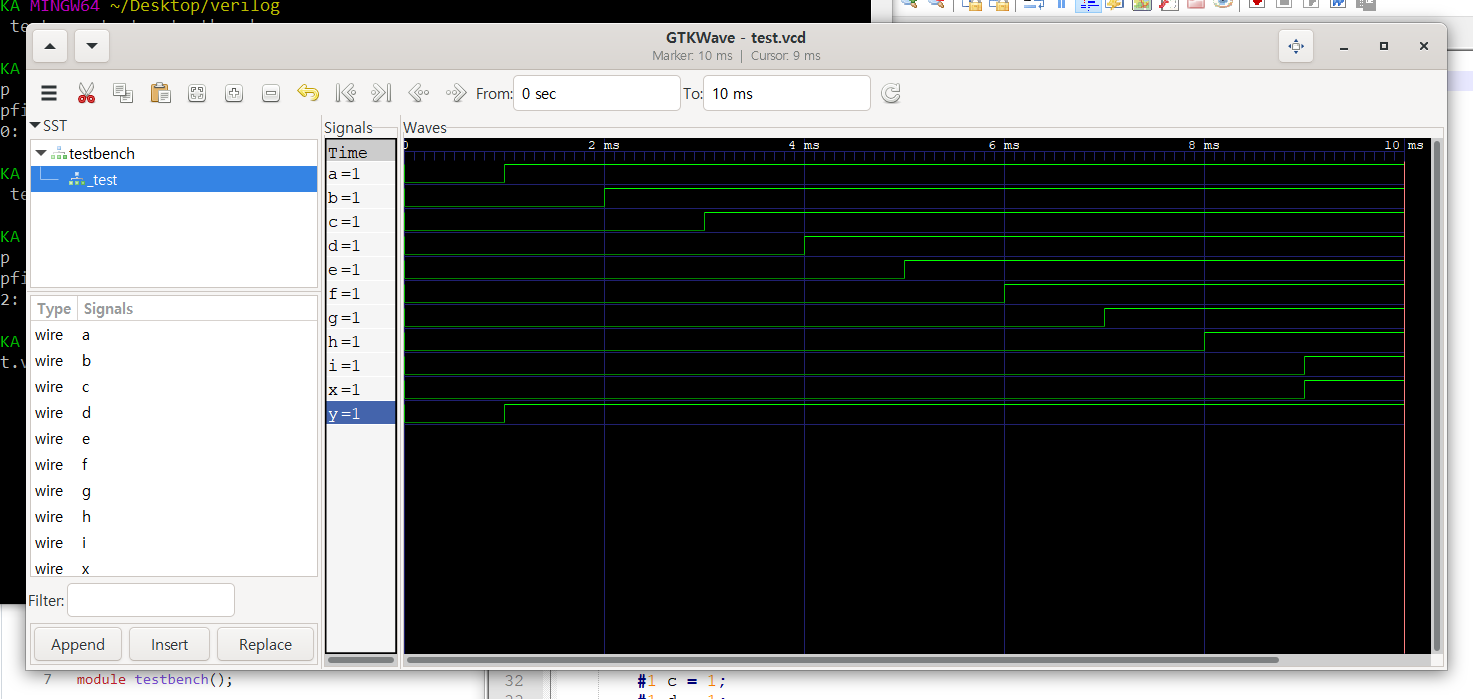

1.[Verilog] 프롤로그 - Icarus Verilog & GTKWave 개발 환경 설정 on Windows 10

Verilog 문법 및 간단한 모듈 작성법에 대해 글을 쓰기로 하였다.개발 환경은 아래와 같다.Windows 10 x64Icarus Verilog v12.0 (iverilog)GTKWave Analyzer v3.3.108 (gtkwave)Icarus Verilog 다운

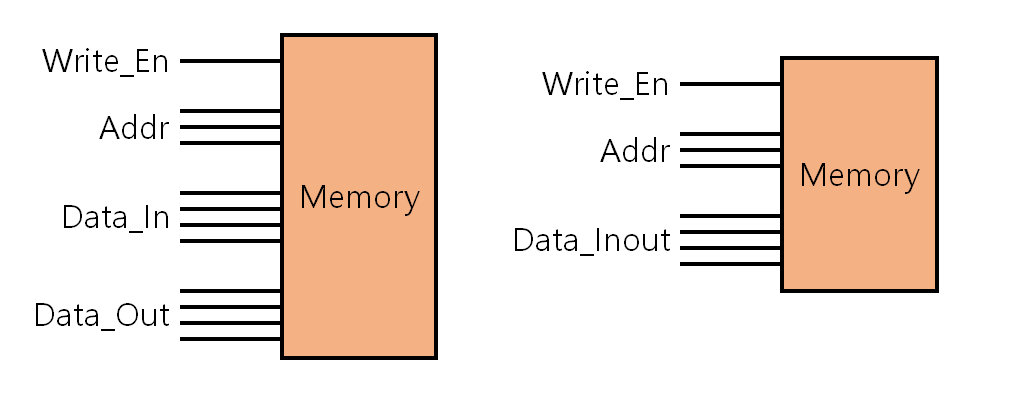

2.[Verilog] Inout 사용법

메모리를 그림으로 간단히 그려보았다.Inout 핀을 사용하는 이유는 대개 핀 개수를 줄이기 위해서이다. 대부분의 통신 프로토콜들은 Input 핀과 Output 핀을 전용으로 나누지만, 일부 프로토콜에서는 Inout 핀을 사용하기도 한다.Inout 핀으로도 통신 프로토콜

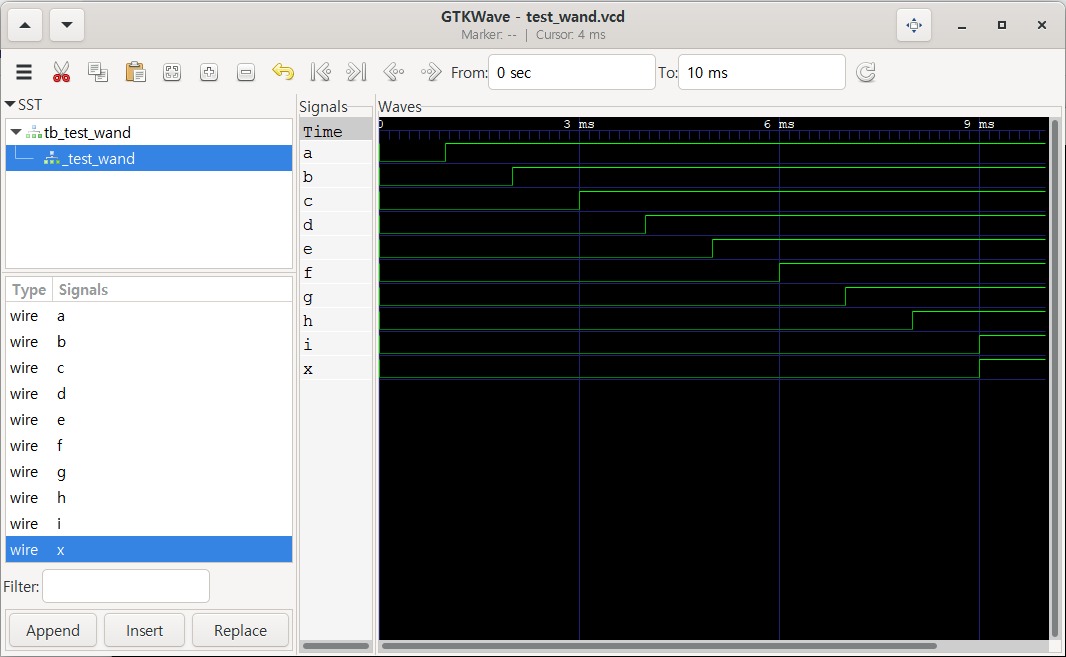

3.[Verilog] 생소한 자료형 정리 (1) - net 자료형

Verilog의 자료형에는 두 가지 종류가 있다.net 자료형 \- wire, tri, wand, wor, triand, trior, supply0, supply1, tri0, tri1, triregvariable 자료형 \_ reg, integer, real, t

4.[Verilog] Procedural Assignment, Continuous Assignment

Procedural Assignment은 절차적 할당이라고 하며, initial이나 always 등과 같은 event block 내에서 값을 할당하는 것을 말한다.아래의 예제를 보자.always block에서 값을 할당한 것을 볼 수 있다.event block 안에서는

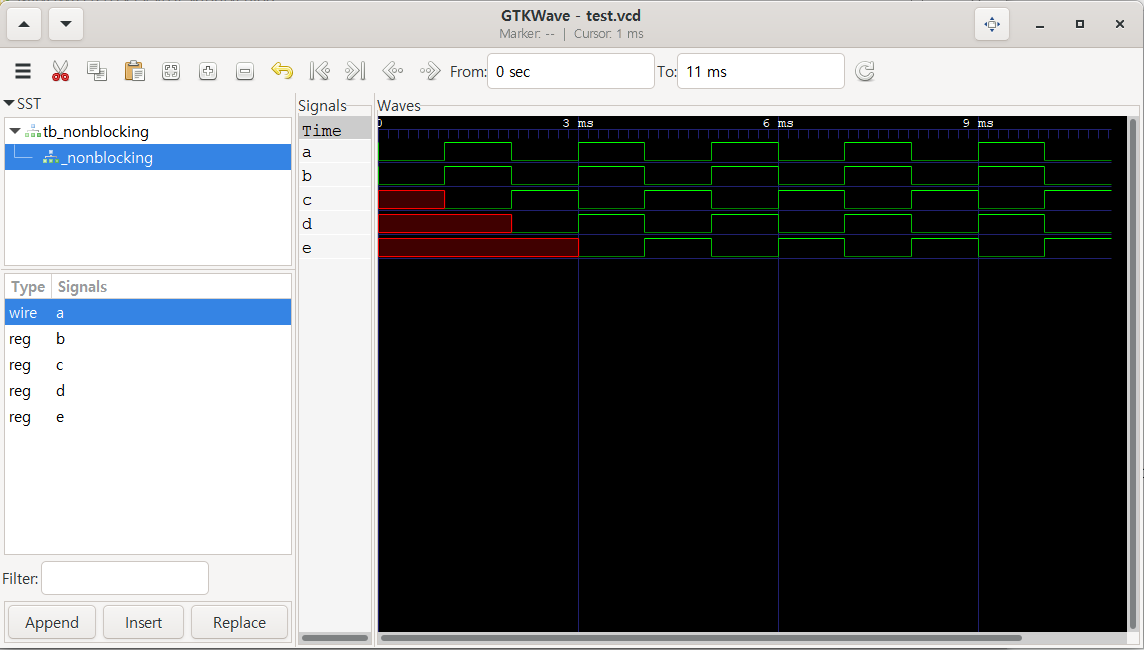

5.[Verilog] Blocking Assignment, Non-blocking Assignment

Blocking Assignment는 해당 라인이 실행될 때 뒤에 있는 Assignment들을 잠시 블로킹하는 특성을 가지고 있다.인터넷에 둘을 비교한 내용이 많지만, 파형으로 직접 확인해보고 싶었다.아래의 예제를 보자.b=a 부분이 실행되는 동안 뒤에 있는 c=b,

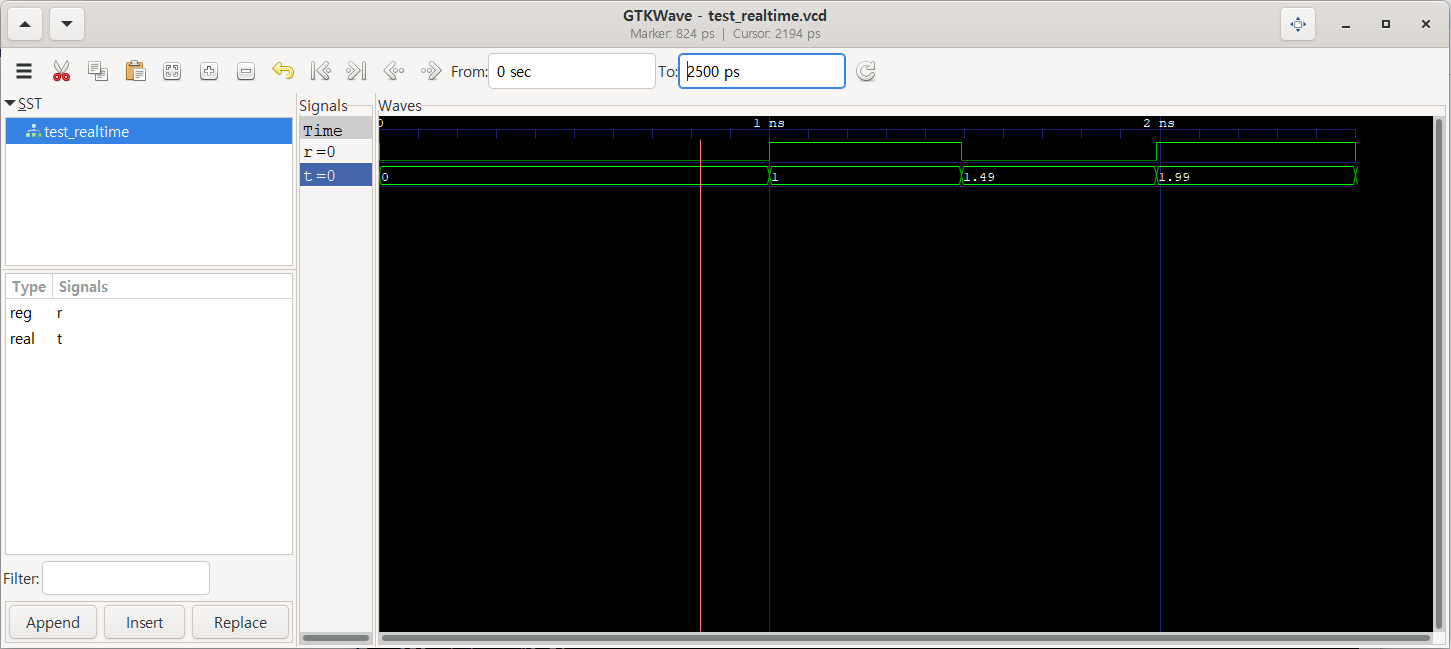

6.[Verilog] 생소한 자료형 정리 (2) - variable 자료형

Verilog의 자료형에는 두 가지 종류가 있다.net 자료형 \- wire, tri, wand, wor, triand, trior, supply0, supply1, tri0, tri1, triregvariable 자료형 \- reg, integer, real, t

7.[Verilog] UART 컨트롤러를 만들어 보자 (1) - 개념 및 구조 파악

UART 컨트롤러란 UART 통신 프로토콜에 맞춰 데이터를 송수신하기 위해 사용되는 하드웨어를 말한다. 보내고자 하는 데이터를 프로토콜에 맞춰 비트 단위로 변환하여 TX 라인으로 보내고, RX 라인으로 수신한 비트스트림을 데이터로 복원하는 기능을 한다.설계하기 나름이지

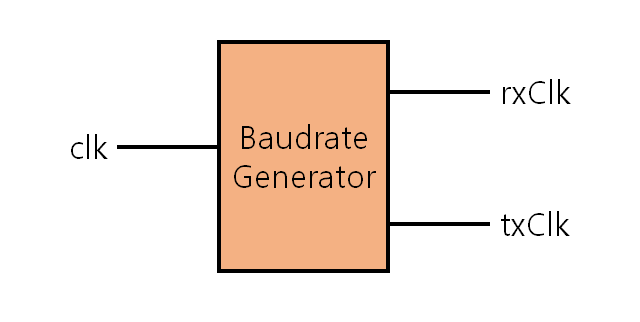

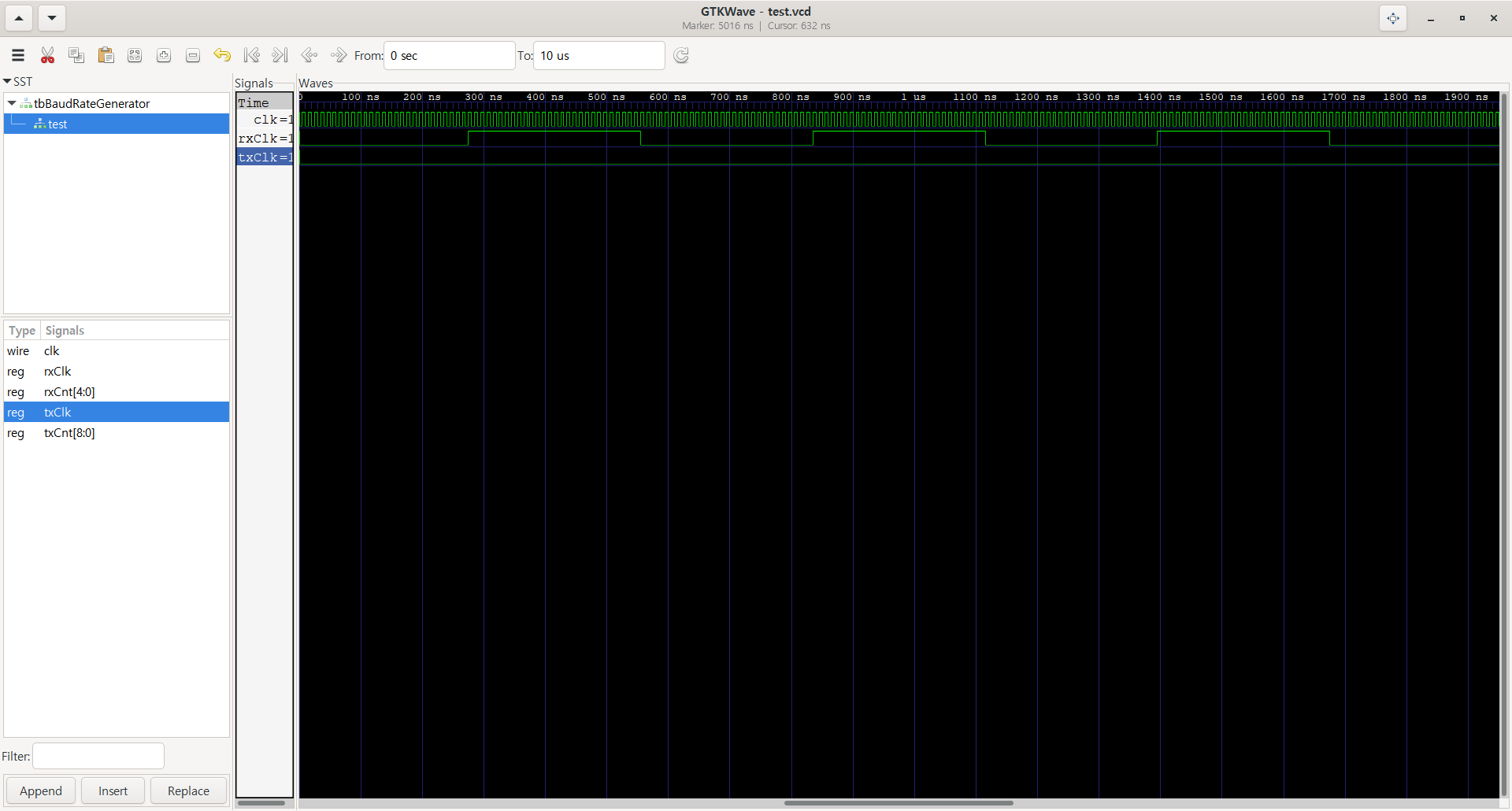

8.[Verilog] UART 컨트롤러를 만들어 보자 (2) - 보레이트 생성기 구현

Verilog HDL로 각 모듈을 하나씩 만들어 보자.첫 번째로 보레이트 생성기를 만들어 보자.먼저 각 모듈에서 사용할 매크로를 정의하자.Defines.vh입력 클럭, 보레이트, 오버샘플링 등 사용자가 가변적으로 설정할 수 있는 값들을 따로 매크로 파일로 빼서 관리하도

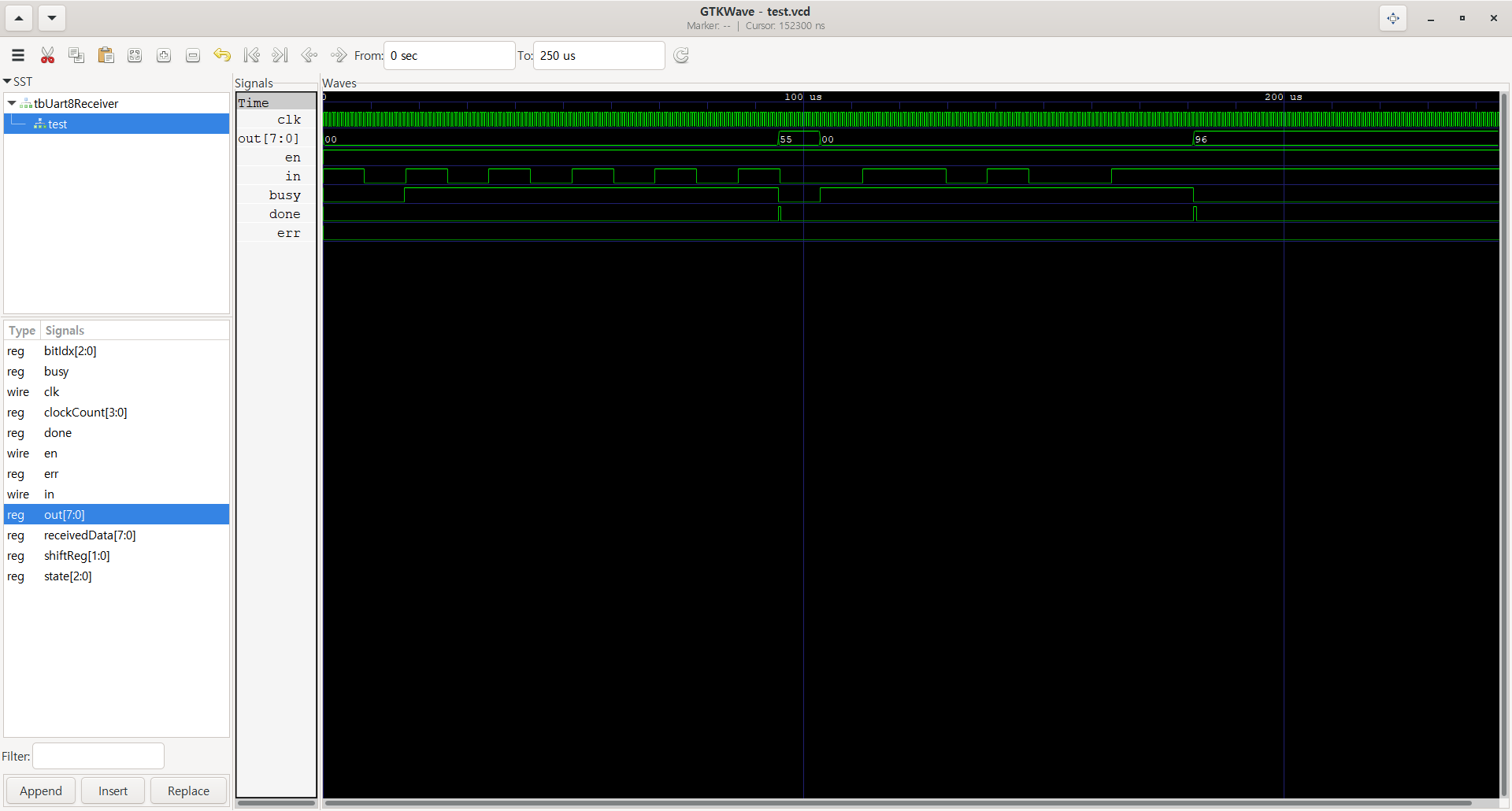

9.[Verilog] UART 컨트롤러를 만들어 보자 (3) - 수신기 구현

Verilog HDL로 각 모듈을 하나씩 만들어 보자.두 번째로 수신기를 만들어 보자.아래 글에서 구현한 매크로 파일을 이용한다.\[https://velog.io/@pikamon/Verilog-10RTL 모듈을 만들어 보자.Uart8Receiver.vstate

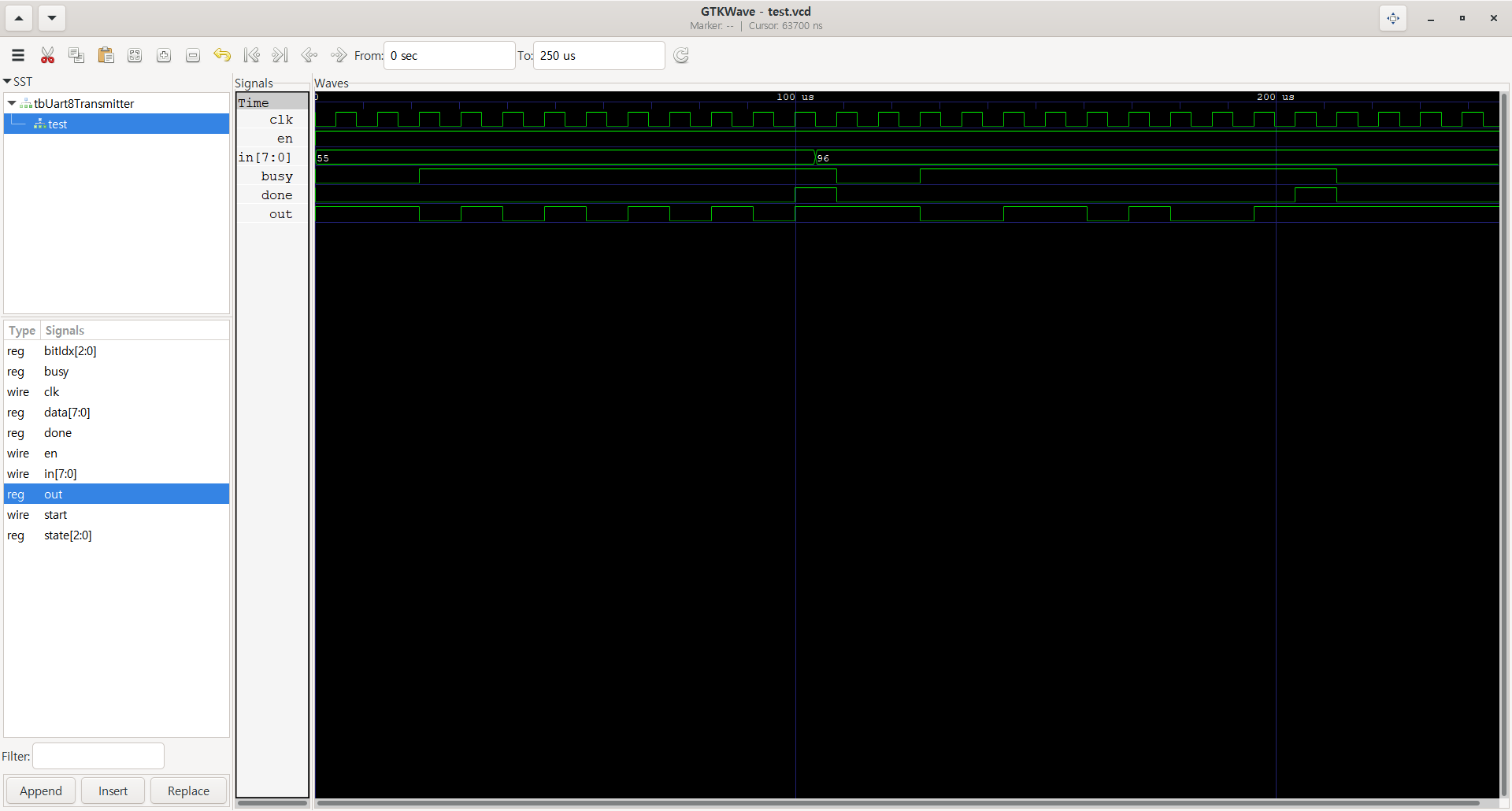

10.[Verilog] UART 컨트롤러를 만들어 보자 (4) - 송신기 구현

Verilog HDL로 각 모듈을 하나씩 만들어 보자.세 번째로 송신기를 만들어 보자.아래 글에서 구현한 매크로 파일을 이용한다.\[https://velog.io/@pikamon/Verilog-10RTL 모듈을 만들어 보자.Uart8Transmitter.v수신

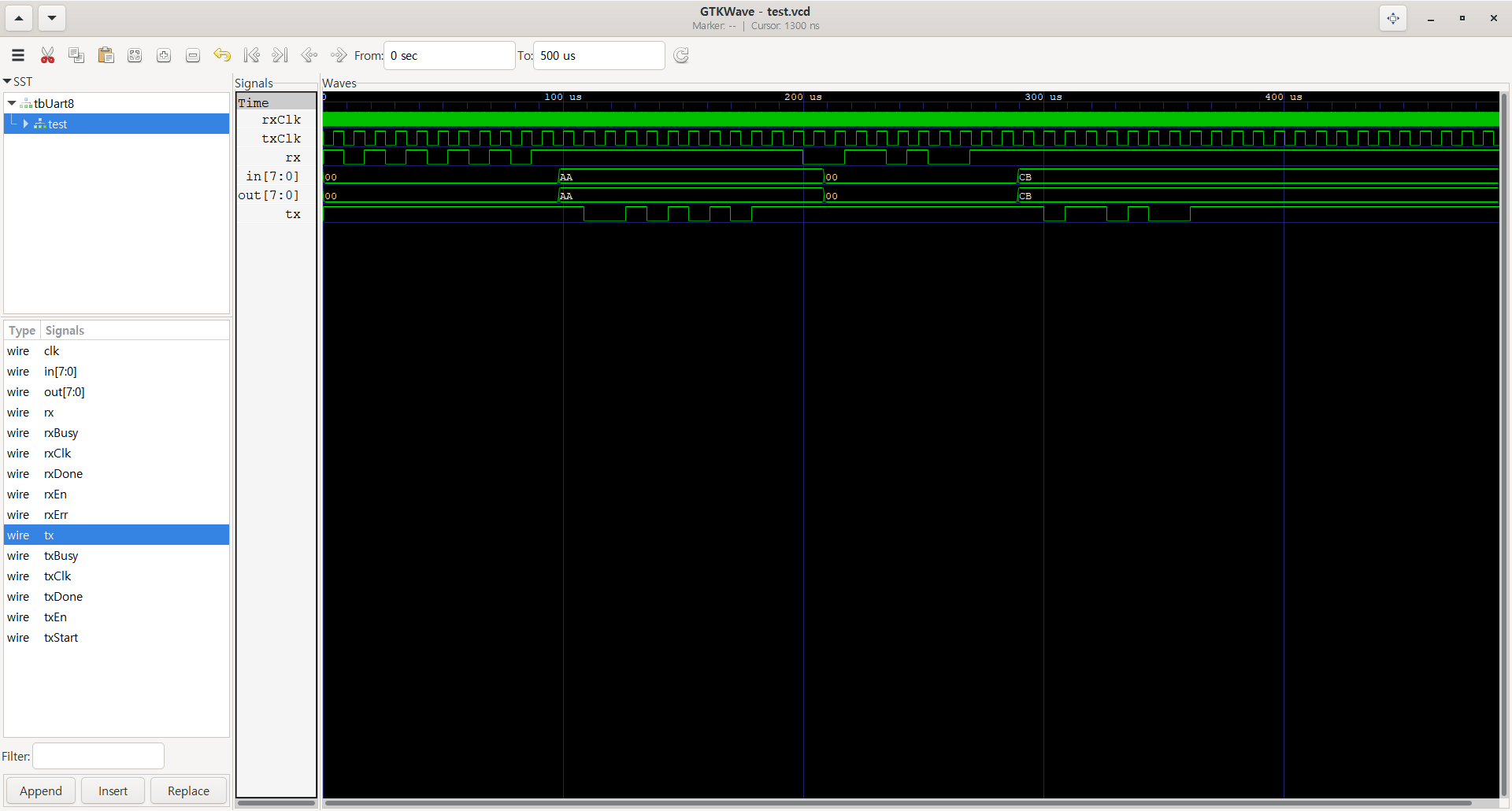

11.[Verilog] UART 컨트롤러를 만들어 보자 (5) - Top 모듈 구현

아래 글에서 각 모듈을 구현하여 검증하였다.https://velog.io/@pikamon/Verilog-10https://velog.io/@pikamon/Verilog-11https://velog.io/@pikamon/Verilog-12이제

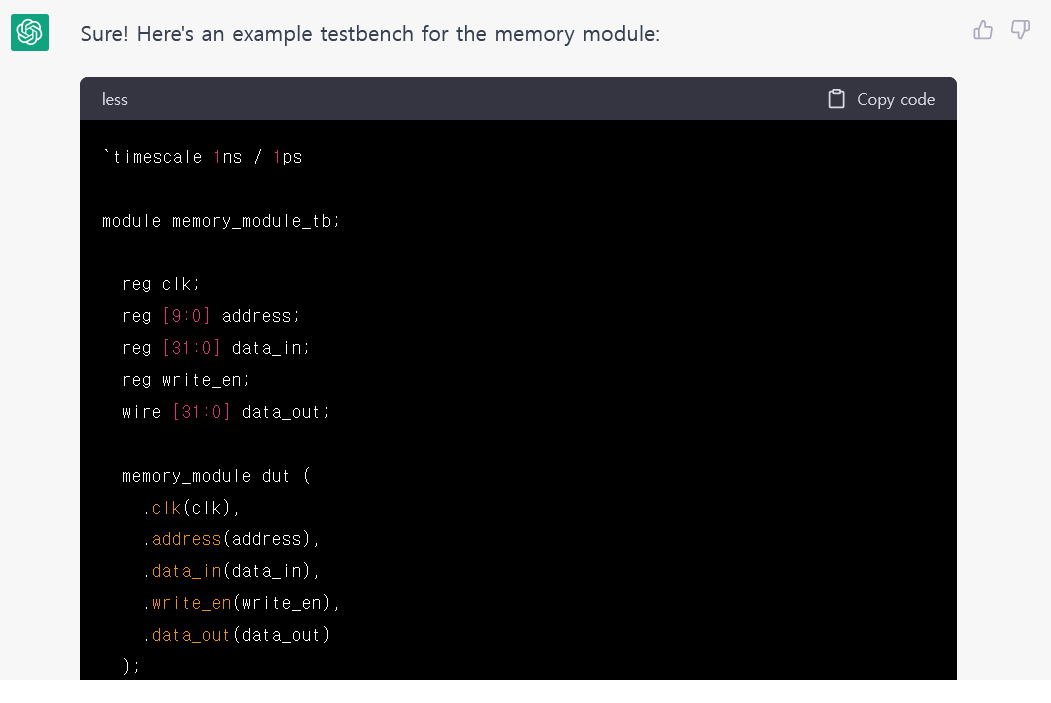

12.[Verilog] ChatGPT로 만들어본 32-bit 메모리 모듈

어제 처음 ChatGPT를 써봤는데, 얘가 프로그래밍 소스 코드를 생성해준다...Verilog 할 줄 아냐고 물어봤는데 "Sure!" 라고 하길래, 32-bit 1KB 짜리 메모리 모듈 만들어달라고 하니까 얘가 실제로 만들어줬다.. 심지어 testbench도 만들어달라