CMOS VLSI DESIGN

집적회로

IC(Integrated Circuits)는 수많은 수동소자와 능동소자를 고밀도로 집적시켜 하나의 칩으로 만드는 것입니다. 과거에는 전자회로기판에 소자들과 wire를 이용해 만들었지만 기술의 발전으로 기판+소자+wire를 One Chip에 만들 수 있게 되었습니다.

- SSI(Small Scale Integration)

- MSI(Middle Scale Integration)

- LSI(Large Scale Integration)

- VLSI(Very Large Scale Integration)

- ULSI(Ultra Large Scale Integration)

- SoC(System on Chip) : 전체의 System을 하나의 Chip에 포함되어 있는 것을 의미합니다.

IC와 CMOS를 사용하는 이유는 Fast, Cheap, Low power의 장점을 가지기 때문입니다.

반도체

주로 4족 원소인 Si이 사용되며 주변 Si들과 공유결합을 이루고 있습니다. 또한 특정 조건에 따라 전도성이 달라지는 물질입니다. 불순물이 첨가되지 않은 Intrinsic 반도체는 electron과 hole이 같은 개수로 존재합니다. 따라서 부도체의 성질을 가지고 있습니다. 그러나 불순물이 doping된 Extrinsic 반도체에서 electron과 hole은 다음과 같습니다.

3족 doping : p-type

5족 doping : n-type

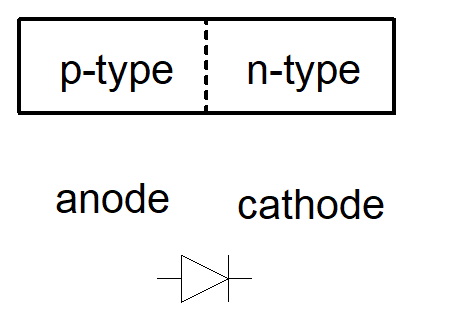

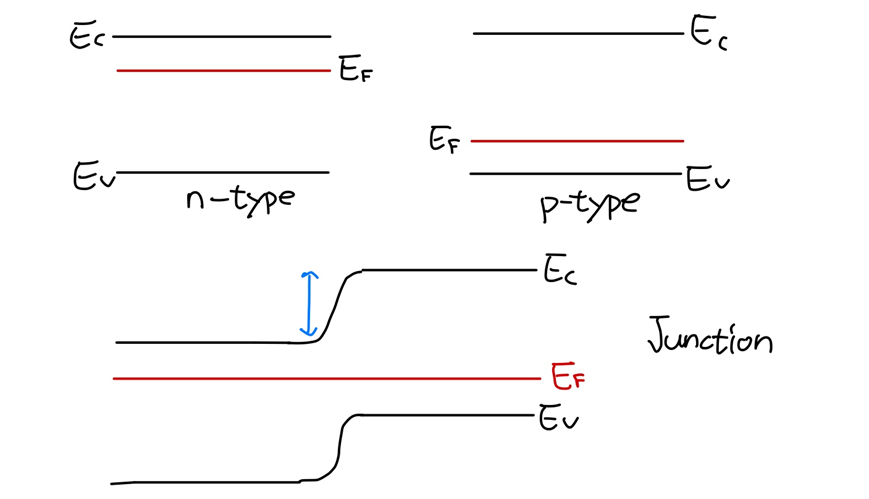

PN-Junction

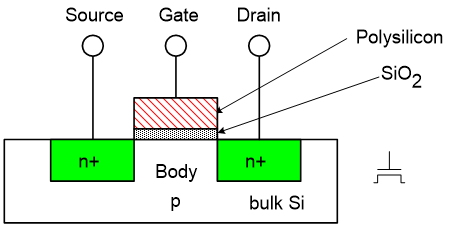

MOSFET

MOSFET(Metal Oxide Semiconductor Field Effect Transistor)은 수직으로 Metal Oxide Body로 이루어져 있고 수직 전계(Field)가 발생하여 channel이 형성되는 효과(Effect)가 있습니다. 수평으로는 Source Body Drain으로 이루어져 있고 수평 전계(Field)가 발생하여 channel을 통해 전류가 흐르는 효과(Effect)가 있습니다. 그리고 Gate, Source, Drain, Body 4개의 단자로 이루어져 있습니다.

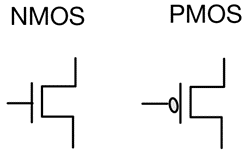

Symbol

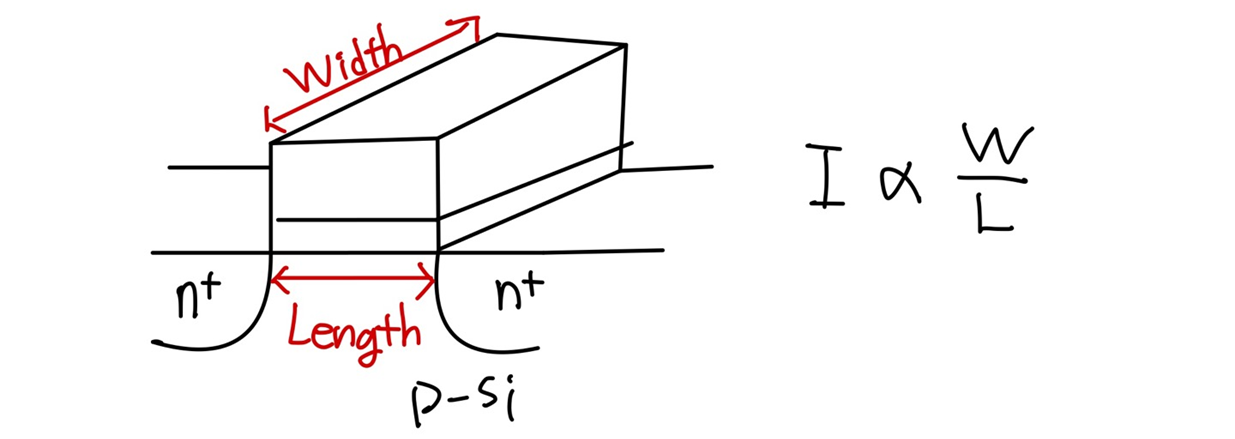

전류와 length와 width 관계

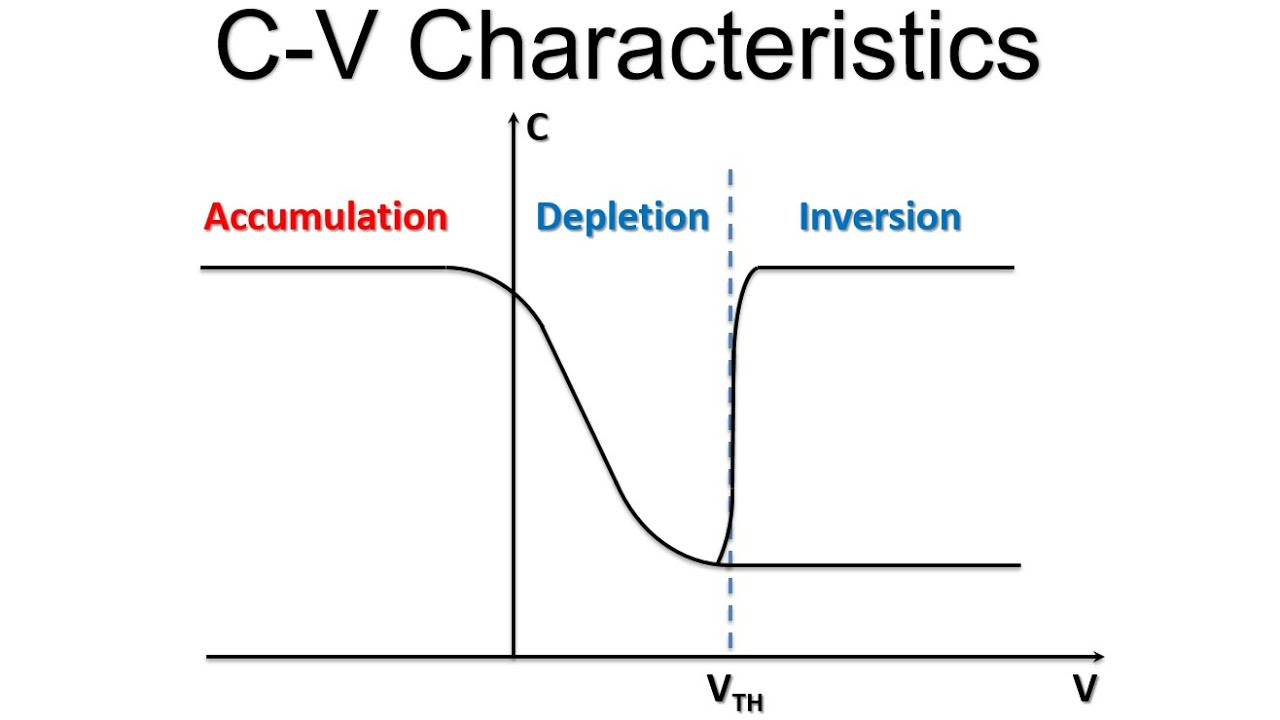

Capacitance

Acc와 Inv에서 d가 같으므로 같은 C값을 가지고 Dep에서 d가 커지므로 낮은 C를 가진다.

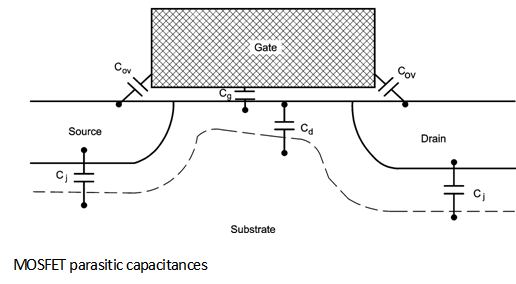

Parasitic Capacitor in Mosfet

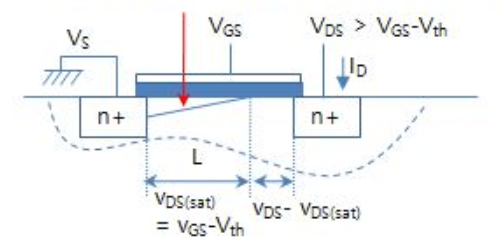

Channel Length Modulation

linear 영역에서 Vds를 키우면 pinch-off가 발생하게 되고 이때부터 Vds를 증가시키더라도 전류는 증가하지 않는다. 그러나 Vds가 증가할수록 채널의 길이가 짧아지고 이는 결국 드레인 전류의 상승을 불러오게된다.

Body Effect

Mosfet은 gate, source, drain, body 4단자 소자다. gate와 body 사이의 전압차이로 수직전계가 발생하고 일정 값(Vth) 이상이 되면 채널이 형성된다. 그리고 일반적으로 source와 body는 gnd로 연결되있다. 더 낮은 Vg에서 mosfet을 on시키기 위한 방법으로는 Body전압을 음수로 만들어 body와 연결된 source도 음수가 된다. (Vgs = Vg - Vs) 이는 결국 더 낮은 gate voltage에서 동작할 수 있게 만든다.

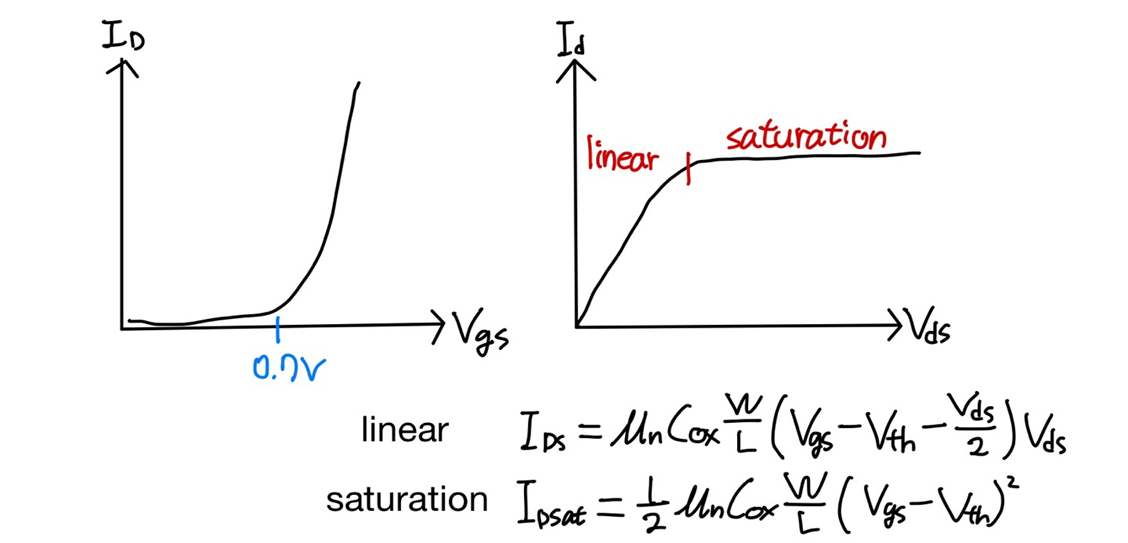

V-I 특성곡선 & 전류공식 (linear / Saturation)

- Vgs < Vth : Off

- Vgs > Vth , Vds < Vgs-Vth : linear

- Vgs > Vth , Vds > Vgs-Vth : saturation

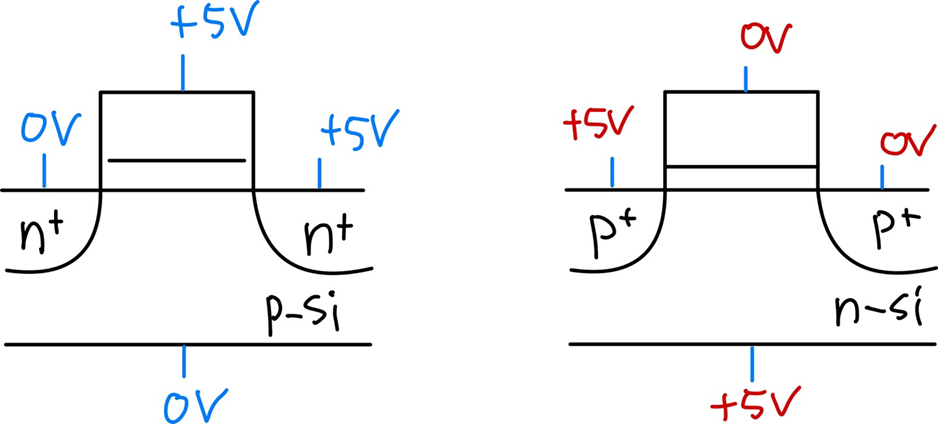

nmos는 source와 body를 0V로 만들고, pmos는 source와 body를 Vdd로 만든다.

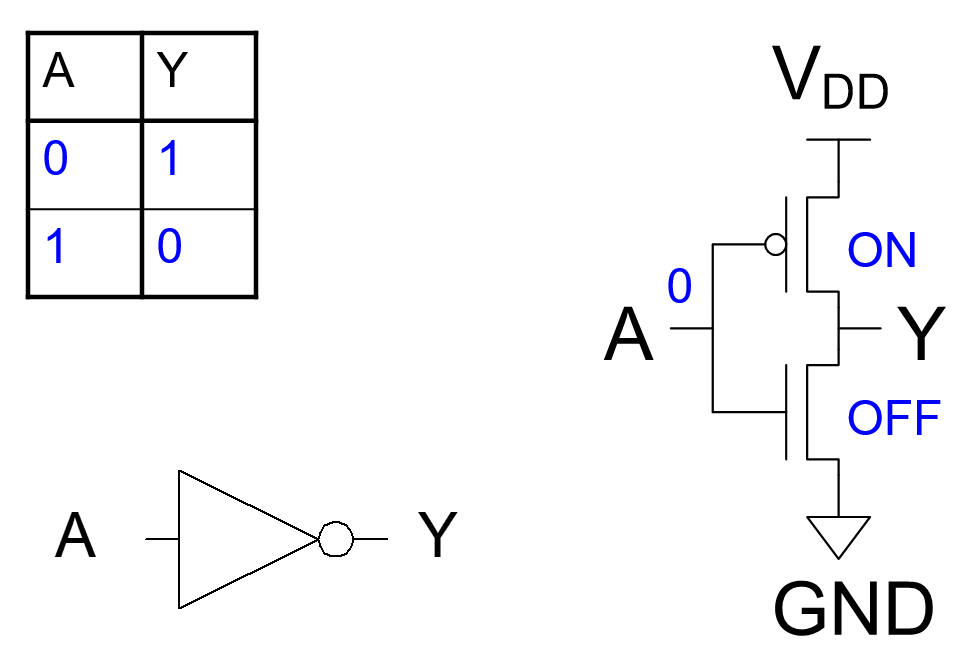

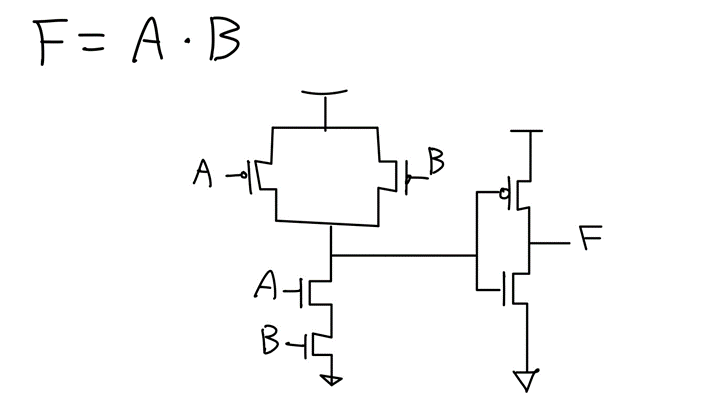

Inverter

pmos가 Vdd에 가깝고 nmos가 Gnd에 가까운 이유는 pmos의 body가 Vdd로 연결되고 nmos의 body는 Gnd에 연결되기 때문이다.

또다른 이유로는 Inverter의 완전한 Pull-up과 Pull-down을 만들기 때문이다. 만약 nmos가 Vdd에 가깝다면 nmos가 on이 되었을 때 source가 완전히 Vdd로 Pull-up되지 않고 Vth만큼 감소되어 출력된다.

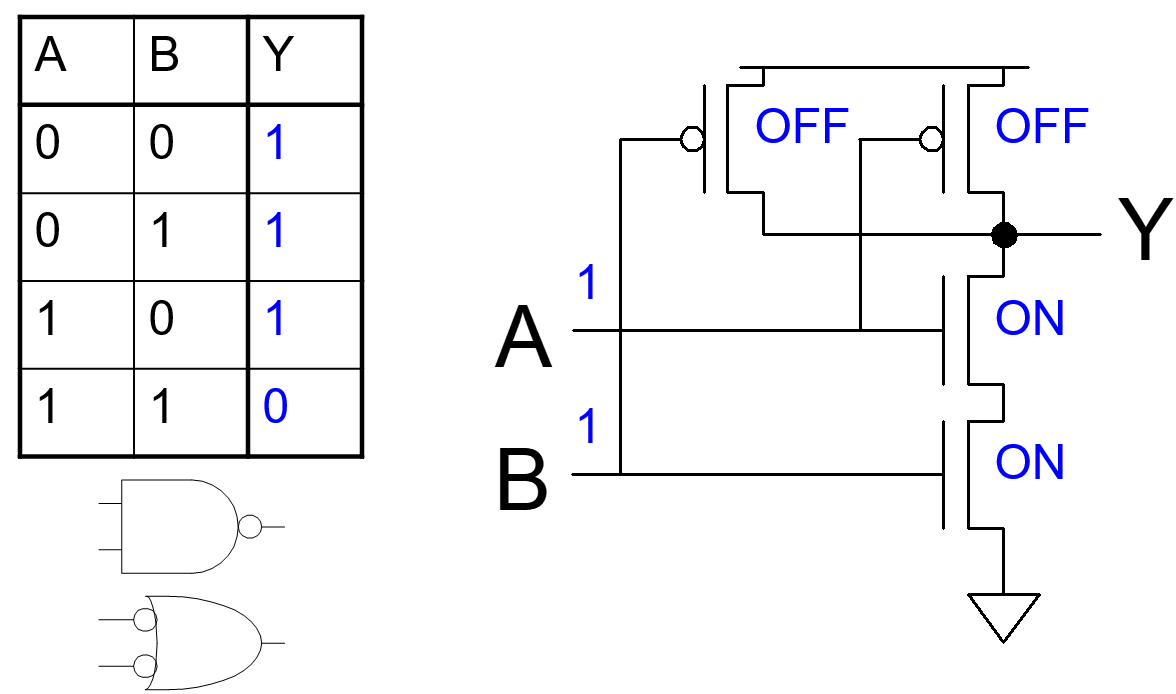

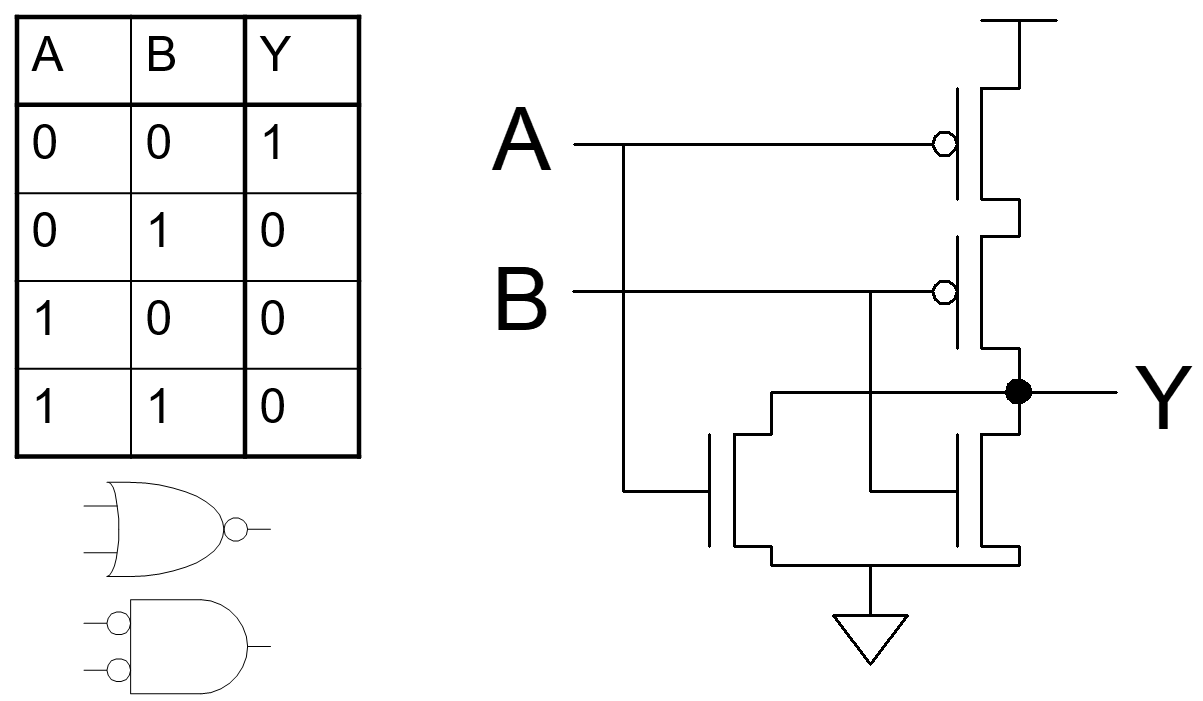

NAND

NOR

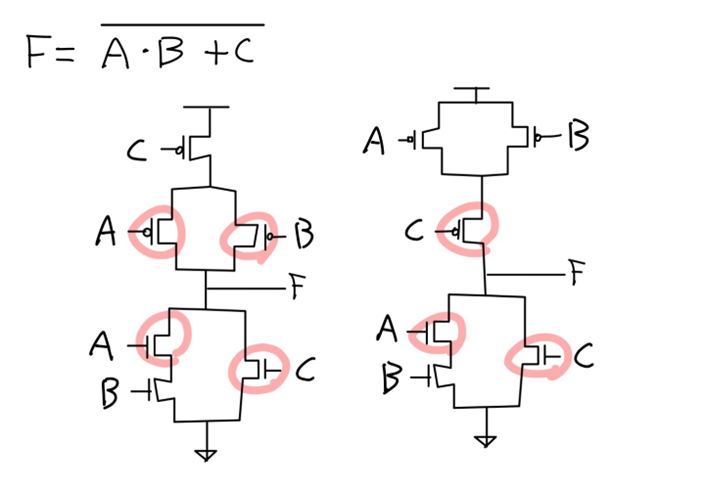

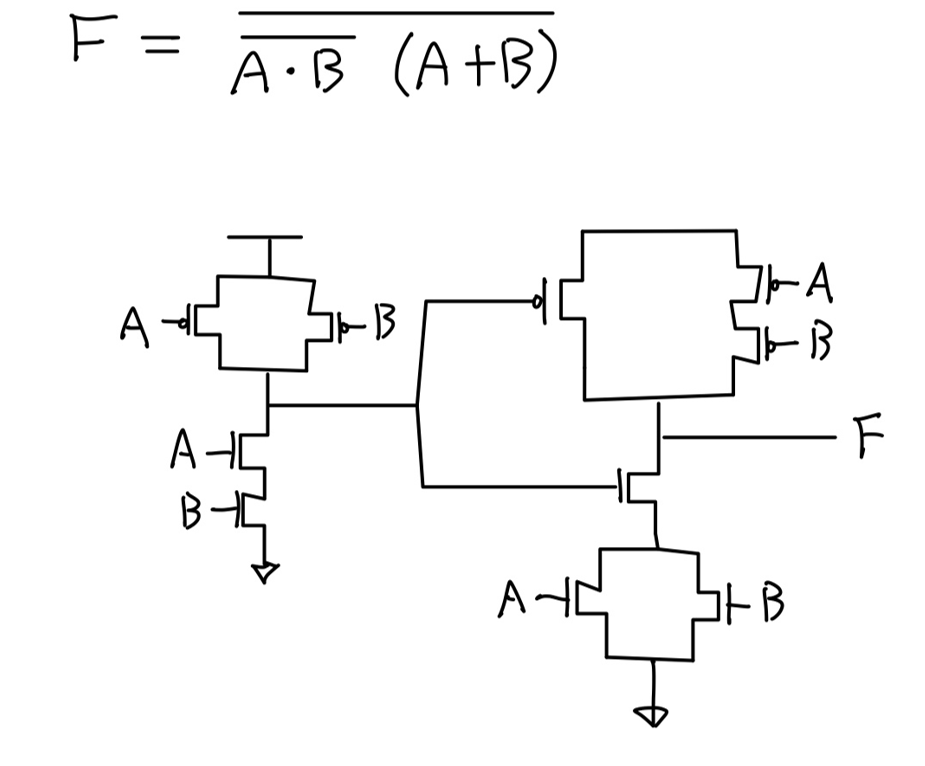

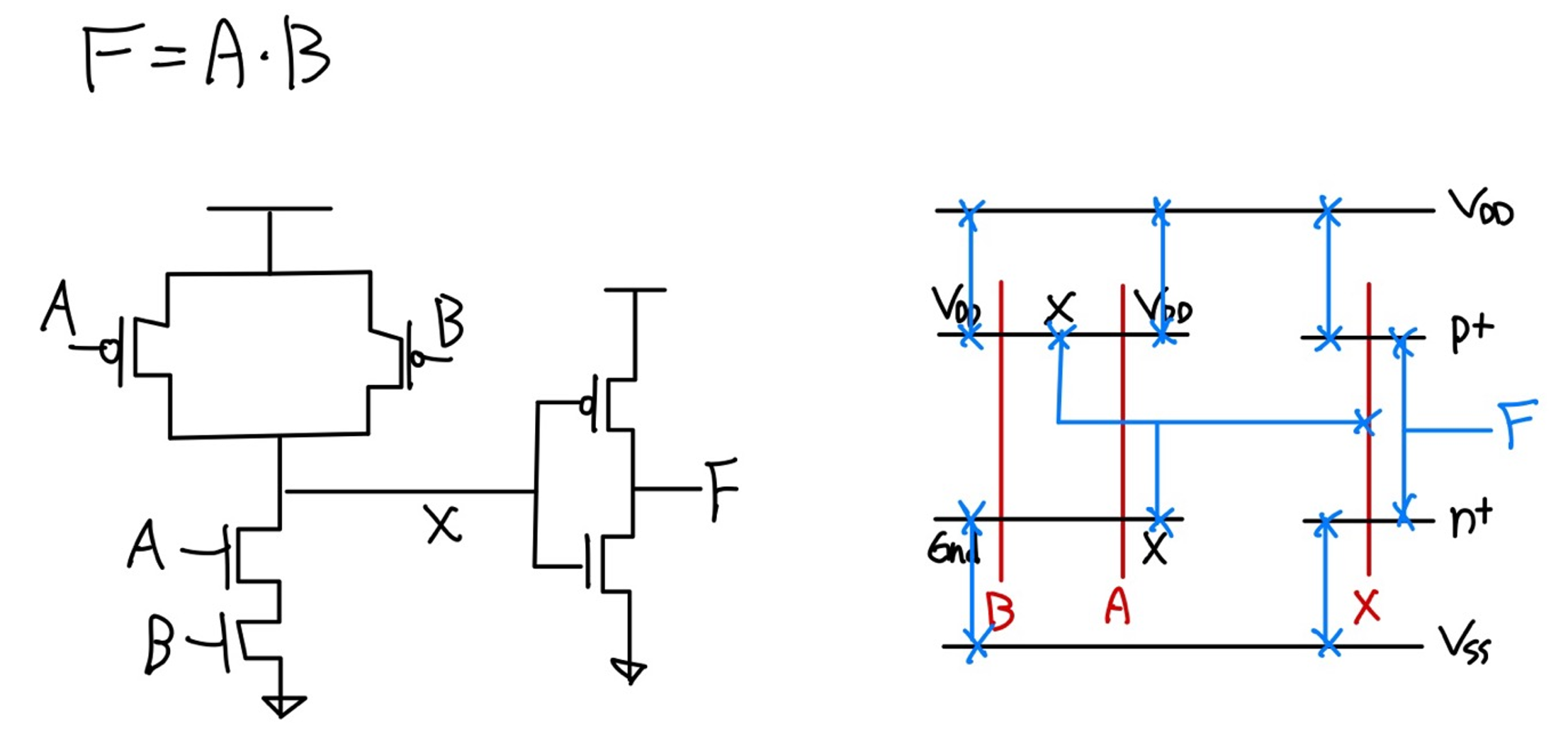

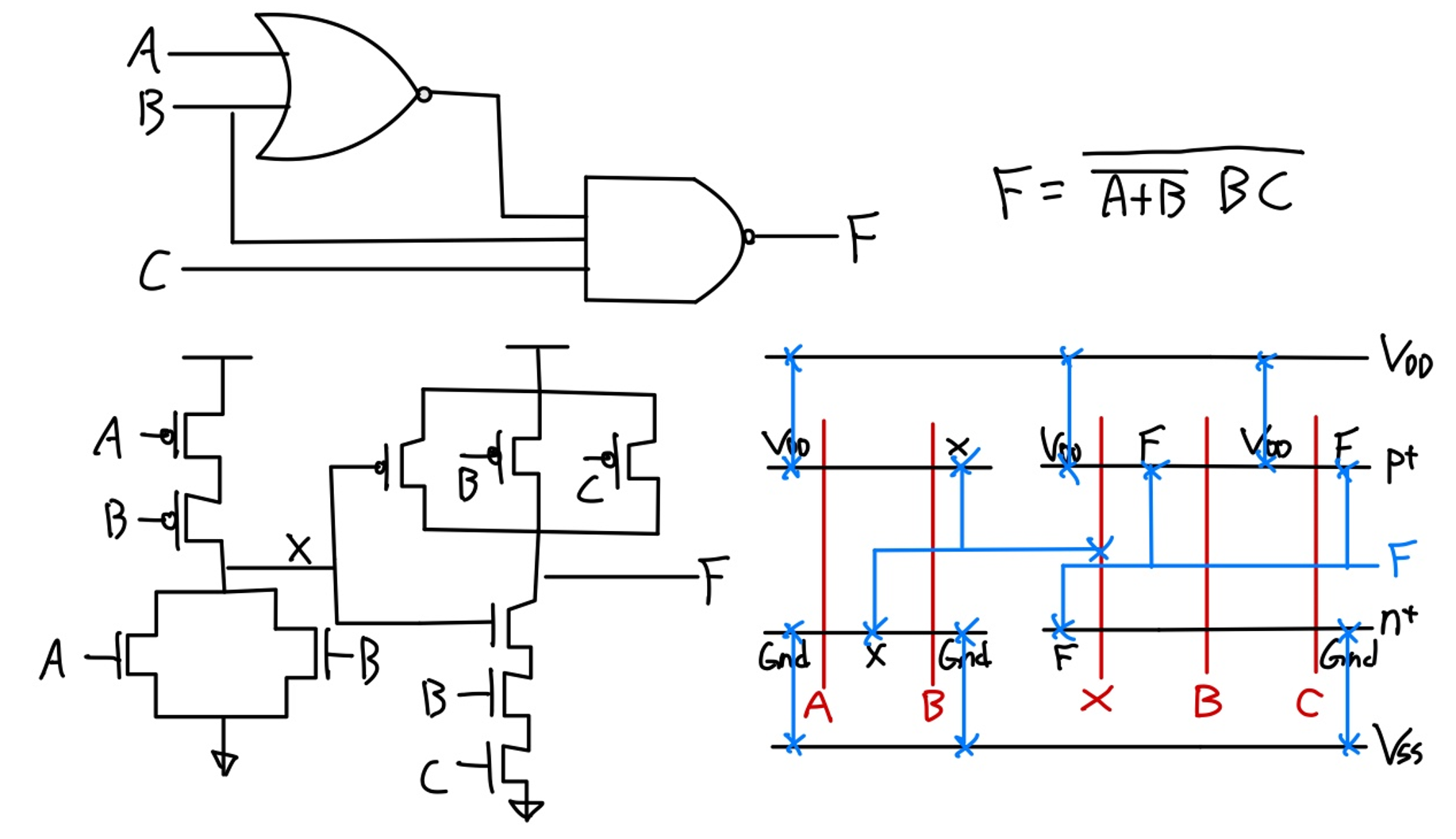

CMOS Schematic

곱연산은 nmos기준 직렬로 연결하고 덧셈연산은 nmos기준 병렬로 연결한다. pmos는 반대로 그려주면 된다.

tr에는 다양한 C가 존재하고, C가 클수록 voltage change가 어렵기 때문에 출력에 달린 tr 개수에 따라 성능이 달라진다.

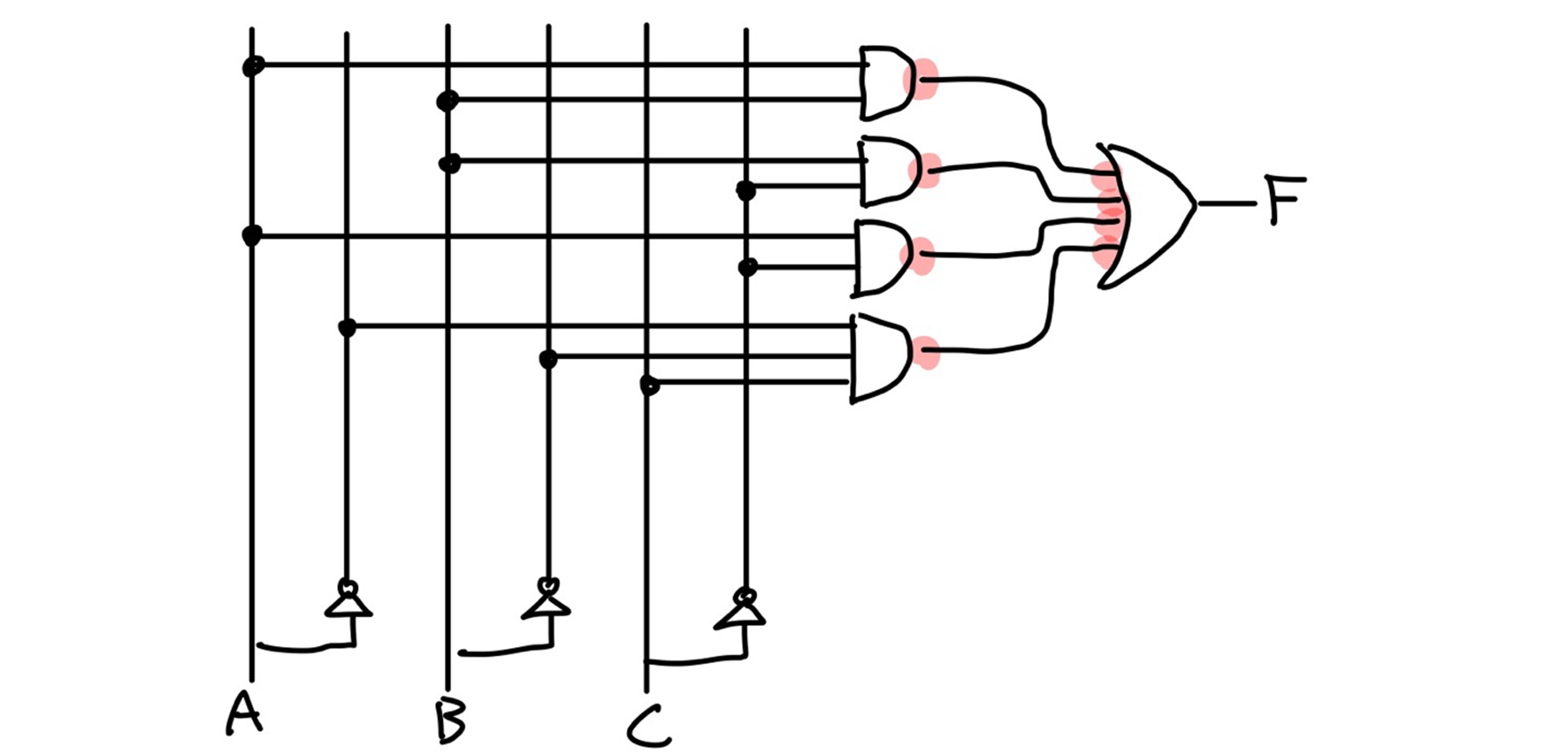

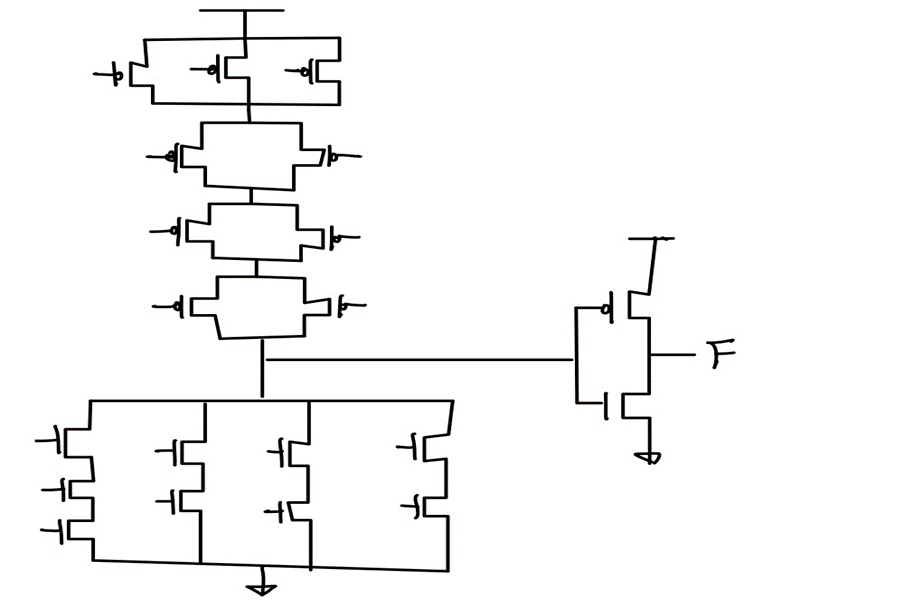

Truth Table로부터 F와 Logic gate 그리고 schematic을 나타냈다.

- Logic gate에서는 2NAND 3개, 3NAND 1개, 4NAND 1개, NOT 3개가 있으므로

4x3+6x1+8x1+2x3 = 32개의 tr - Schematic에서는 26개의 tr이 있다.

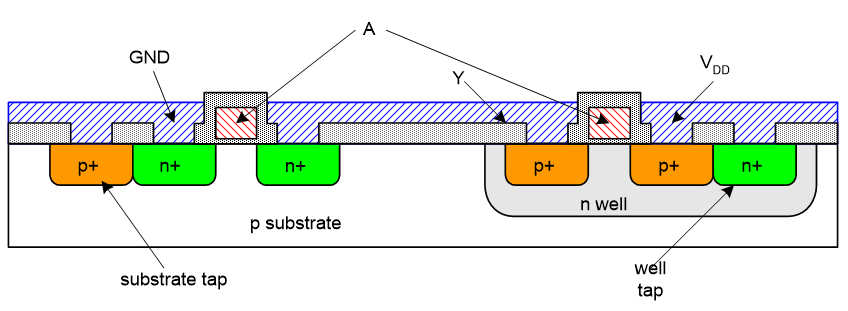

Cross Section/Mask Set

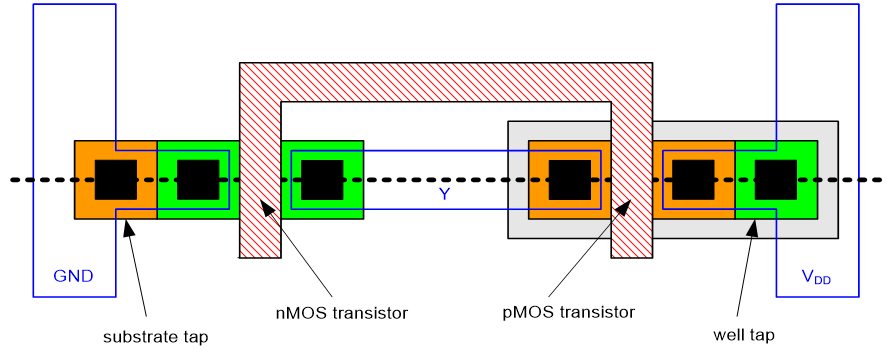

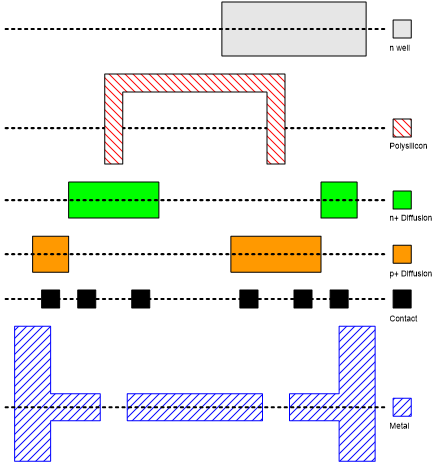

아래 그림 2개는 single well Inverter의 Cross Section과 Mask Set이다.

nmos의 p+와 pmos의 n+는 body를 metal에 연결해준 것이다.

그러나 electron과 hole은 모빌리티가 서로 다르므로 다음과 같이 length와 width를 똑같이 그리면 안된다.

Inverter를 만들기 위해 총 6개의 mask가 필요합니다.

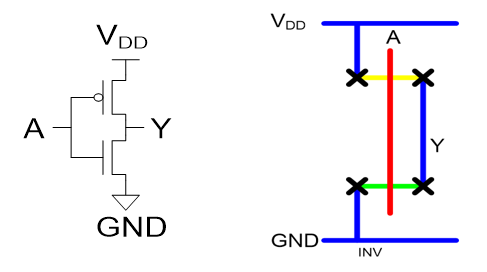

Stick Diagram

schematic을 바로 mask set으로 만들기에 회로가 복잡해질수록 어렵다. 따라서 실제로 Layout을 하기 전에 막대 형태로 대략적인 모습을 그려보는 stick diagram을 그려 조금 더 쉽게 Layout 형태를 구상할 수 있다. stick diagram은 그리는 사람에 따라 회로 모양에 따라 여러가지 형태가 나올 수 있다.

우선 stick diagram을 그리기 위해 schematic에서 path를 정해야 한다. path를 정하는 방법은 다음과 같다.

- nmos와 pmos block을 모두 만족해야 한다.

- 각각의 block에서 tr을 1번씩만 경유해야 한다.

Inverter의 stick diagram이다.

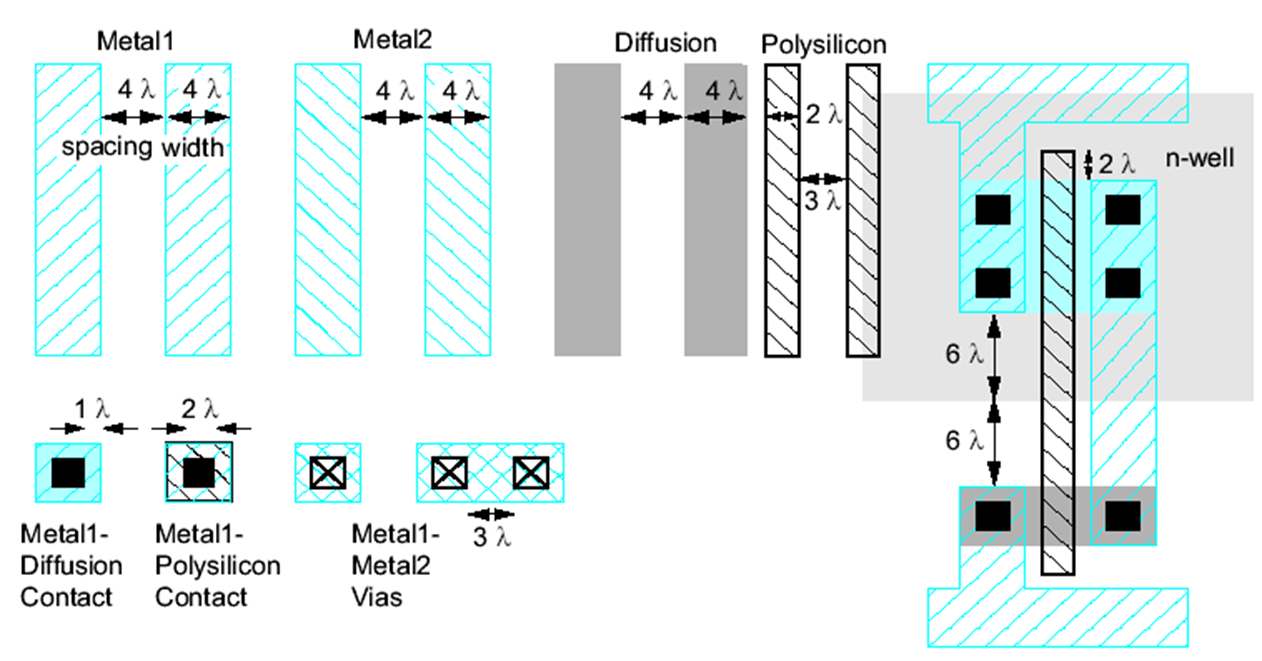

Design Rules

Design Rule은 metal과 metal 사이, metal의 두께, contact과 metal의 간격, contact과 contact사이의 거리 등 각 공정 속에 굉장히 많은 design rule이 있다. 설계 엔지니어는 각 공정의 Design Rule을 바탕으로 설계를 해야한다.