Virtuoso

Standard Cell

Library를 생성해 Standard Cell을 만드는 과정입니다.

Inverter

Inverter Simulation

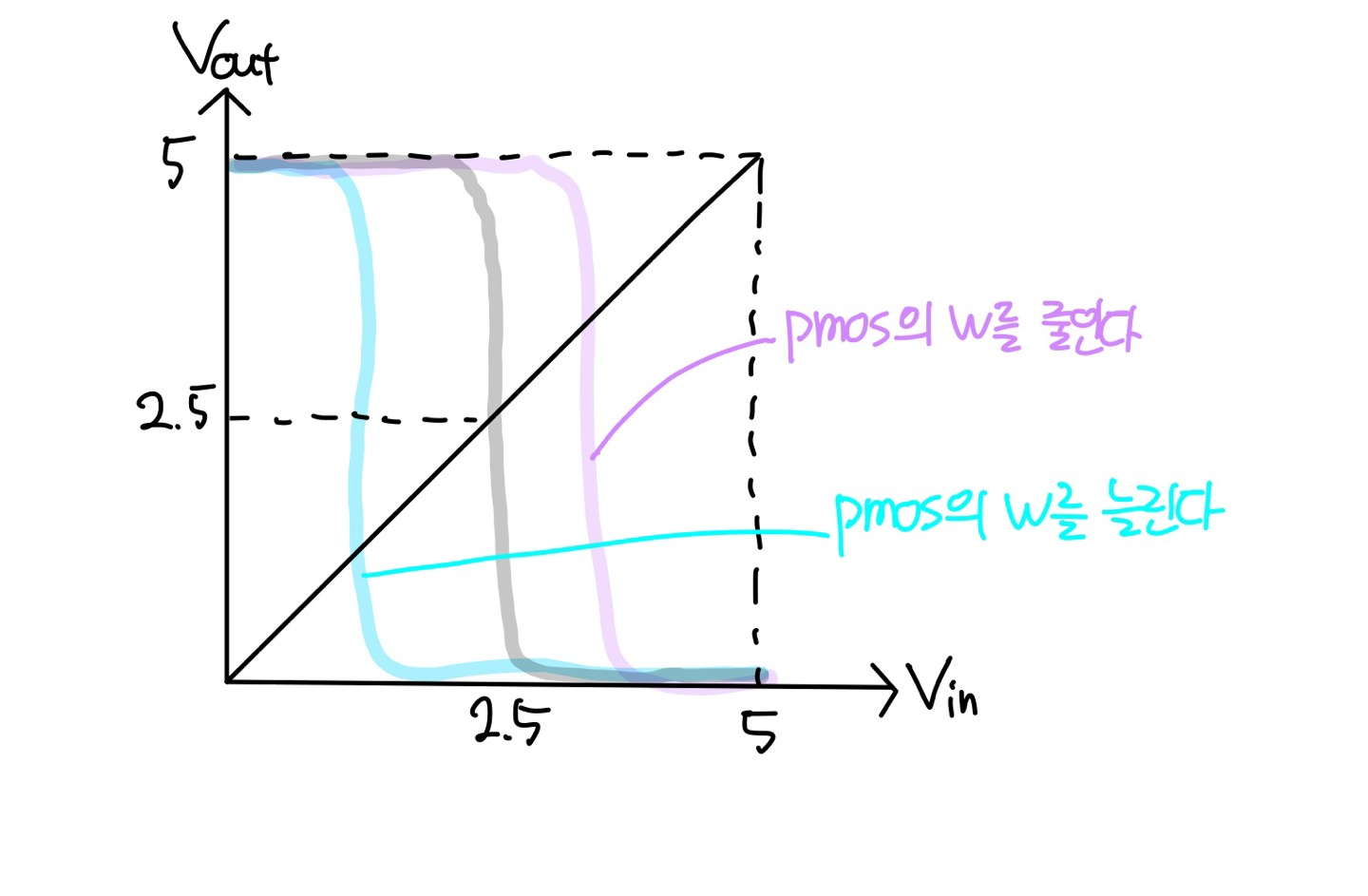

전류는 W와 L을 조절하여 설정할 수 있다. pmos의 영역이 더 작은 경우 W를 늘려 조절할 수 있다. 그리고 nmos의 영역이 더 작은 경우 pmos의 W를 줄여 조절할 수 있다.

pmos의 W를 주로 조절하는 이유는 보통 공정상 가장 작은 단위가 L을 결정하여 줄일 수 없고, nmos의 W를 fix했을 때 pmos의 W를 조절해서 Inverter를 만들 수 있다.

실습에서는 nmos의 width를 1u로 고정하고 pmos의 width를 sweep해가며 찾아가야 한다.

처음 1u부터 10u까지 1u씩 sweep하고, 이 과정을 반복하여 소수점 두째자리까지 width를 찾는다.

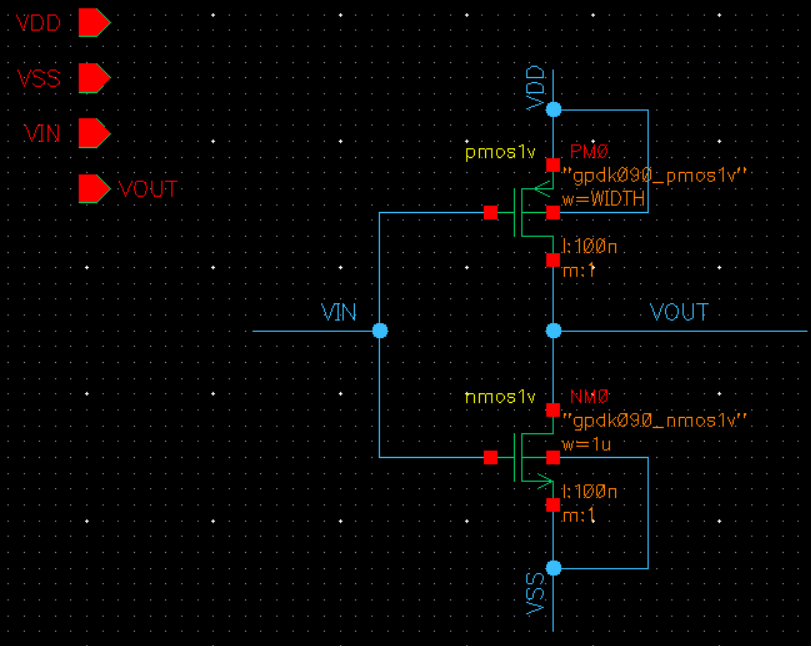

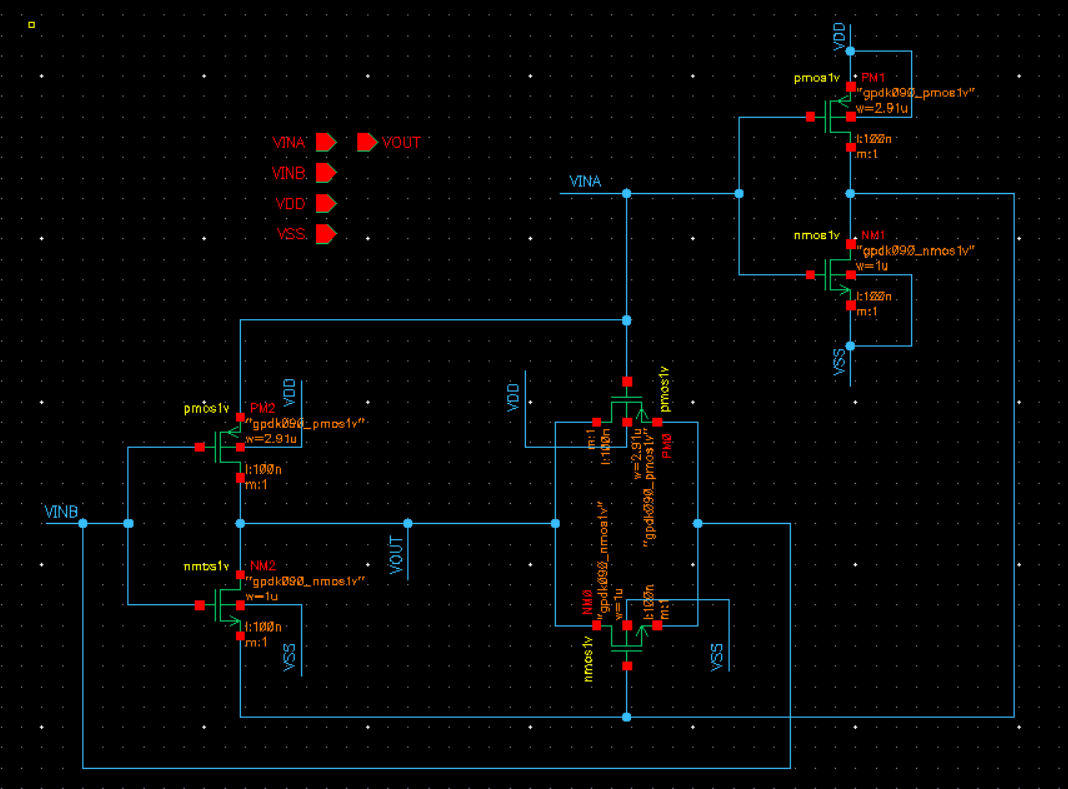

Schematic

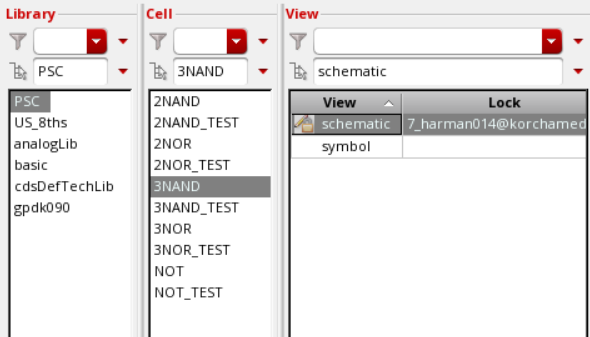

Library Manager에서 File -> New -> Cellview를 통해 schematic을 만들어준다.

Option -> Display -> Grid를 설정

단축키

i : instance

w : wire

l : lable

p : pin

q : 속성

i를 눌러 instance에 들어가고 gpdk090 library에서 nmos1v와 pmos1v를 각각 가져온다. wire를 이용해 배선을 연결하고(body도 연결해야함), label로 배선의 이름을 표시한다. VDD, VSS, VIN은 INPUT Pin으로 설정하고, VOUT은 OUTPUT Pin으로 설정한다.

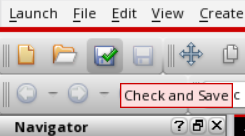

완료되면 Check and Save로 error를 검사한다.

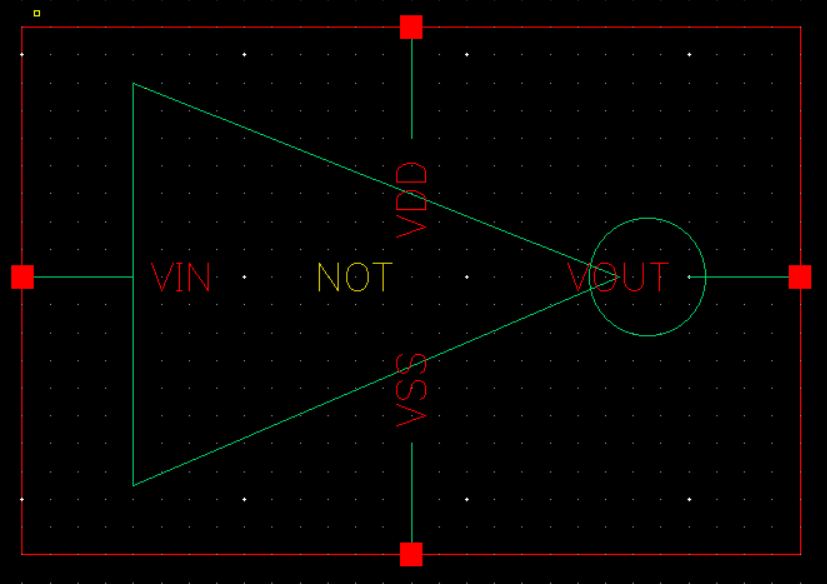

Symbol

schematic에서 Create -> Cellview -> From cellview로 접근해 symbol을 만든다.

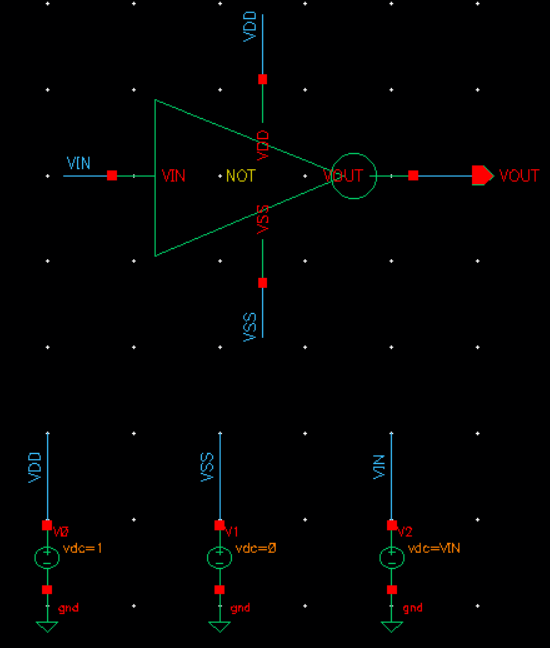

Test

Library Manager에서 File -> New -> Cellview를 통해 test schematic을 만들어준다.

instance에서 나의 library의 전에 만든 NOT을 가져오고, analog library에서 전원을 위의 그림과 같이 만들어준다. OUTPUT Pin을 제외한 모든 Pin들은 전원을 연결해준다.

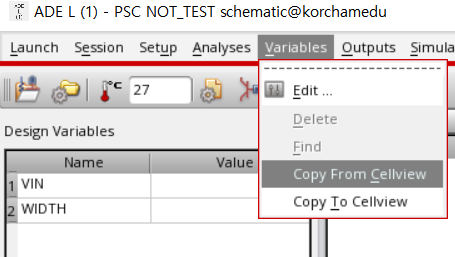

Launch -> ADE L에 들어간다.

위의 그림과 같이 Copy From Cellview로 변수들을 가져온다.(VIN, WIDTH)

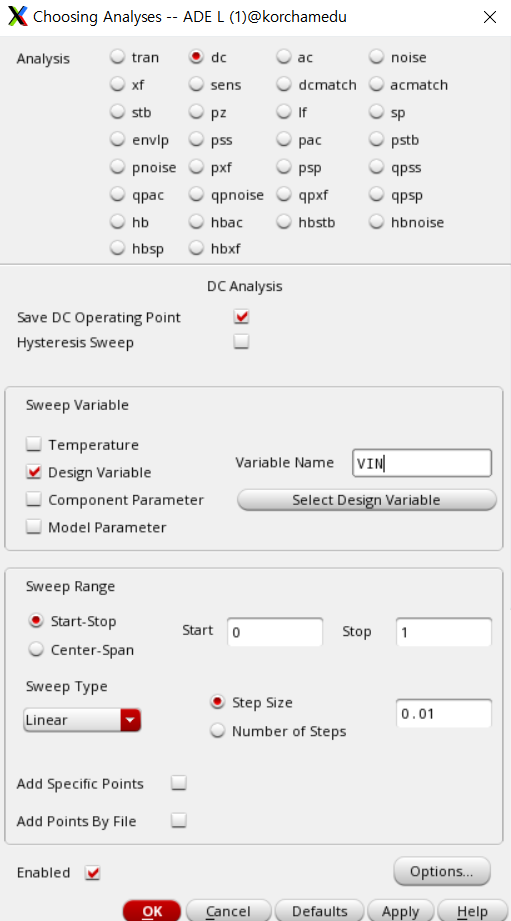

이후 Analyses -> Choose

위와 같이 VIN을 설정한다.

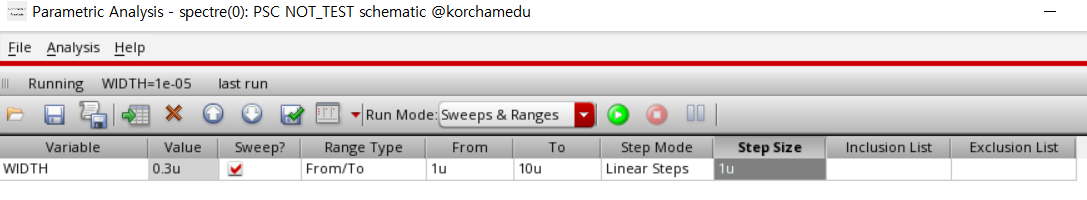

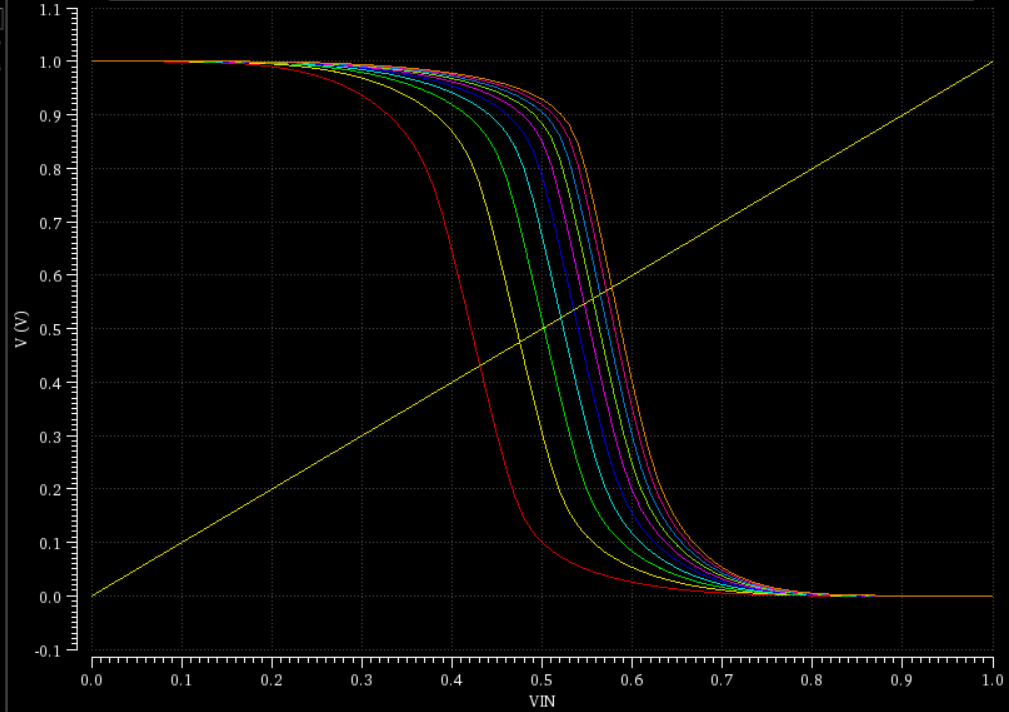

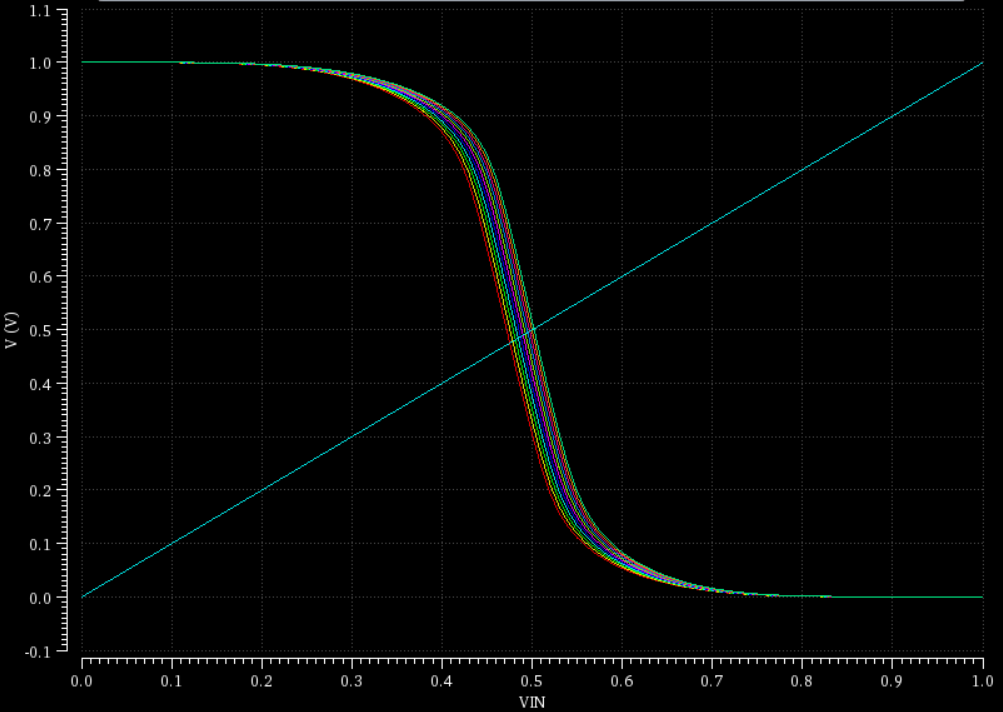

이후 Tool -> Parametric Analysis에서 WIDTH에 따른 Plot을 확인한다.

Result -> Direct Plot

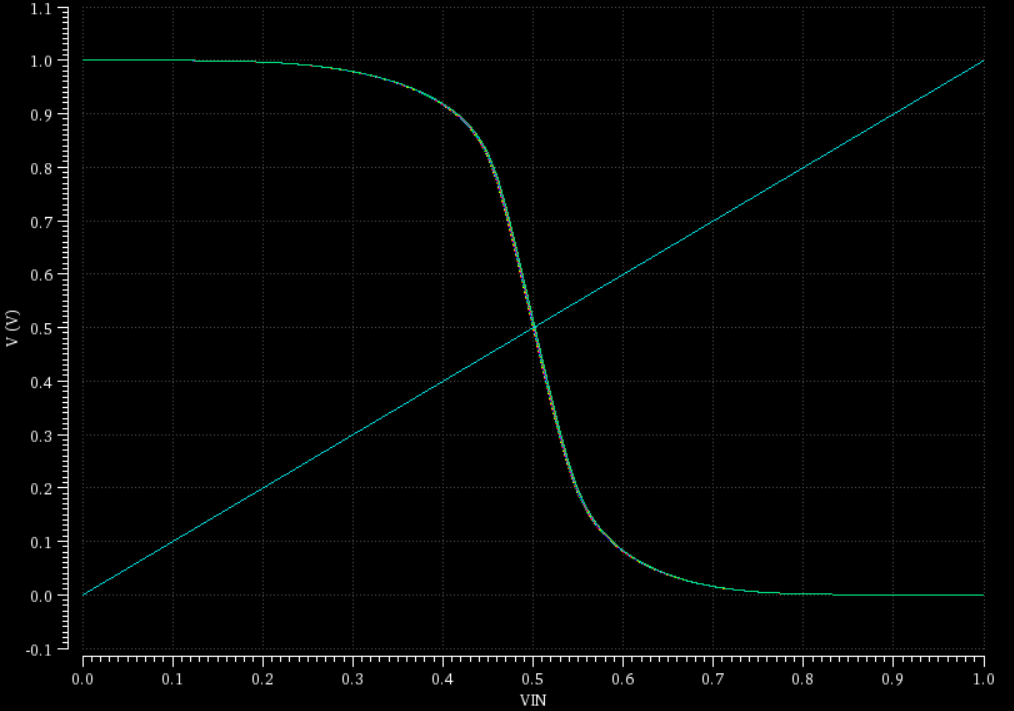

1u부터 10u까지 1u단위로 WIDHT를 변화시킨 것이다.

2u부터 3u까지 0.1u단위로 WIDHT를 변화시킨 것이다.

2.9u부터 3u까지 0.01u단위로 WIDHT를 변화시킨 것이다.

최종 simulation결과 WIDTH는 2.91u이다.

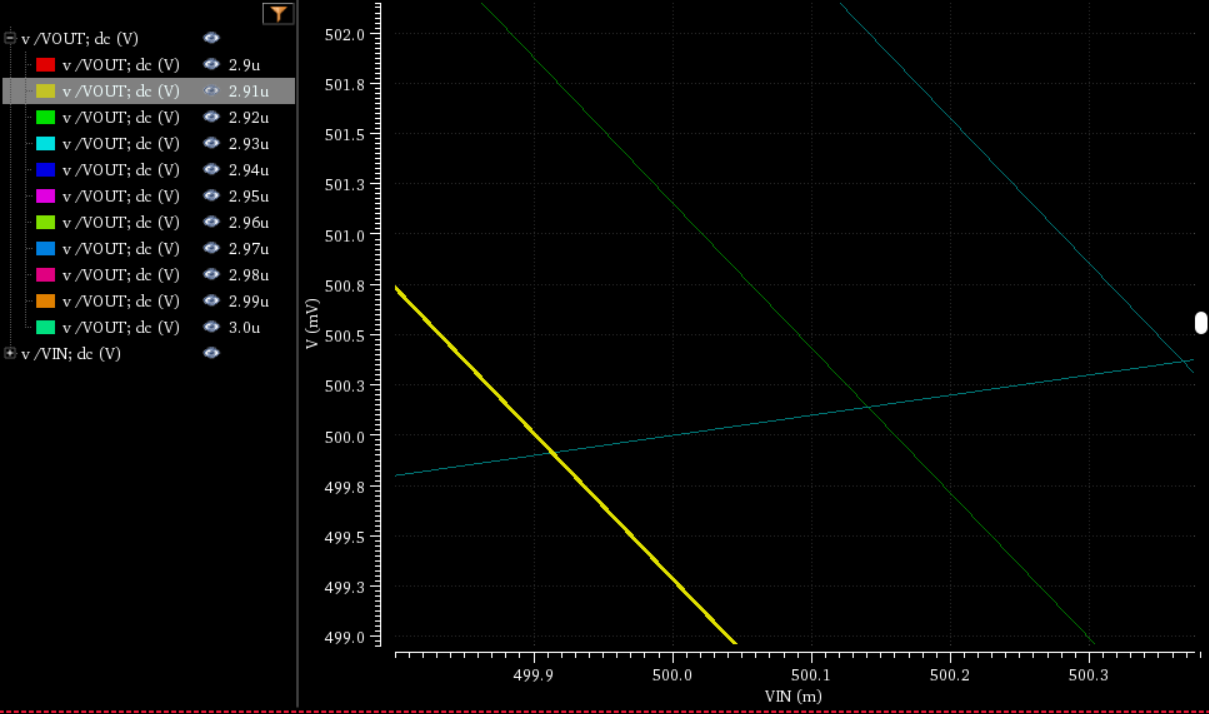

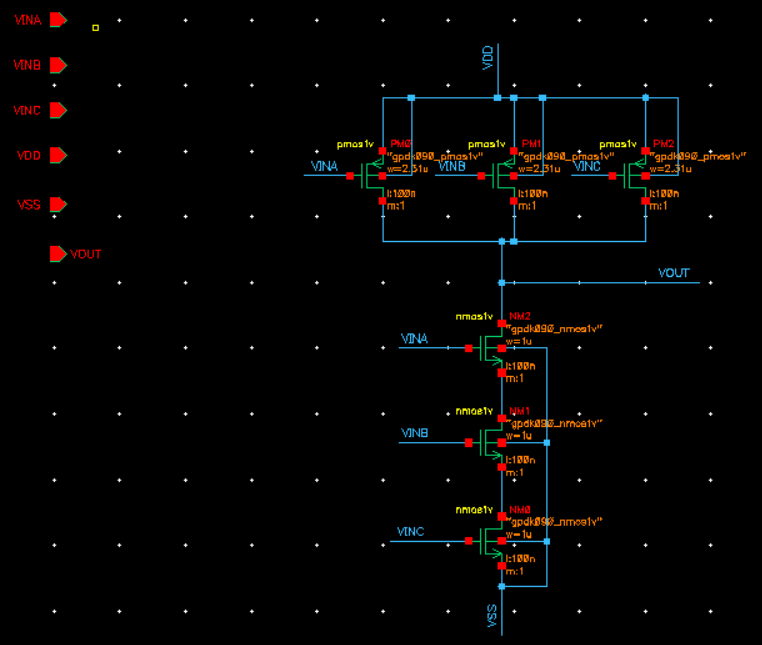

2NAND

| A | B | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

2NAND의 진리표를 보았을 때 아래 2칸과 같이 A를 1로 fix하고 B가 0에서 1로 변할 때 F가 1에서 0을로 변화하는 것으로 simulation하면 된다.

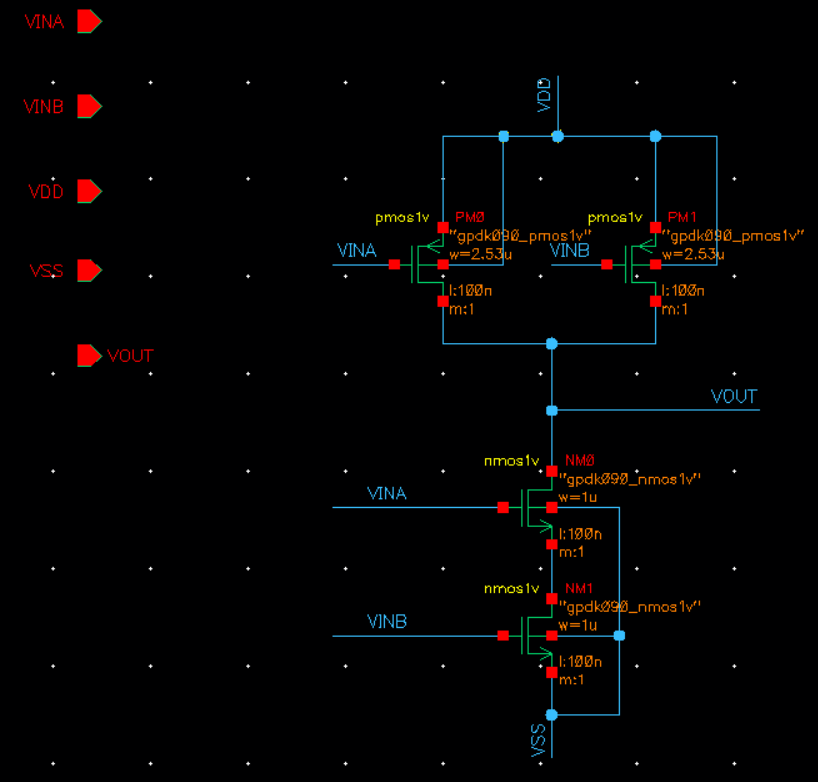

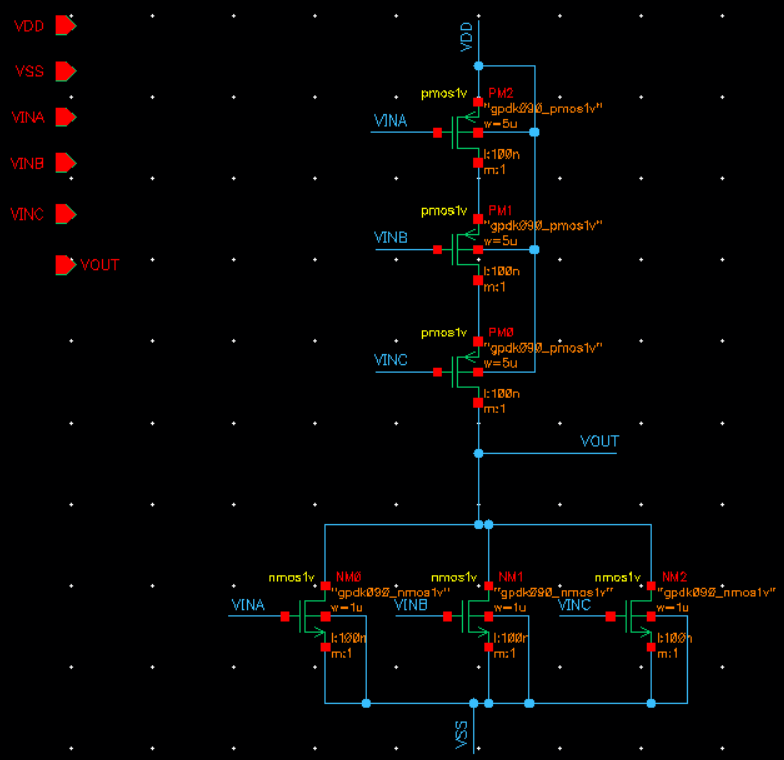

2NOR

| A | B | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

2NOR의 진리표를 보았을 때 위의 2칸과 같이 A를 0로 fix하고 B가 0에서 1로 변할 때 F가 1에서 0을로 변화하는 것으로 simulation하면 된다.

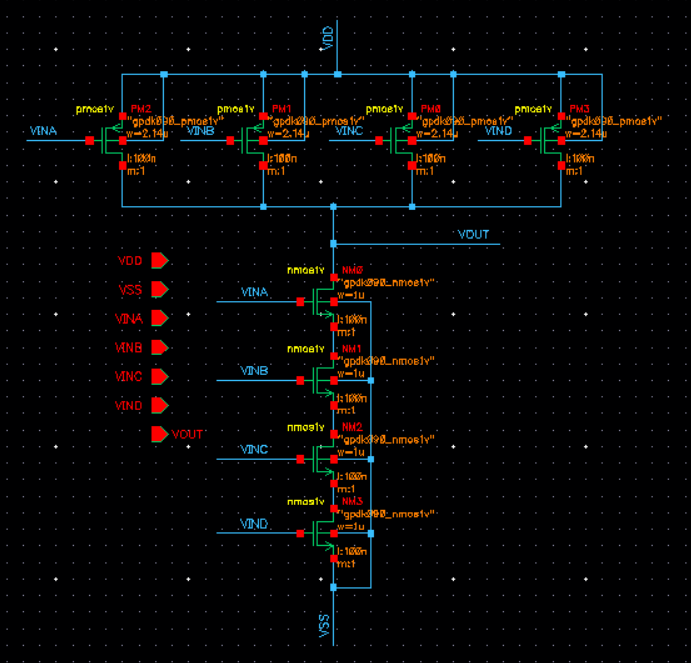

3NAND

3NOR

4NAND

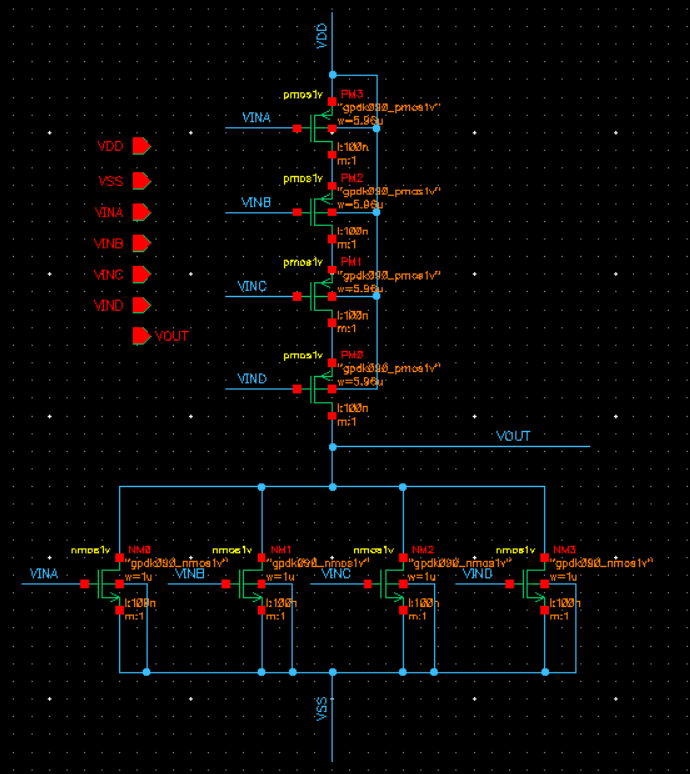

4NOR

XOR

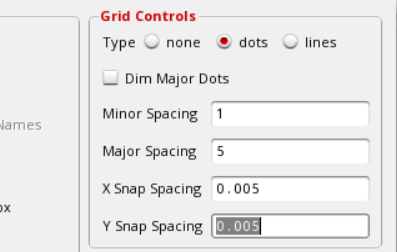

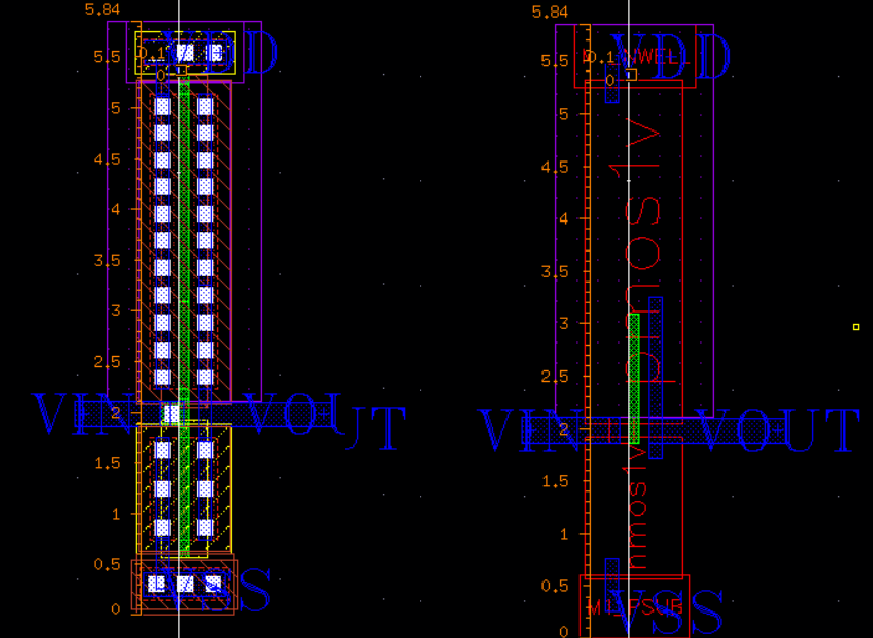

Layout

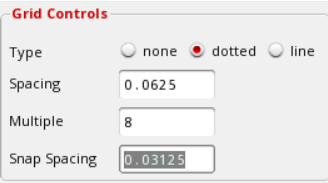

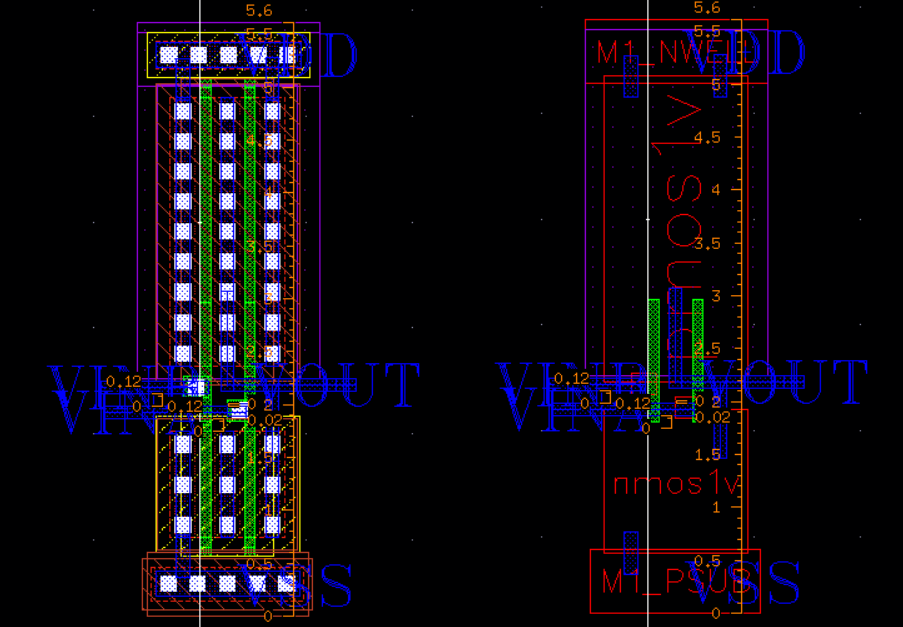

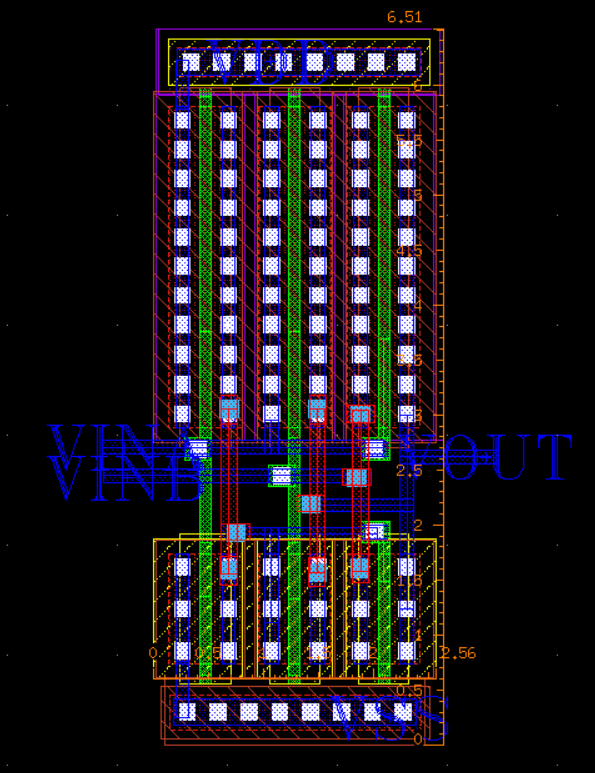

Option -> Display에서 Grid를 위와 같이 조정한다.

만약 Grid를 맞추지 않으면 Off-Grid error가 발생게 된다.

-

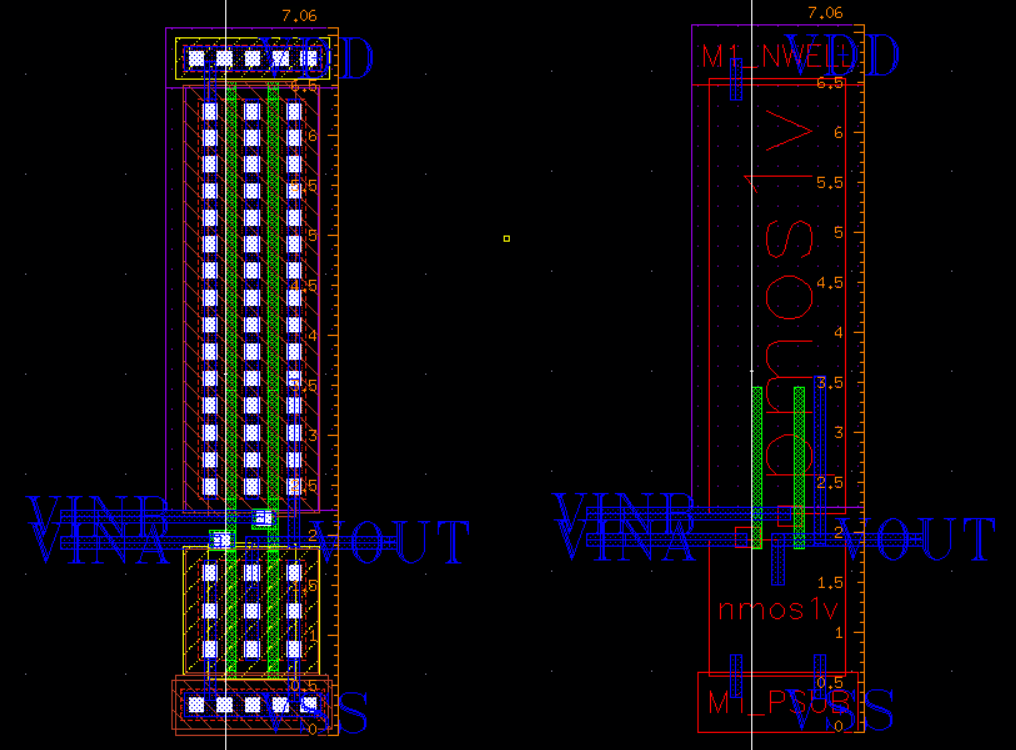

INVERTER

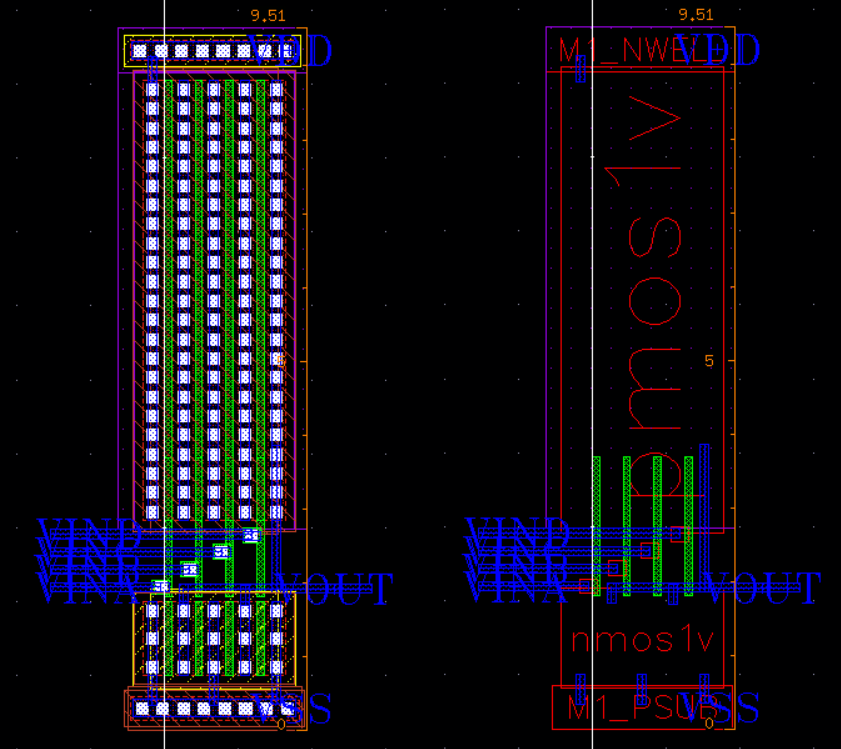

nmos1v와 pmos1v를 instance에서 불러온다. Inverter는

-

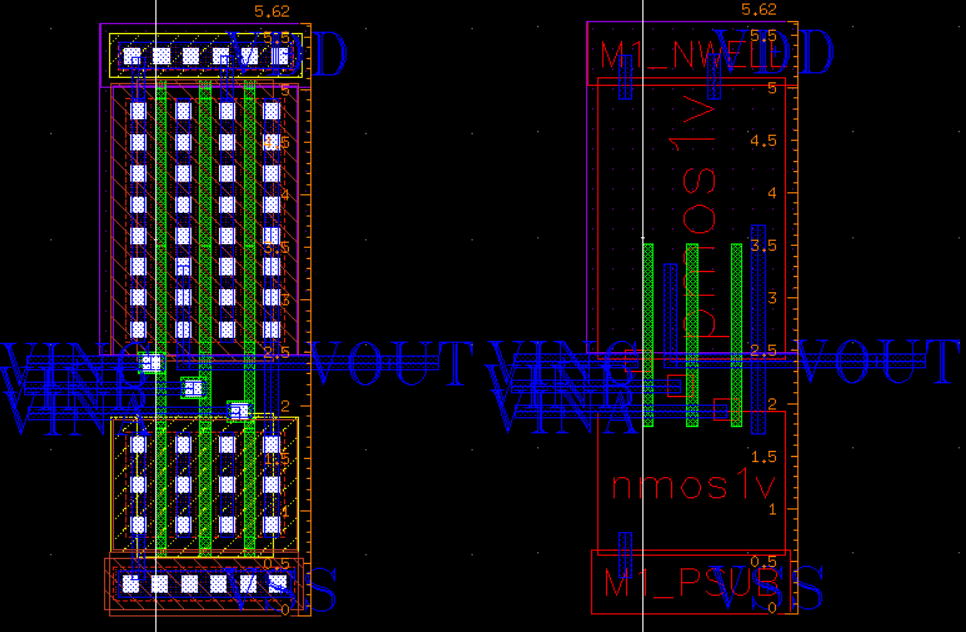

2NAND

-

2NOR

-

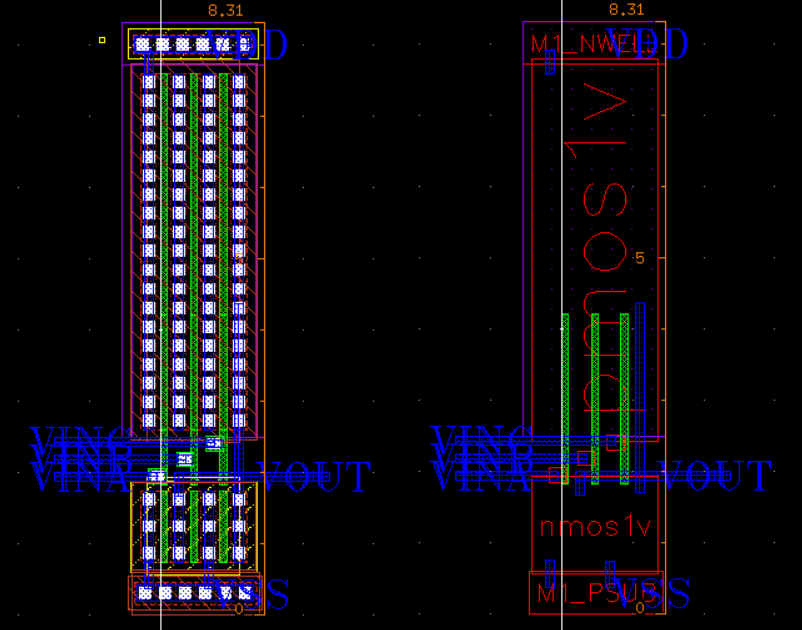

3NAND

-

3NOR

-

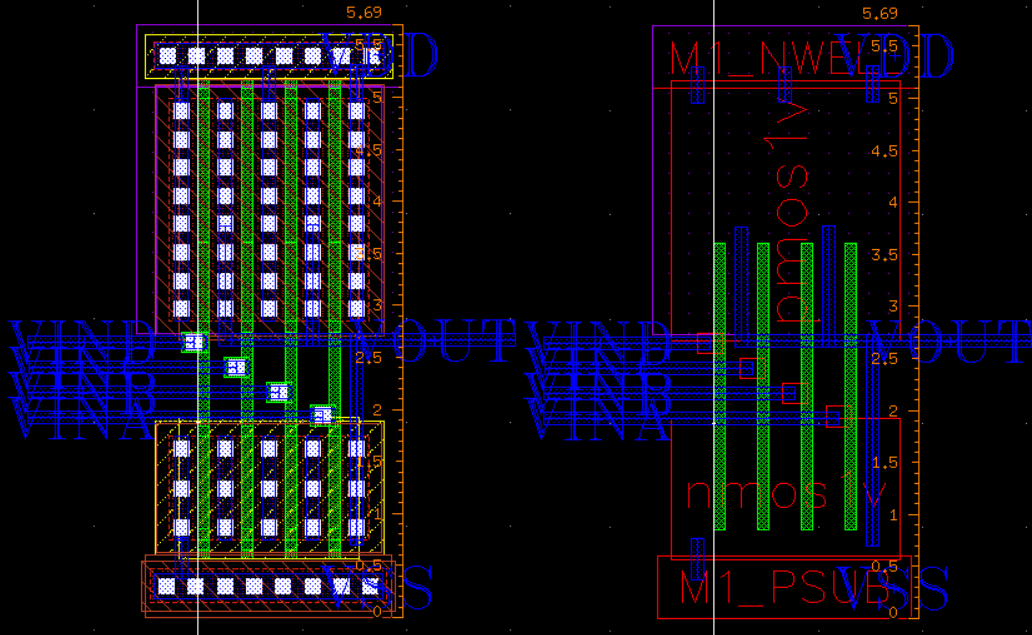

4NAND

-

4NOR

-

XOR

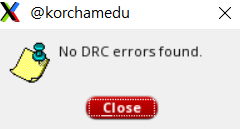

DRC

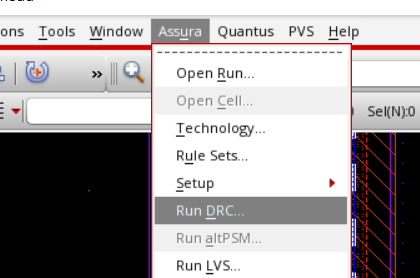

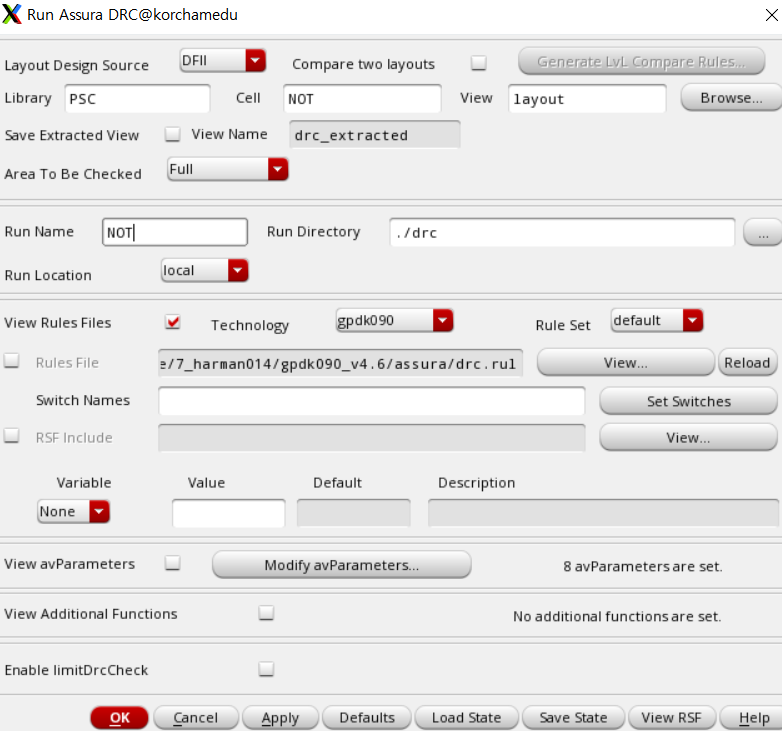

DRC(Design Rule Check)작업은 layout이 design rule에 맞게 그려졌는지를 확인하는 검증단계이다.

Assura -> Run DRC를 실행한다.

Run Name을 정하고 Run Directory는 ./drc이다.

Rule file은 gpdk090으로 설정하고 DRC를 진행한다.

DRC 검증 완료

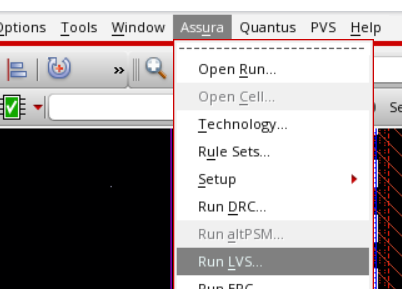

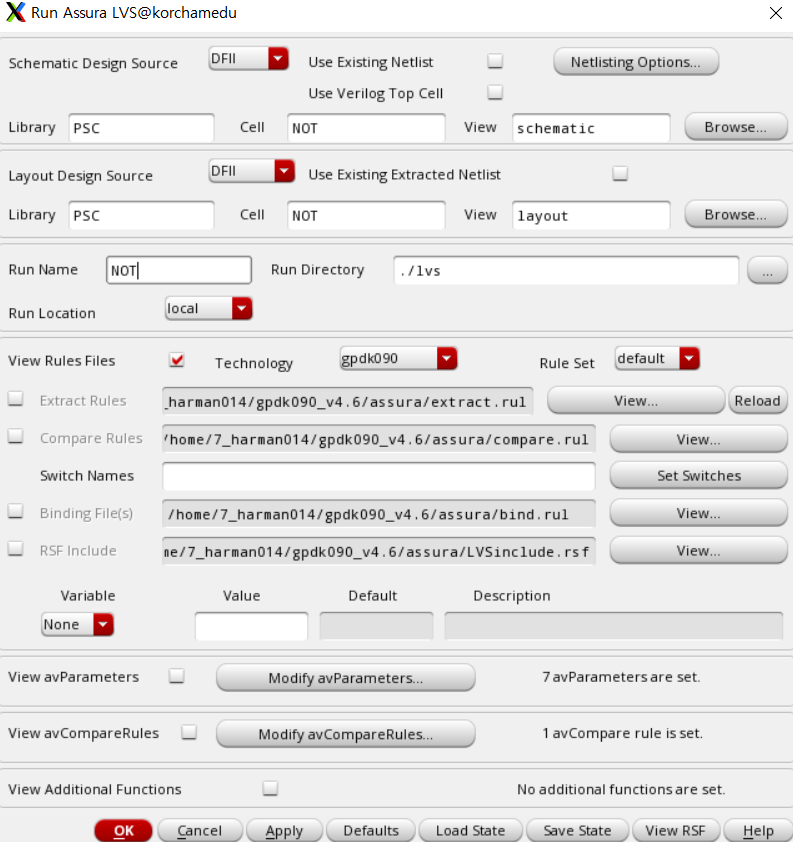

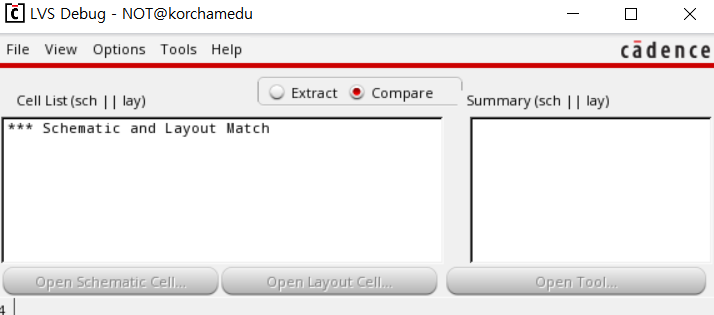

LVS

LVS(Layout versus Schematic)작업은 layout이 schematic과 match가 되는지 확인하는 검증작업이다.

Assura -> Run LVS를 실행한다.

Schematic source를 확인한다.

Run Name을 정하고 Run Directory는 ./lvs이다.

Rule file은 gpdk090으로 설정하고 LVS를 진행한다.

LVS 검증 완료