RISC-V의 RV32I Instruction Set을 구현하고, GPIO, UART등의 Peripheral을 구성하여 설계한 하드웨어에 Software Program을 동작시키는 프로젝트다.

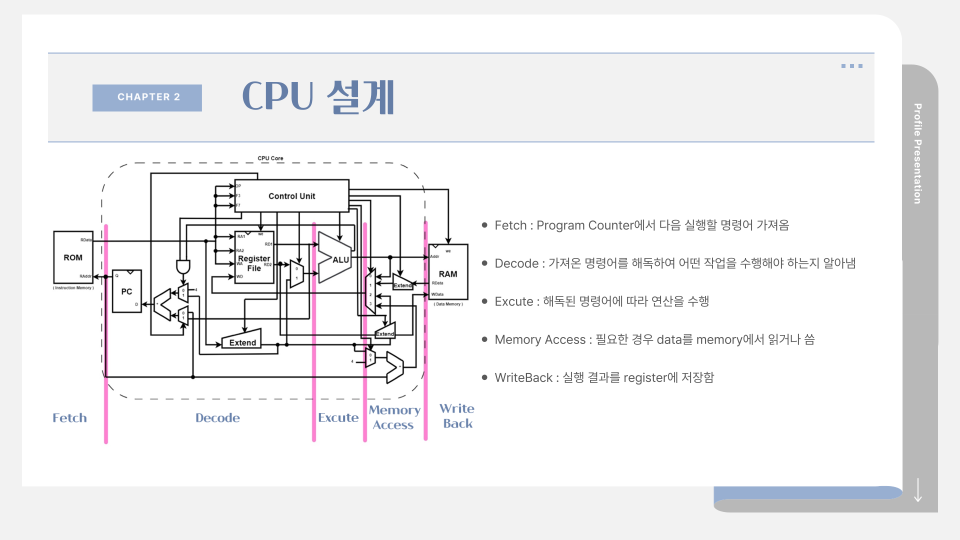

이번 프로젝트의 CPU는 Single Cycle로 동작하지만, Pipeline으로 만든다면 위와 같이 나누고, register를 배치하여 Multi Cycle로 동작시킬 수 있다.

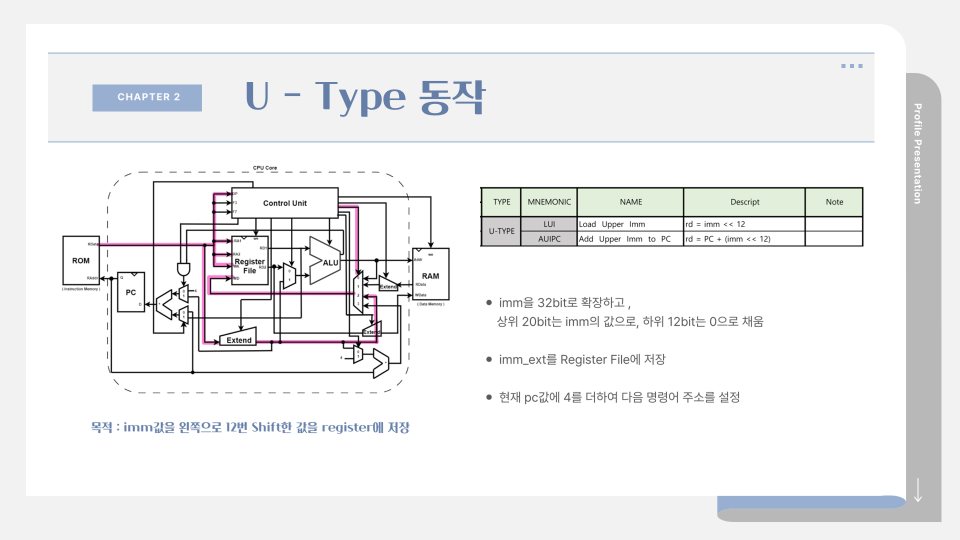

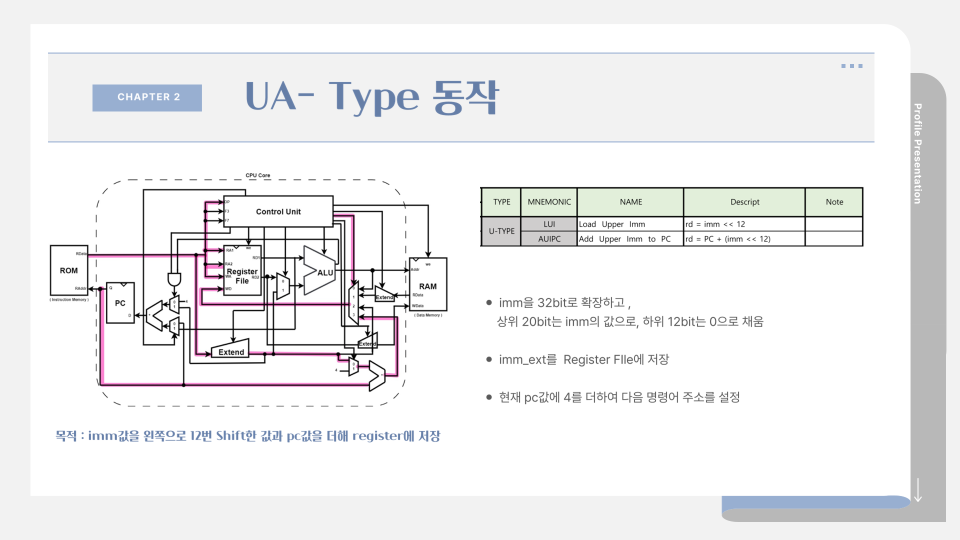

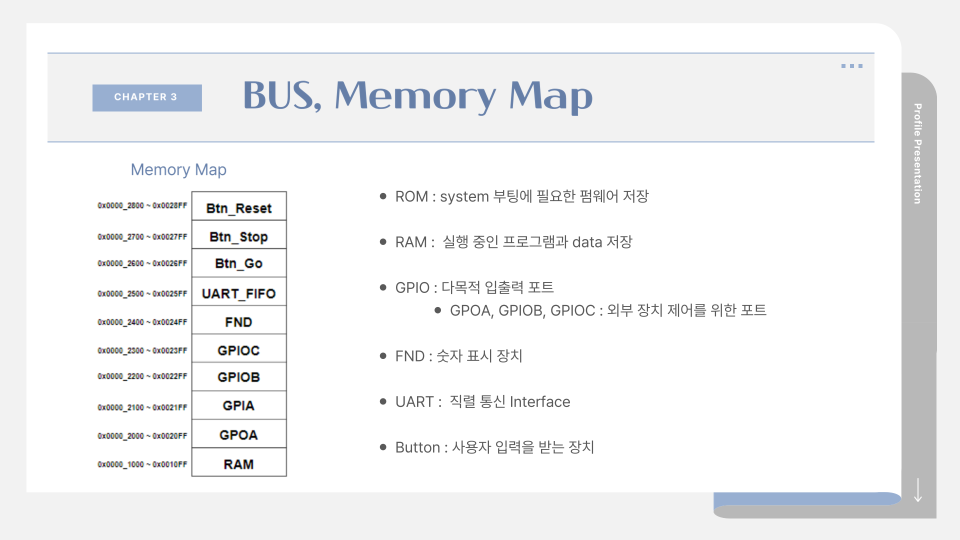

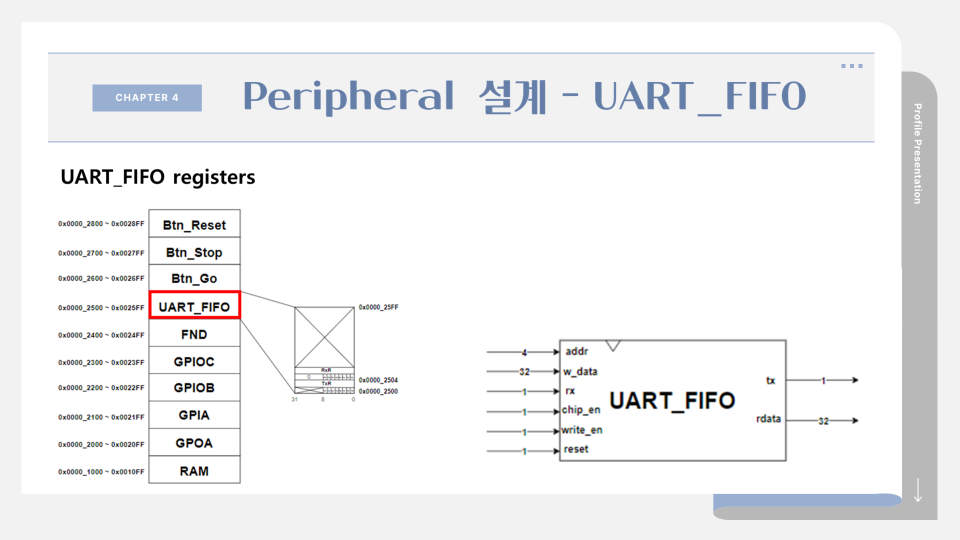

CPU는 기본적으로 Control Unit, Data Path, ROM, RAM으로 구성되있다.

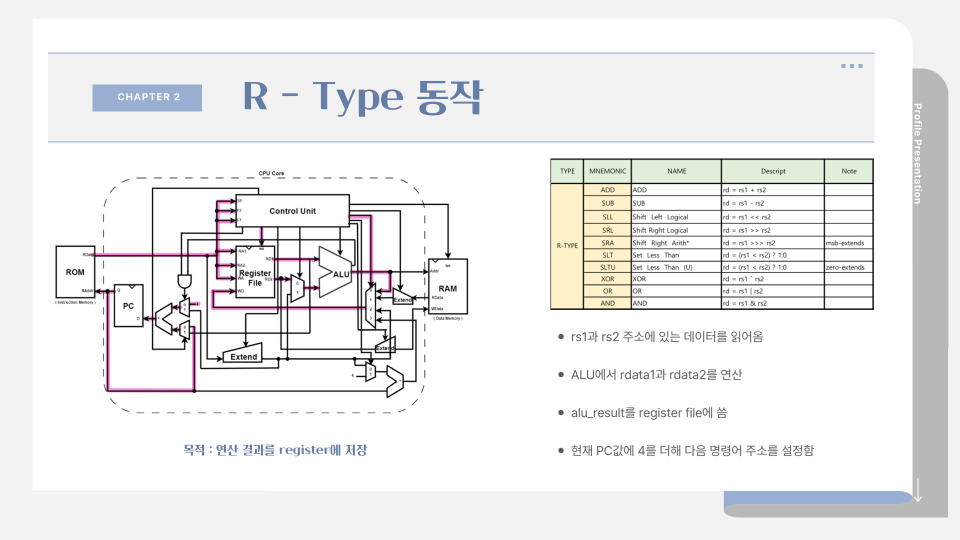

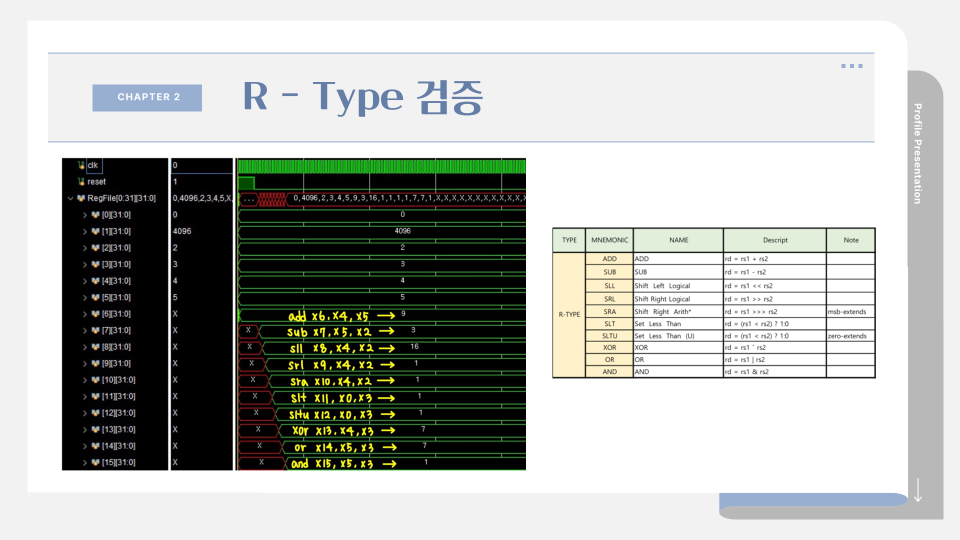

R-Type은 ALU를 통한 연산결과를 register file에 저장하는 역할을 한다.

여기서 shift연산은 "<<, >>, >>>" 3가지가 있다.

">>>"는 shift동작 시 msb가 확장되는 특징을 가지고 있다.

R-Type의 명령어들을 Simulation결과를 통해 확인하였다.

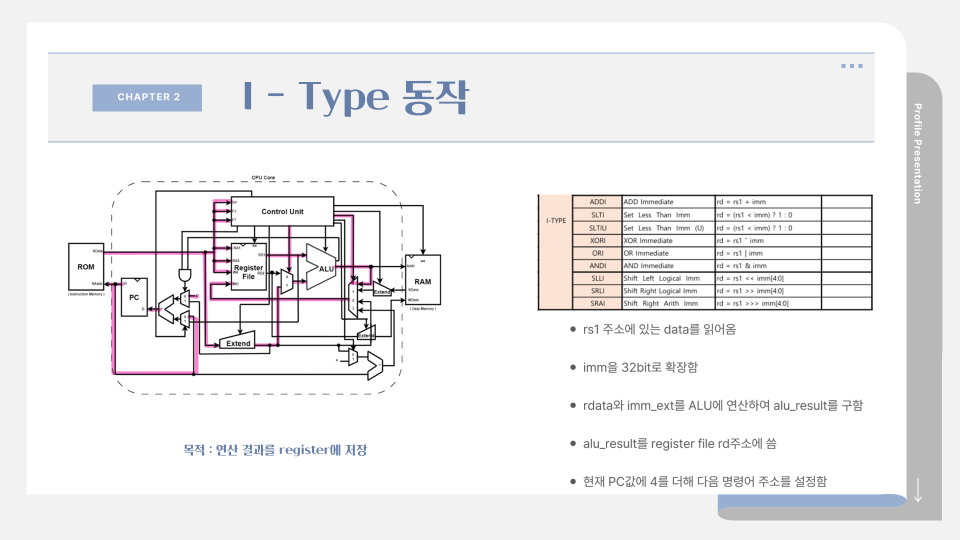

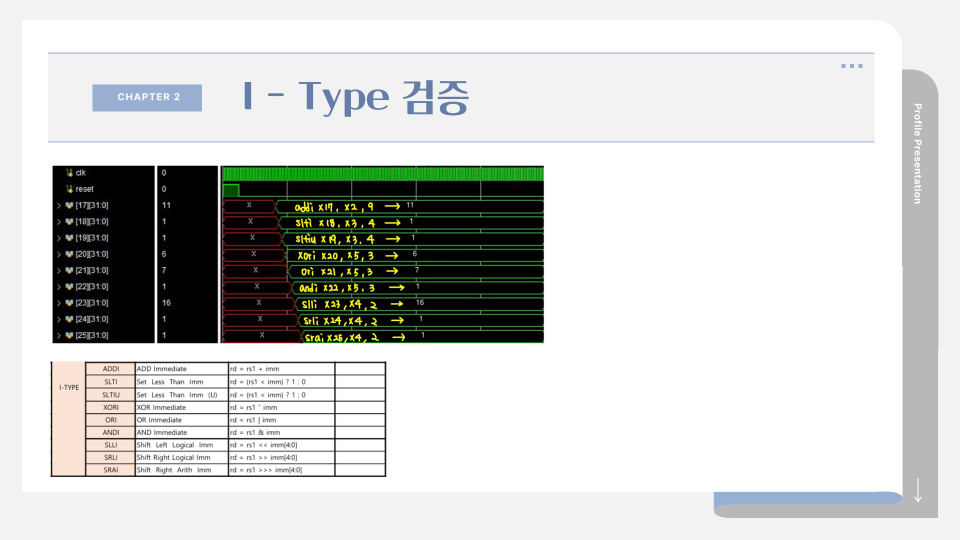

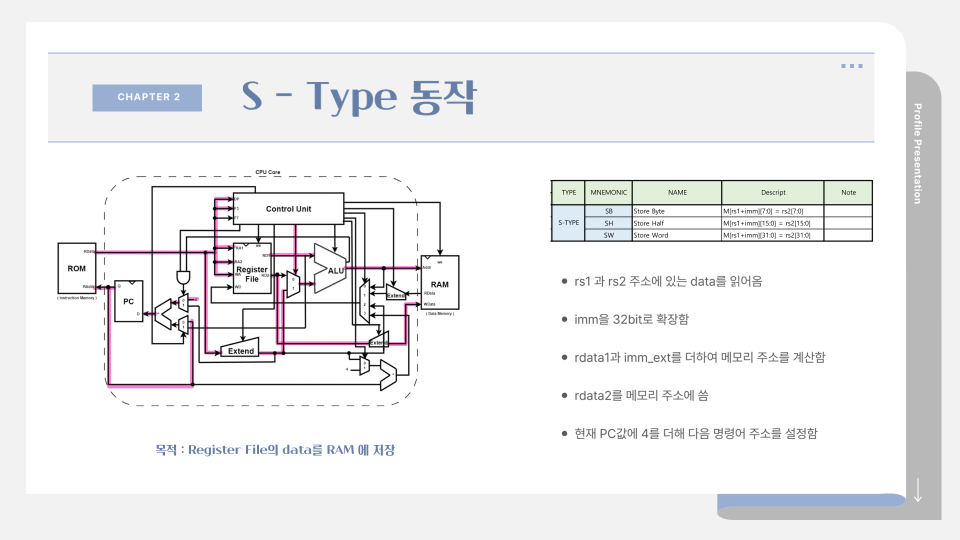

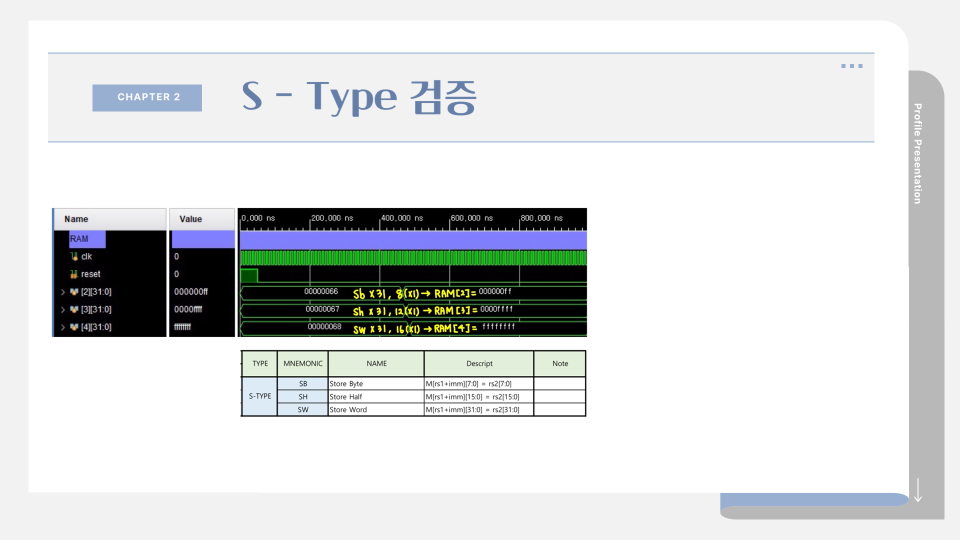

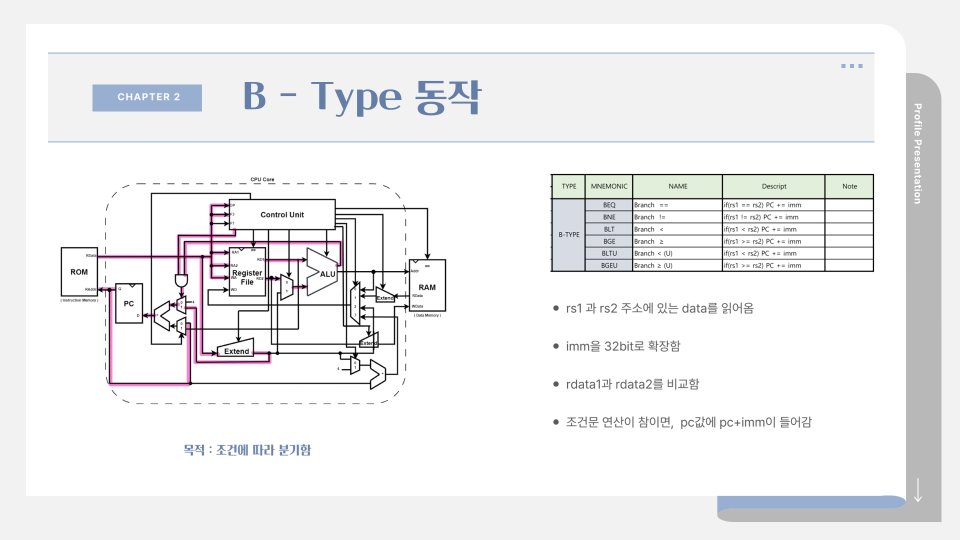

I-Type에는 RAM에 데이터를 register로 load하는 기능과 연산결과를 register에 저장하는 기능이 있다.

rs1과 immediate의 연산 결과를 register에 저장하는 명령을 simulation한 결과다.

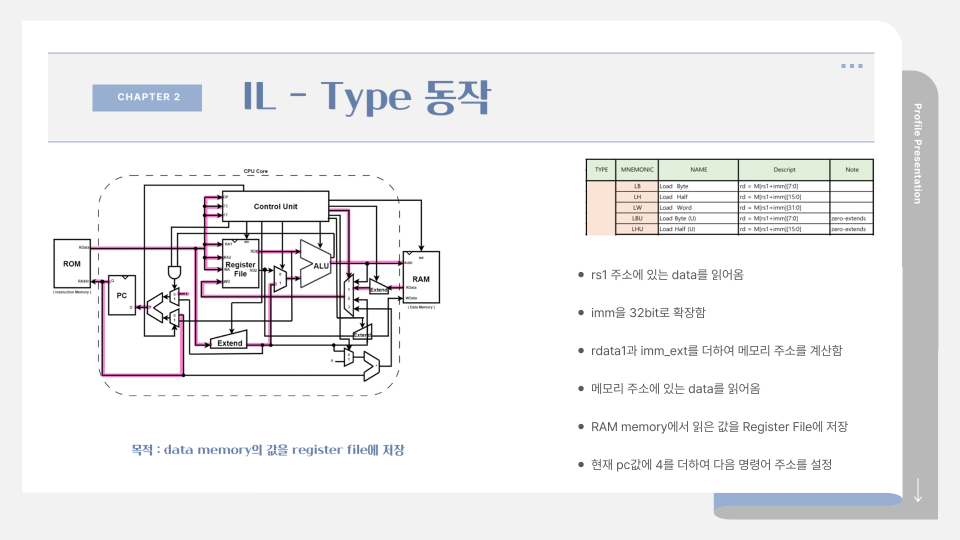

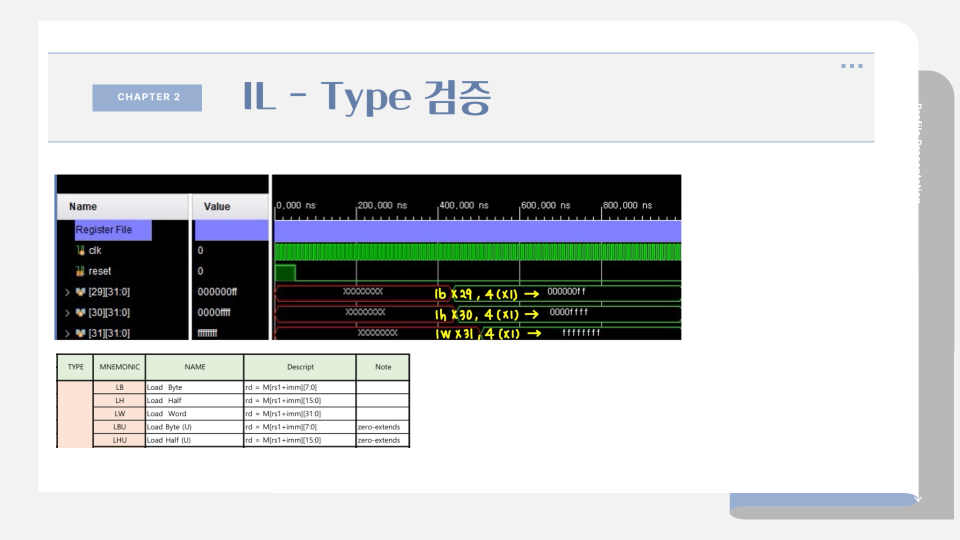

I-Type에서 다른 동작을 하는 명령을 IL-Type이라 했다. 이 명령들은 메모리의 데이터를 register로 load하는 동작이다.

임의로 RAM값을 0xffffffff로 초기화하고, 명령어를 simulation결과 Byte, Half, Word동작이 잘 나타난다.

고찰 작성 필요