컴퓨터에는 연산을 담당하는 CPU뿐만 아니라 여러 Peripheral들로 구성되 있다. CPU와 Peripheral들이 data를 주고받기 위해서는 BUS라는 data이동 통로가 필요하다.

Simple BUS

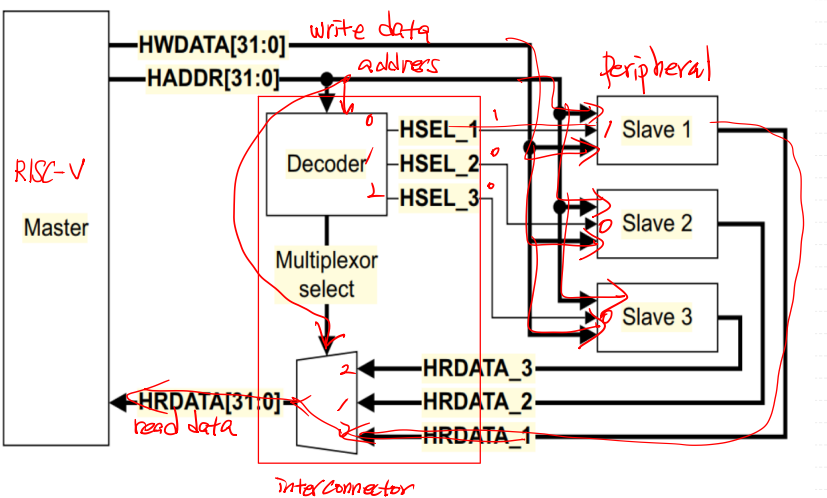

AMBA AHB Lite구조를 이용해 burst기능이 제외된 Simple Bus를 설계하였다.

Address, Write data, Read data는 broadcasting방식으로 모든 Peripheral에 전달되고, Address가 Bus Interconnector에 입력되어 Decoder와 MUX를 통해 Peripheral을 선택할 수 있게 된다.

여기서 Address로 Peripheral에 접근하기 위해 "Memory Mapped I/O"로 각각의 Peripheral에 주소를 부여하여 접근하는 방식을 사용한다.

설계한 Memory Mapped I/O는 Instruction Memory를 제외하고, RAM, GPIO, FND, UART, Button에 주소를 지정하여 사용하고 있다.