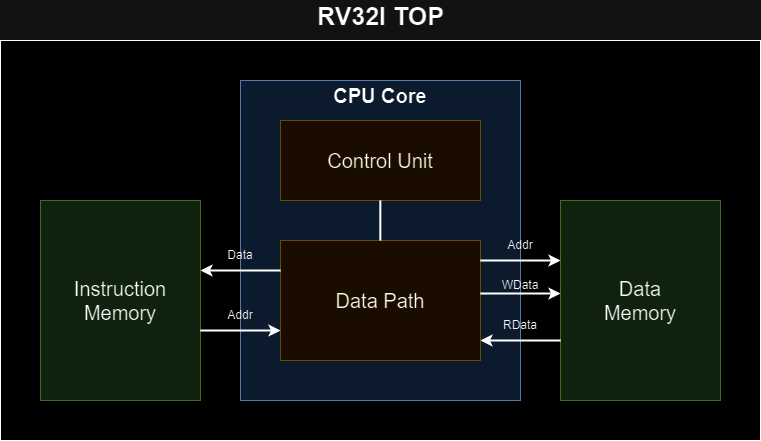

RISC-V는 무료 오픈소스 RISC 아키텍처다. RISC-V의 여러 종류 중에 기본 정수형인 RV32I ISA를 구현해볼 것이다. RV32I는 32bit Integer로 구성되어 곱셈, 나눗셈, 소수점은 포함되지 않는다.

만들어볼 CPU는 Single Cycle로 동작하게 된다.

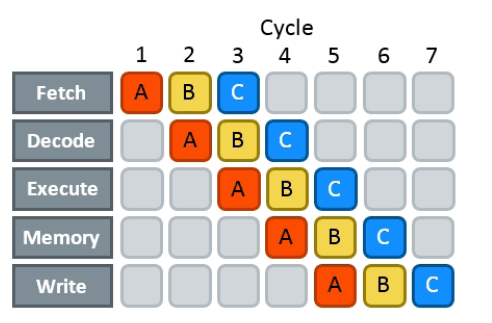

Single Cycle로 동작하는 CPU는 한클럭에 명령어가 실행이 완료되므로 명령 예측이 쉽고, 하드웨어가 단순해진다.

그러나 모든 명령을 한클럭에 실행해야 되므로 특정 명령의 실행시간이 길어질 경우 클럭속도가 느려지는 단점을 가지고 있다.

Multi Cycle 동작을 구현하려면 Pipeline을 통해 Fetch, Decode, Excute, MemAccess, WriteBack으로 나누어 각 구간에 레지스터를 구성해 명령어를 여러 클럭으로 동작시킬 수 있다. CPU성능을 향상시키고, 클럭속도를 높일 수 있다. 그러나 pipeline을 구성하게 되면 명령어 사이의 종속성과 리소스관리를 고려해야 하는 복잡성을 가지고 있다.

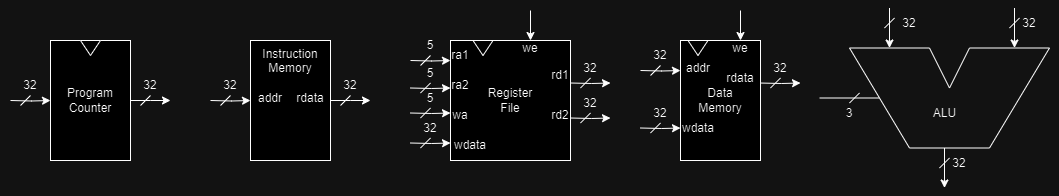

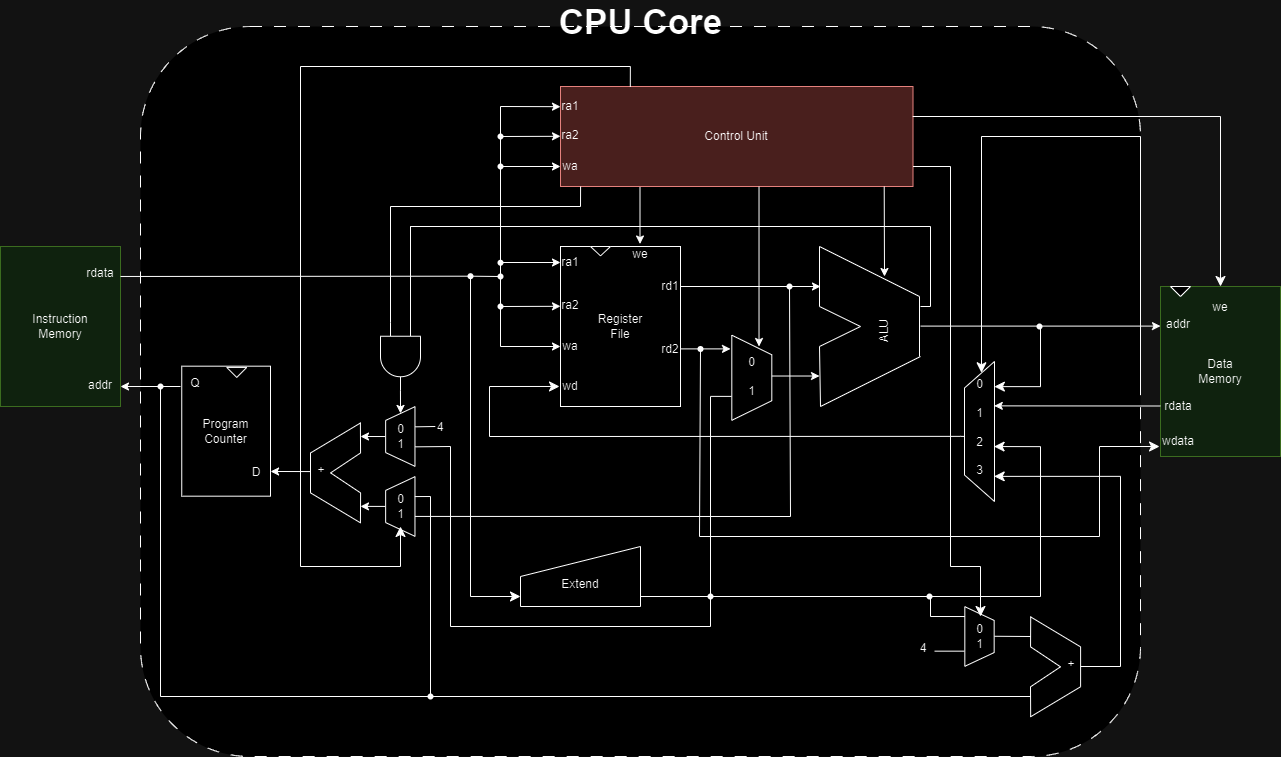

CPU 기본 모듈

-

ALU : 덧셈, 뺄셈, and, or 등을 수행하는 조합회로

-

Register File : 데이터를 읽고 쓸 수 있는 공간, 레지스터 여러개가 파일형태로 존재

-

Program Counter : Instruction의 주소를 가지고 있는 Register

-

Instruction Memory : 명령어가 저장되있는 공간, ROM

-

Data Memory : Data가 저장되있는 공간, RAM

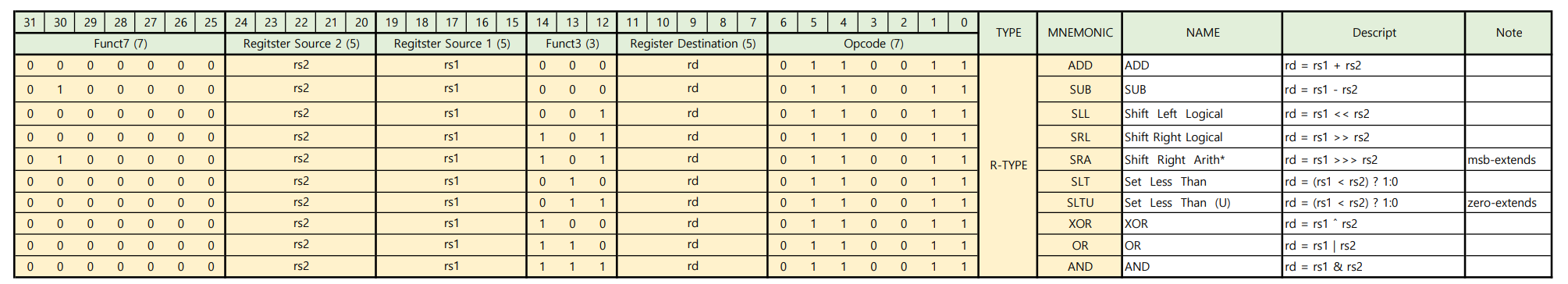

R-Type

type은 opcode에 의해 구분되며, R-Type의 경우 func7과 func5에 의해 Mnemonic(Assembly 명령어)을 구분한다.

ADD동작을 해석하면 "ADD rd, rs1, rs2"는 rs1과 rs2를 더해 rd에 저장한다는 의미다.

여기서 rd(register destination)는 레지스터파일에 write되는 주소를 말하고, rs(register source)는 레지스터파일에서 read하기 위한 주소를 말한다.

Instruction Set은 Instruction Memory에 저장되 있고, cpu가 동작하면 Instruction이 register file과 control unit으로 필요한 정보들이 전달된다.

R-Type은 ALU의 연산 결과를 register file에 저장하는 목적을 가지고 있다.

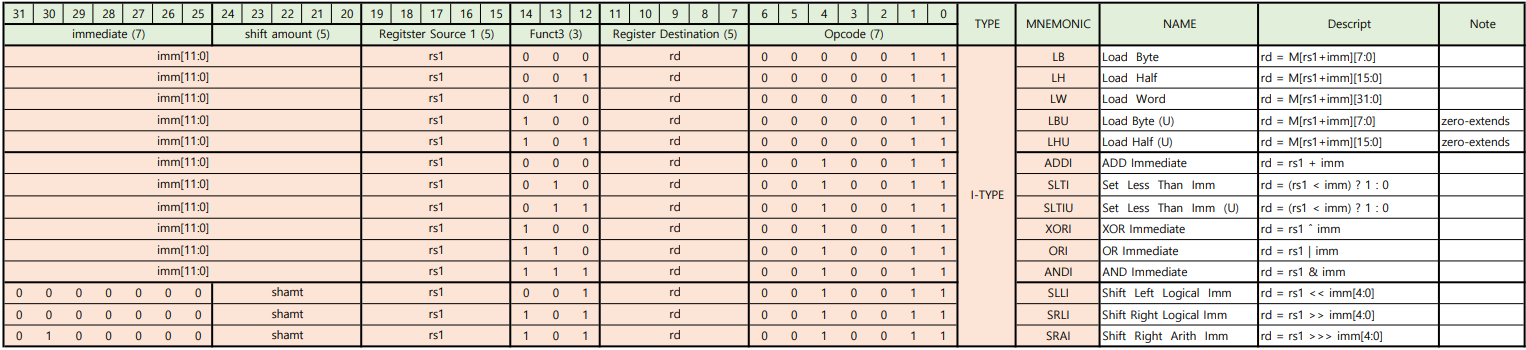

I-Type

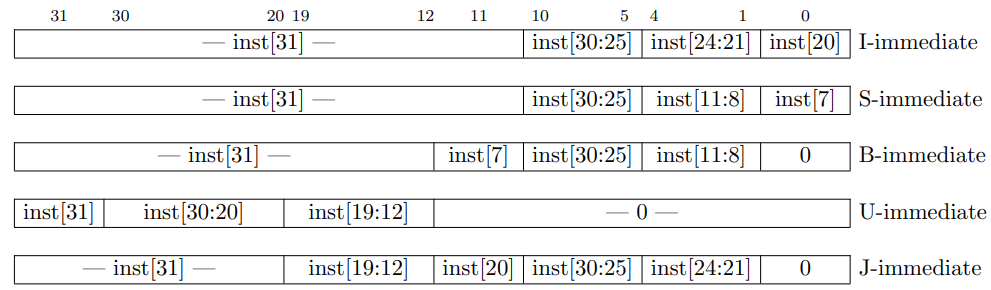

I-Type은 R-Type과 다르게 immediate값을 가지고 있어 12bit의 imm을 32bit로 확장시키는 Extend하드웨어를 구성해야한다.

LW동작을 해석하면 "LW rd, imm(rs1)"는 imm과 rs1을 더한 값을 RAM주소에 접근하여 데이터를 register file에 저장한다.

Extend하드웨어를 만들때는 아래 datasheet를 기반으로 만들어준다.

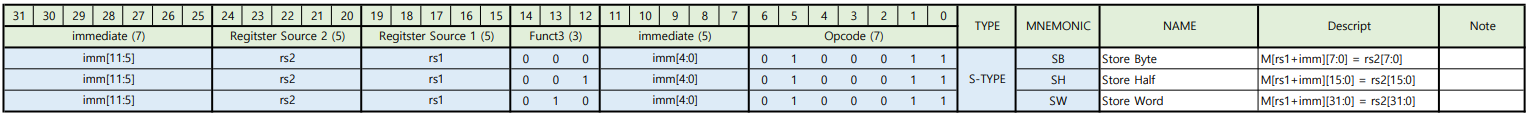

S-Type

S-Type은 데이터를 RAM에 저장하는 목적이 있다.

SW동작을 보면 "SW rs2, imm(rs1)"는 imm과 rs1을 더하고, 결과값을 메모리 주소로 하여 RAM에 rs2값을 저장한다.

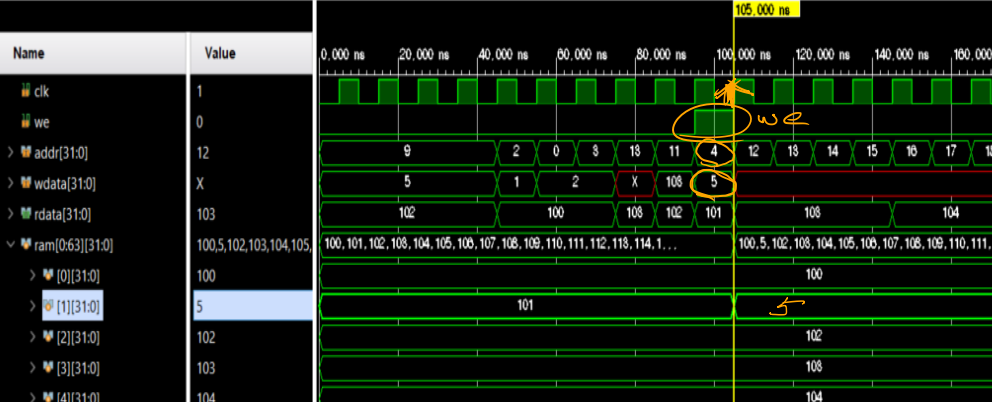

simulation결과를 보면 WE, address, wdata가 ram에 입력되고, 입력결과가 RAM에 잘 저장되는 모습을 볼 수 있다.

나머지 Type들도 Instruction Set을 분석하고, Control Unit신호와 Data Path하드웨어를 구성하면서 구현할 수 있다.

위 그림은 RV32I Instruction Set을 모두 구현한 Architecture이다.