2x1 MUX

2개의 입력중 어느 하나의 입력신호를 선택하여 출력으로 보내주는 논리회로다.

| IN | S0 | OUT |

|---|---|---|

| A | 0 | A |

| B | 1 | B |

NAND로 이루어진 Logic Gate 그리고 CMOS Switch 2가지 방법으로 만들어 보겠다.

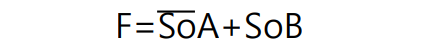

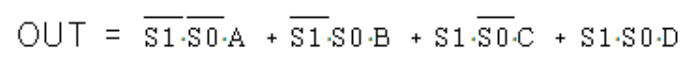

크기비교

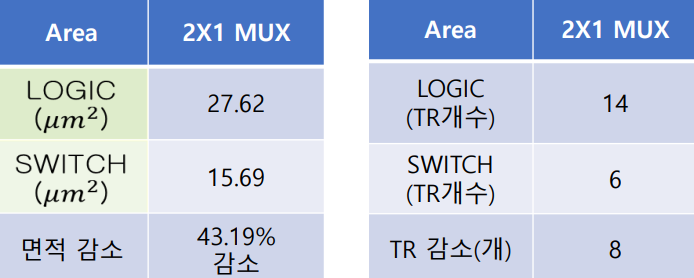

Logic Gate

schematic

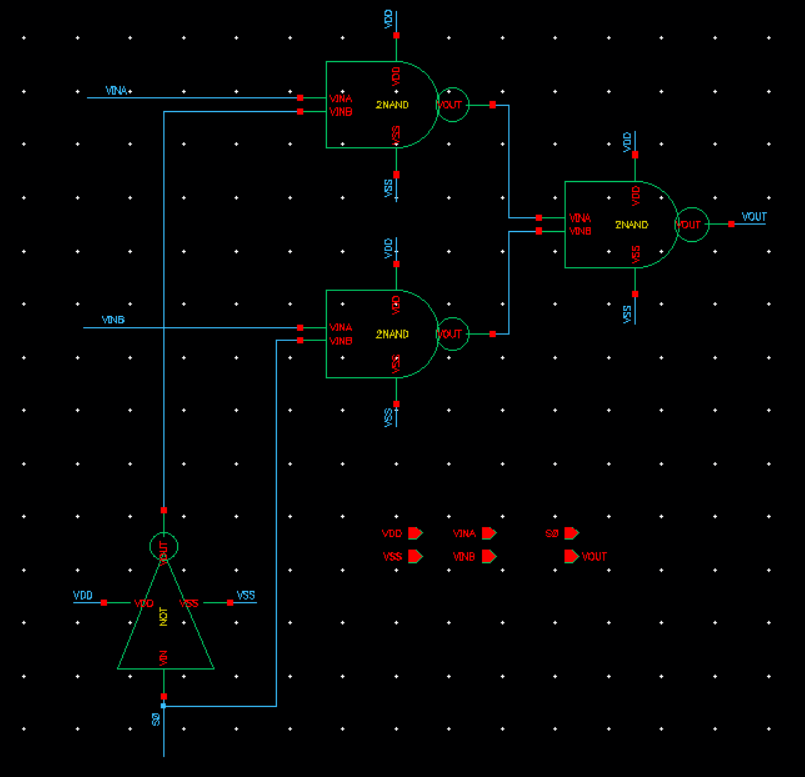

symbol & test simulation setup

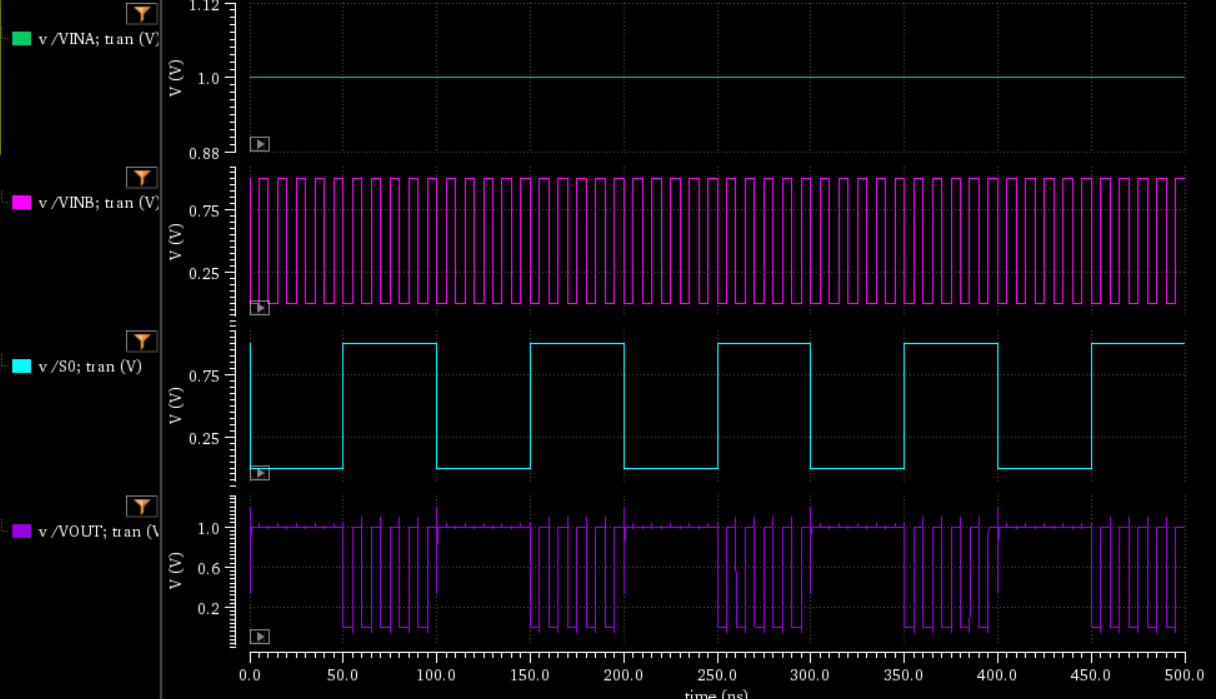

waveform

세번째 파란색 파형은 S0로 0일때 A값이 출력되고, 1일때 B의 pulse가 출력되어 정상적으로 MUX가 동작하는 것을 볼 수 있다.

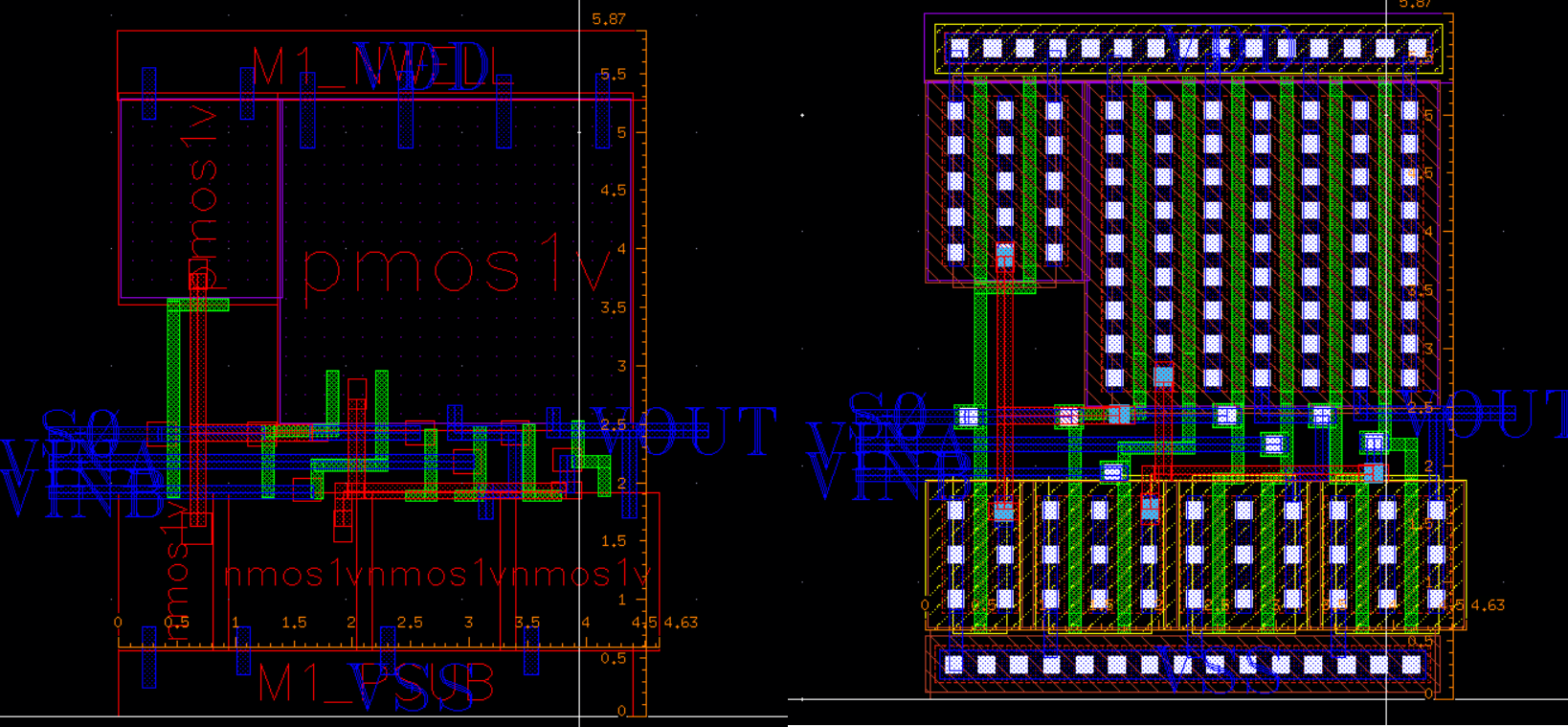

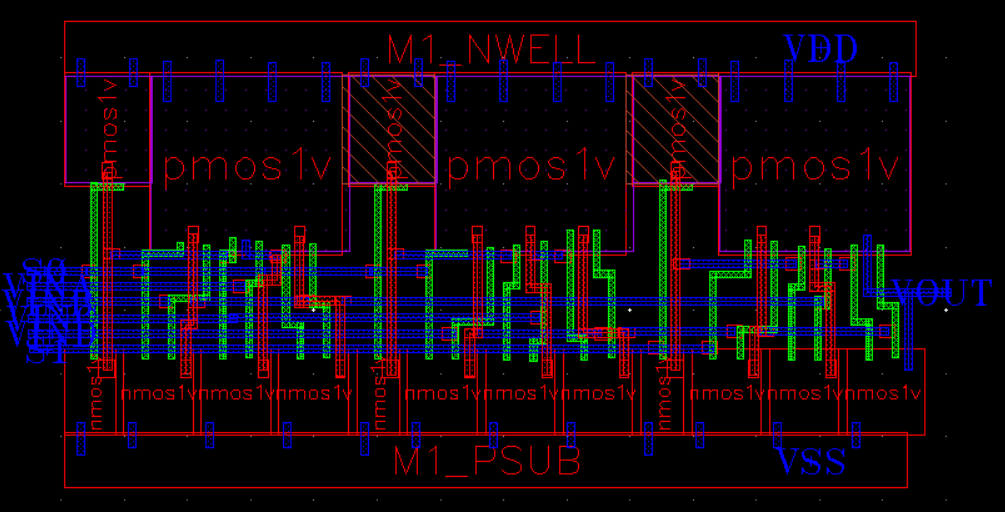

layout

이때 inverter의 pmos는 낭비되는 면적이 있으므로 2finger로 묶으면 낭비되는 면적이 줄어든다.

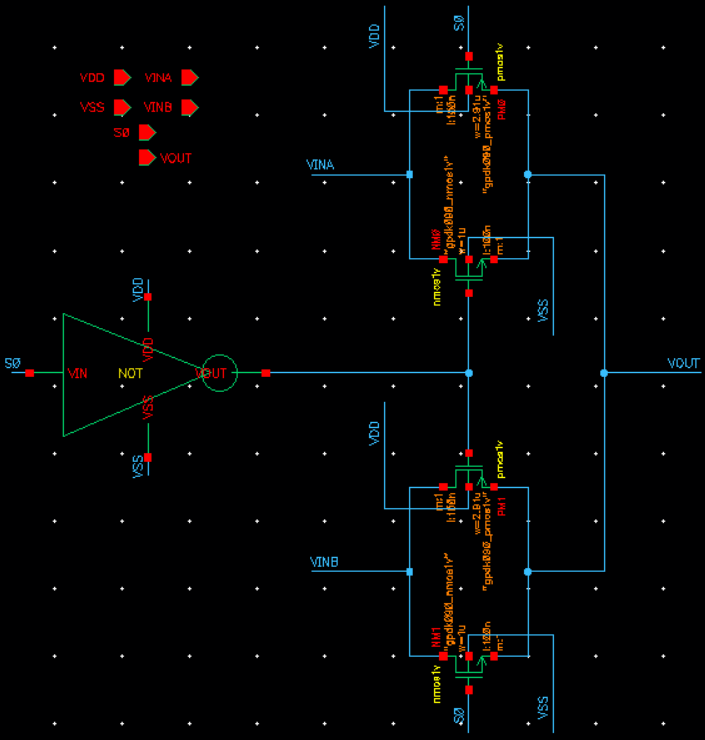

CMOS SWITCH

schematic

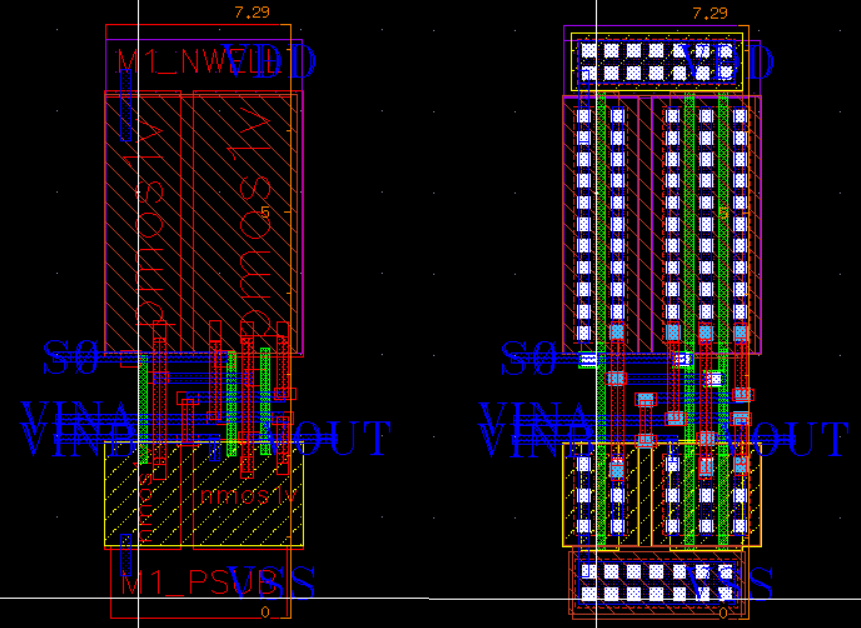

layout

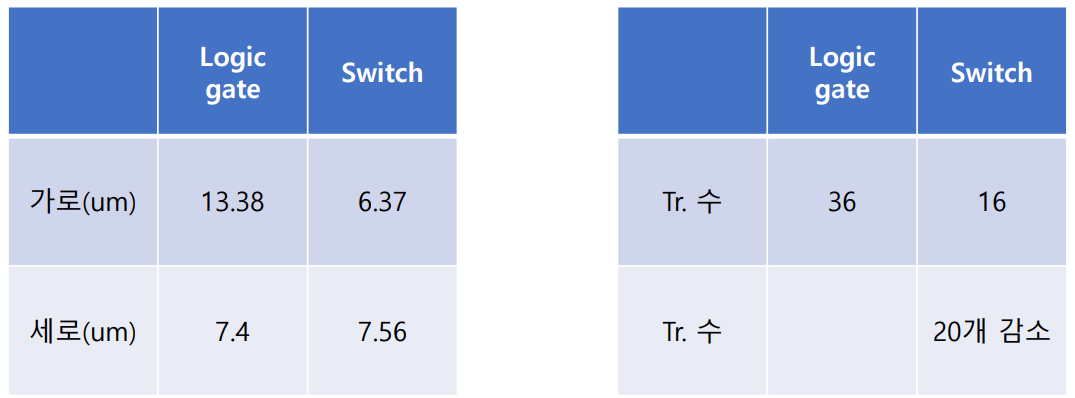

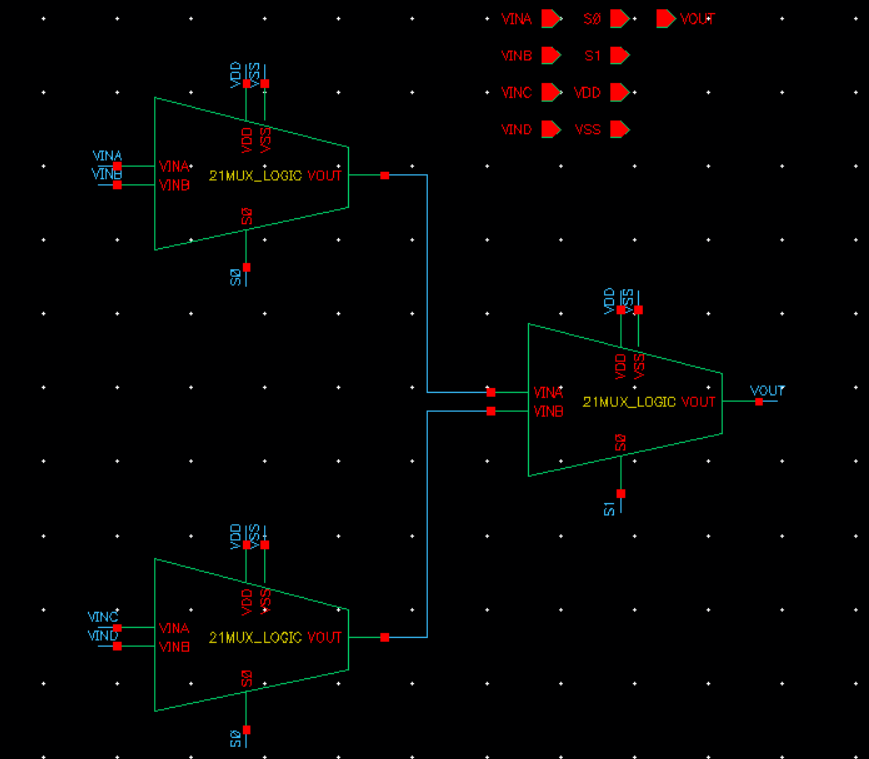

4x1 MUX

4개의 입력중 어느 하나의 입력신호를 선택하여 출력으로 보내주는 논리회로다.

| S0 | S1 | OUT |

|---|---|---|

| 0 | 0 | A |

| 0 | 1 | B |

| 1 | 0 | C |

| 1 | 1 | D |

크기비교

Logic gate

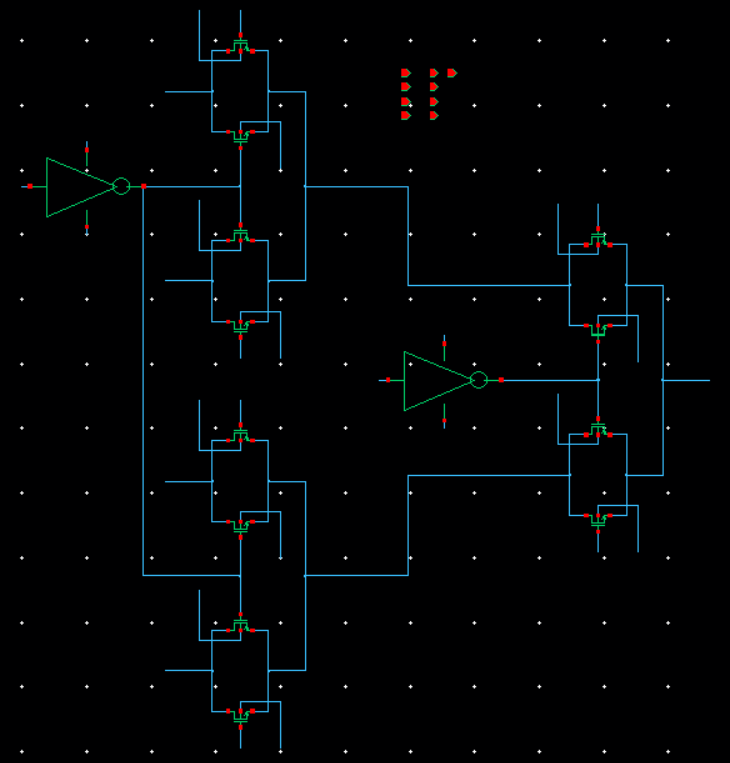

schematic

symbol & test simulation setup

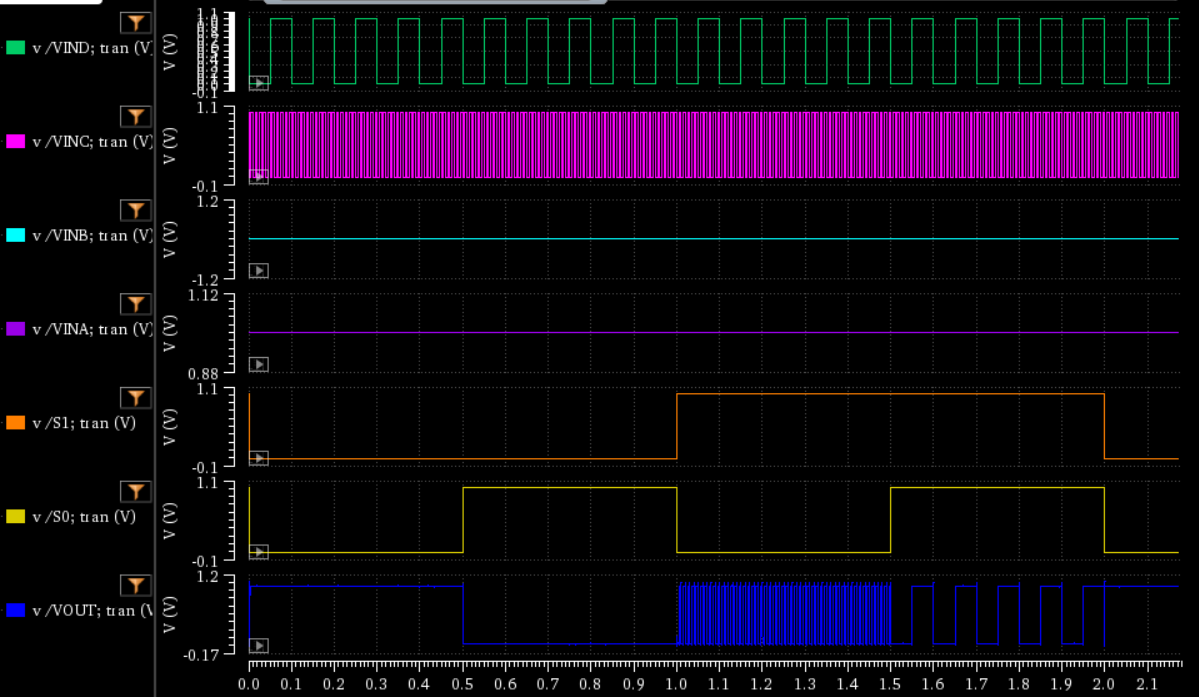

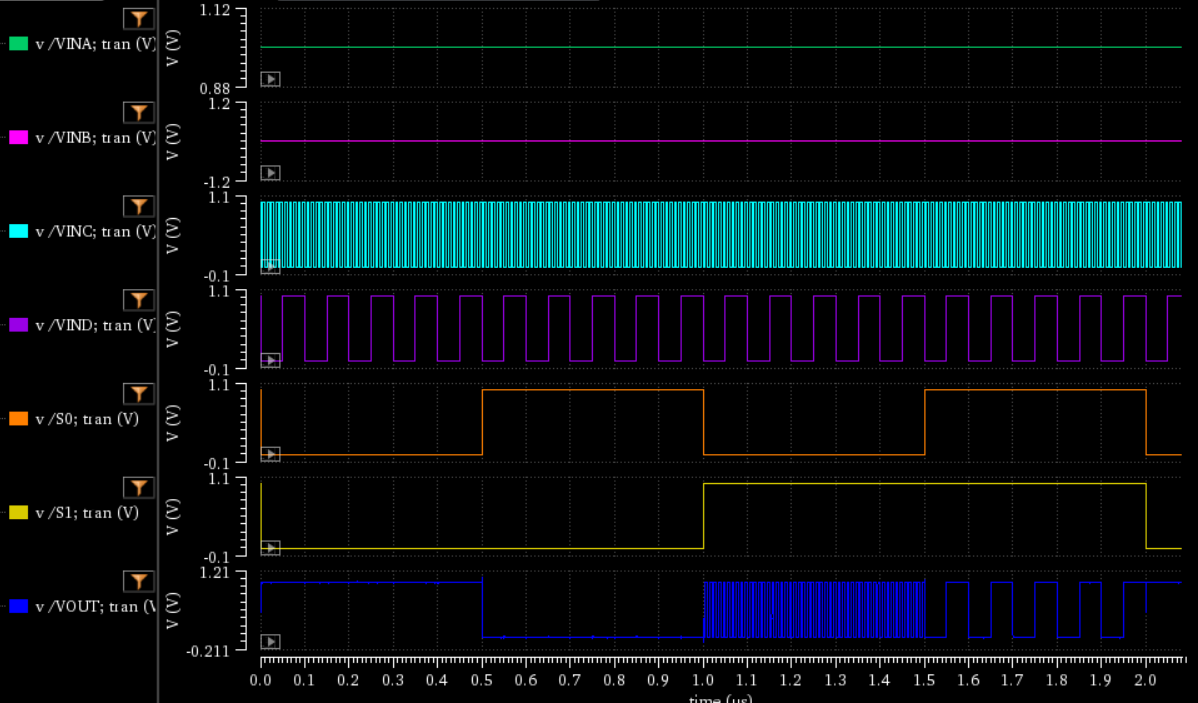

waveform

S0와 S1의 논리에 따라 VOUT이 달라지는 것을 확인

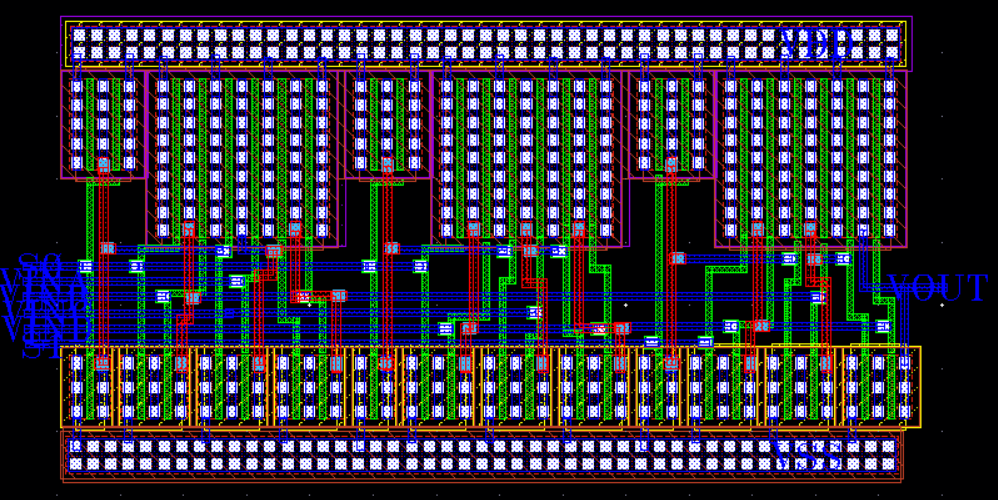

layout

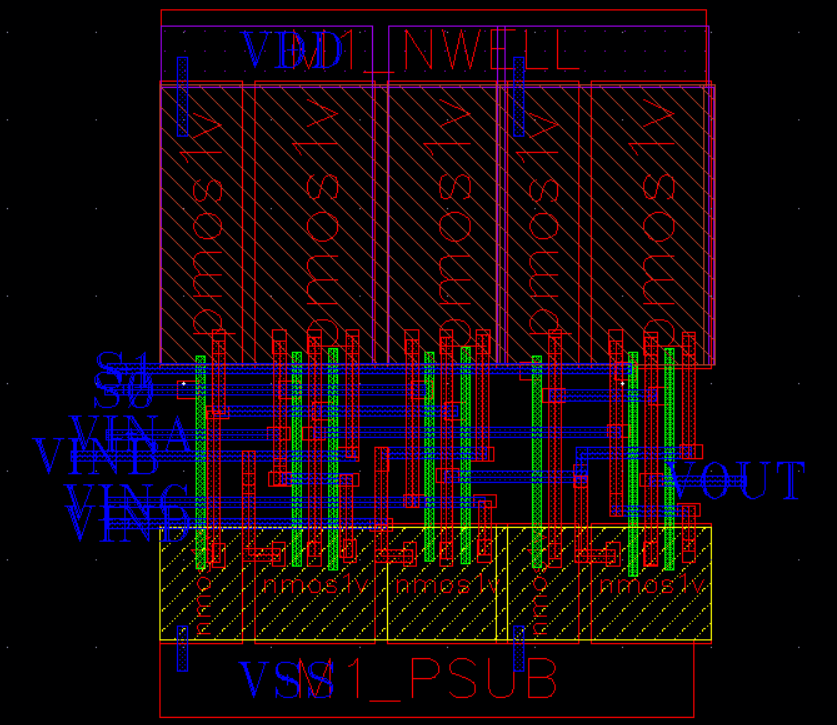

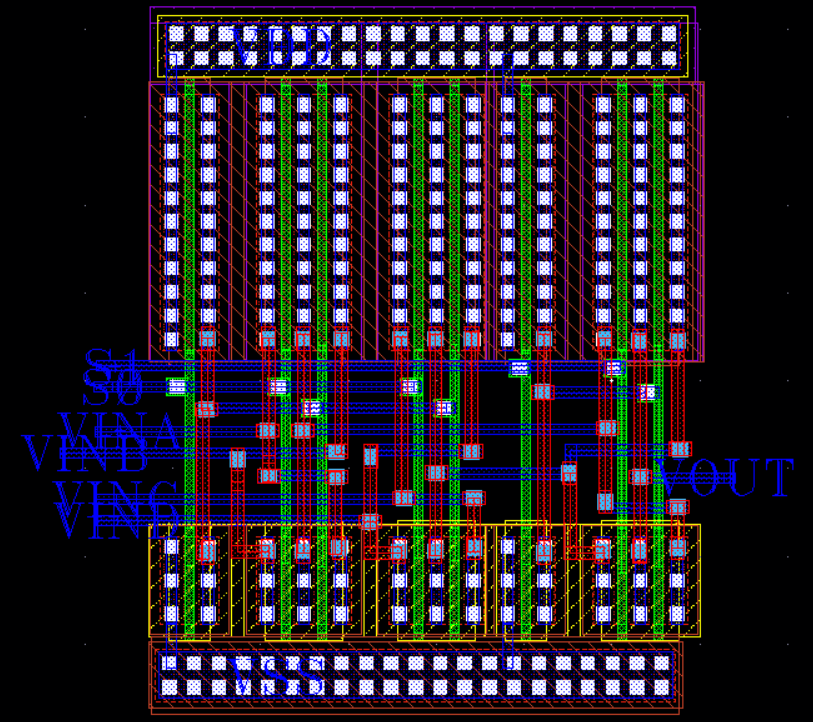

CMOS SWITCH

schematic

waveform

logic gate와 같은 waveform결과 확인

layout

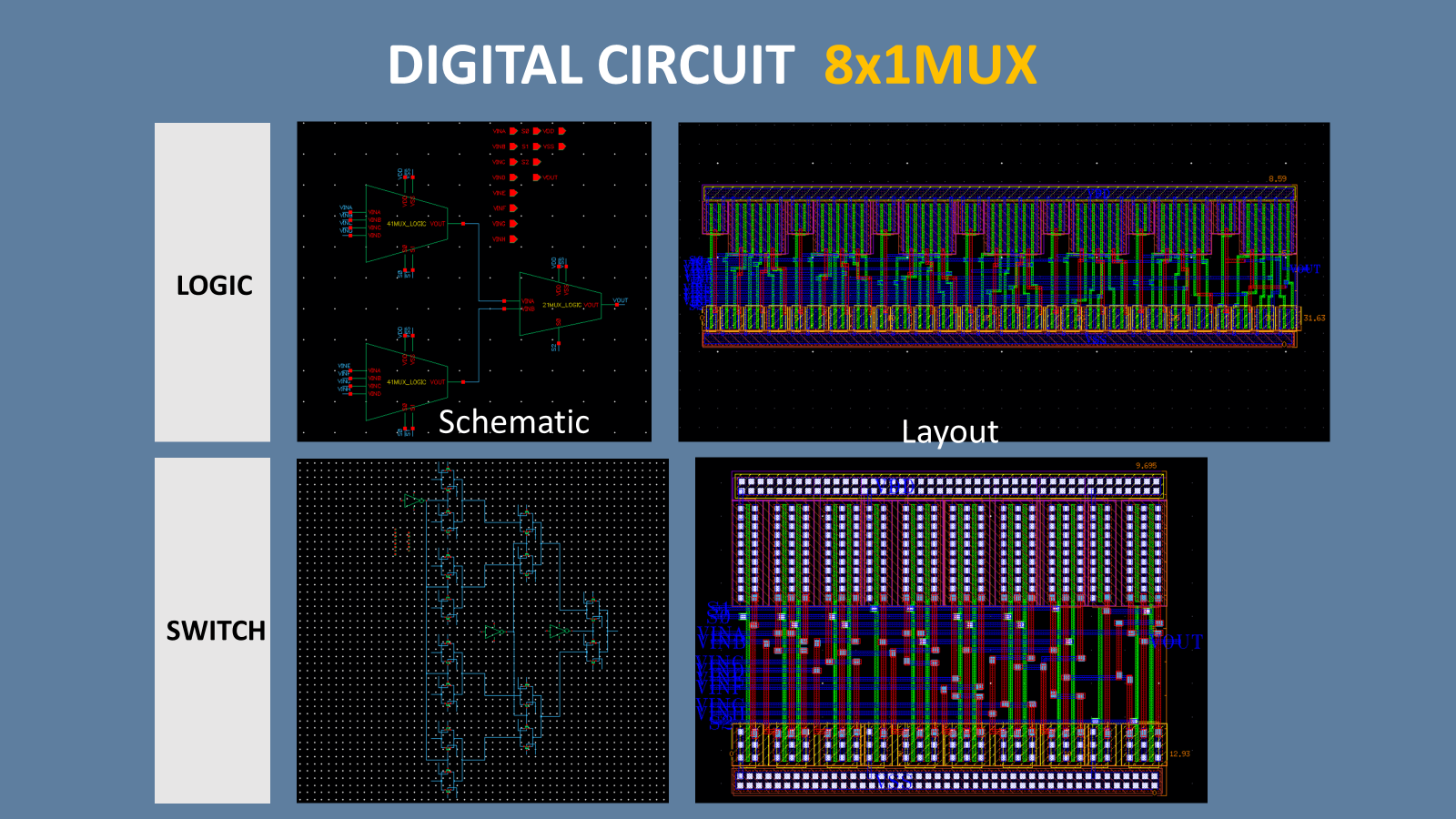

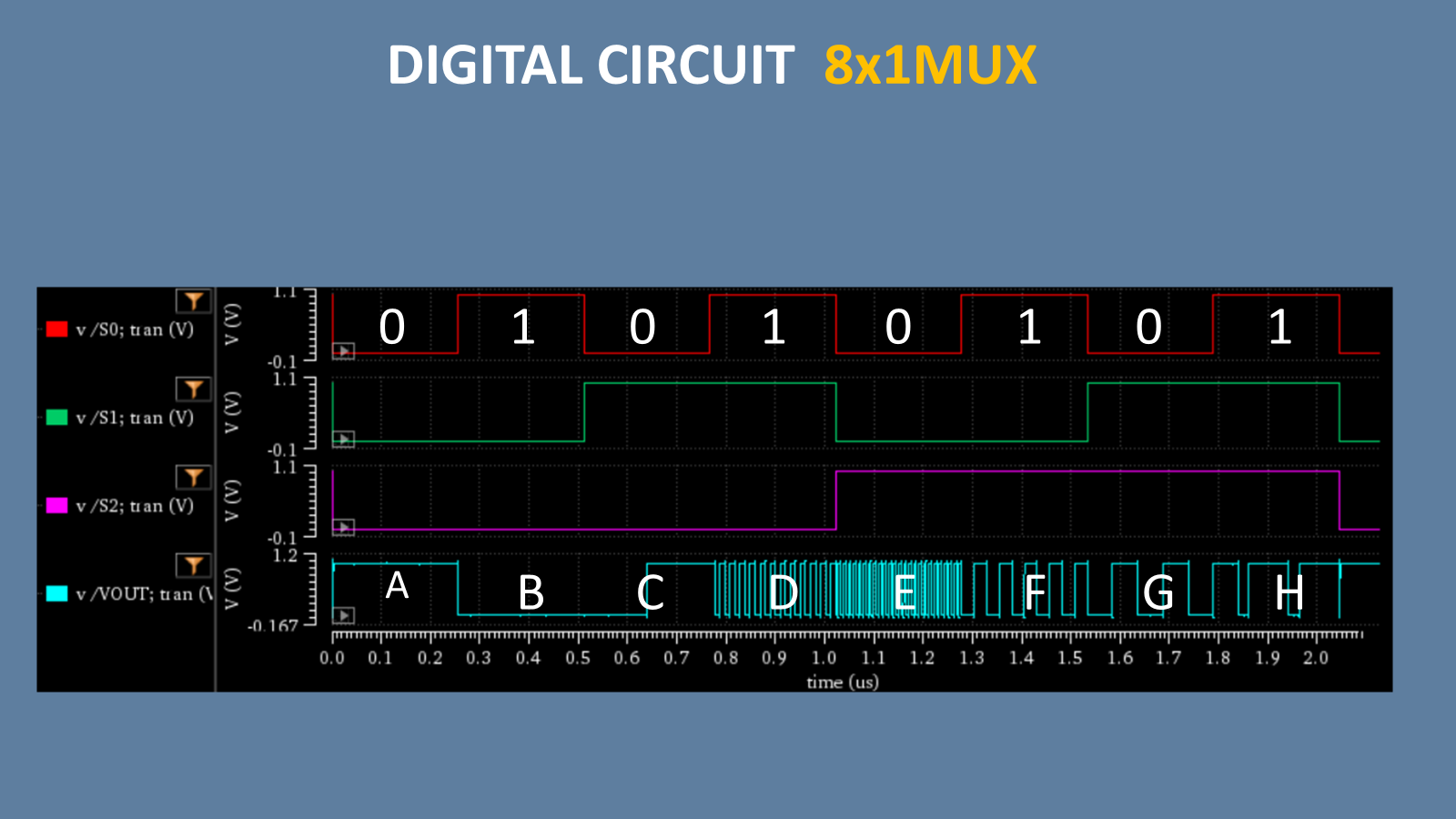

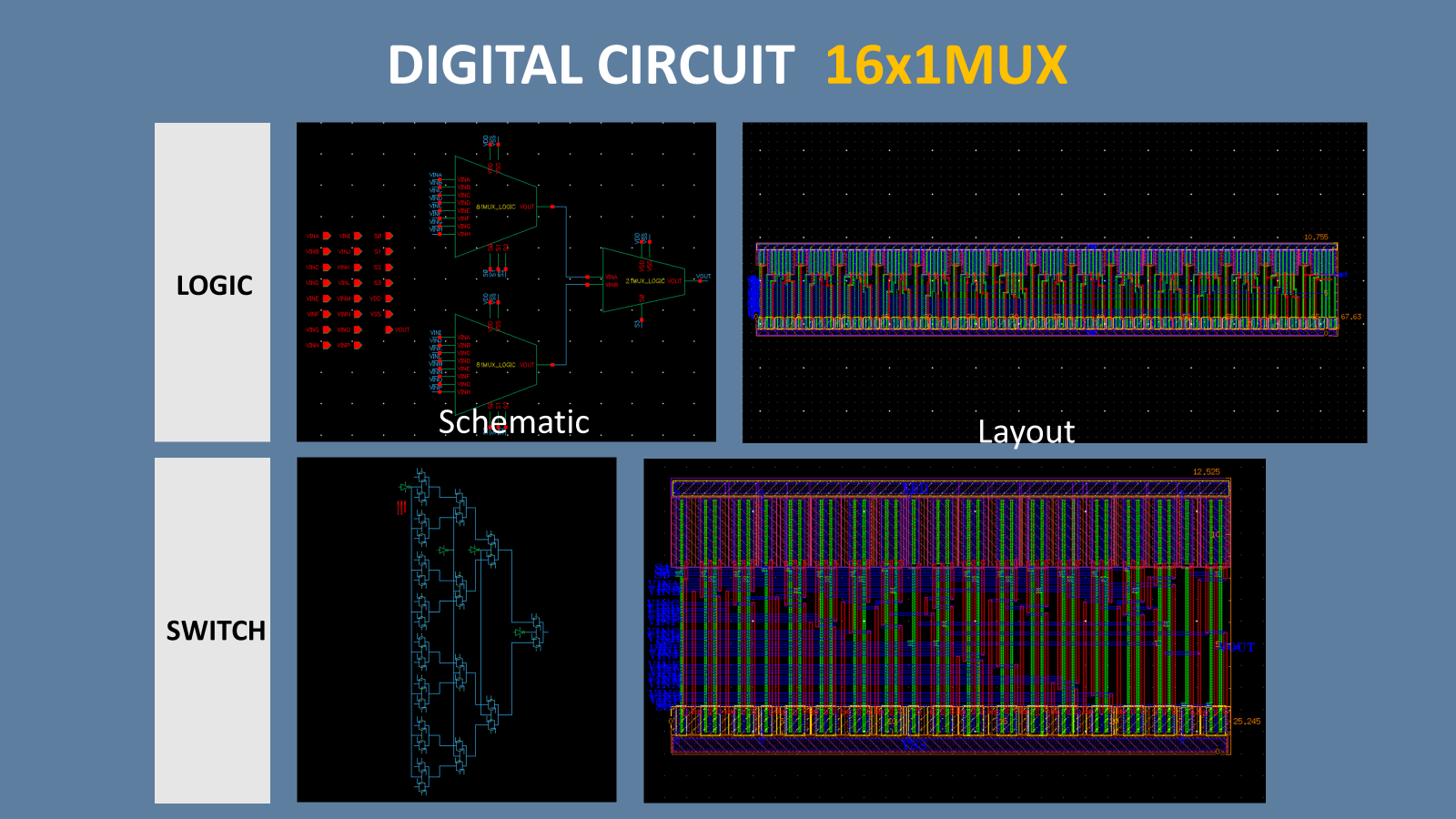

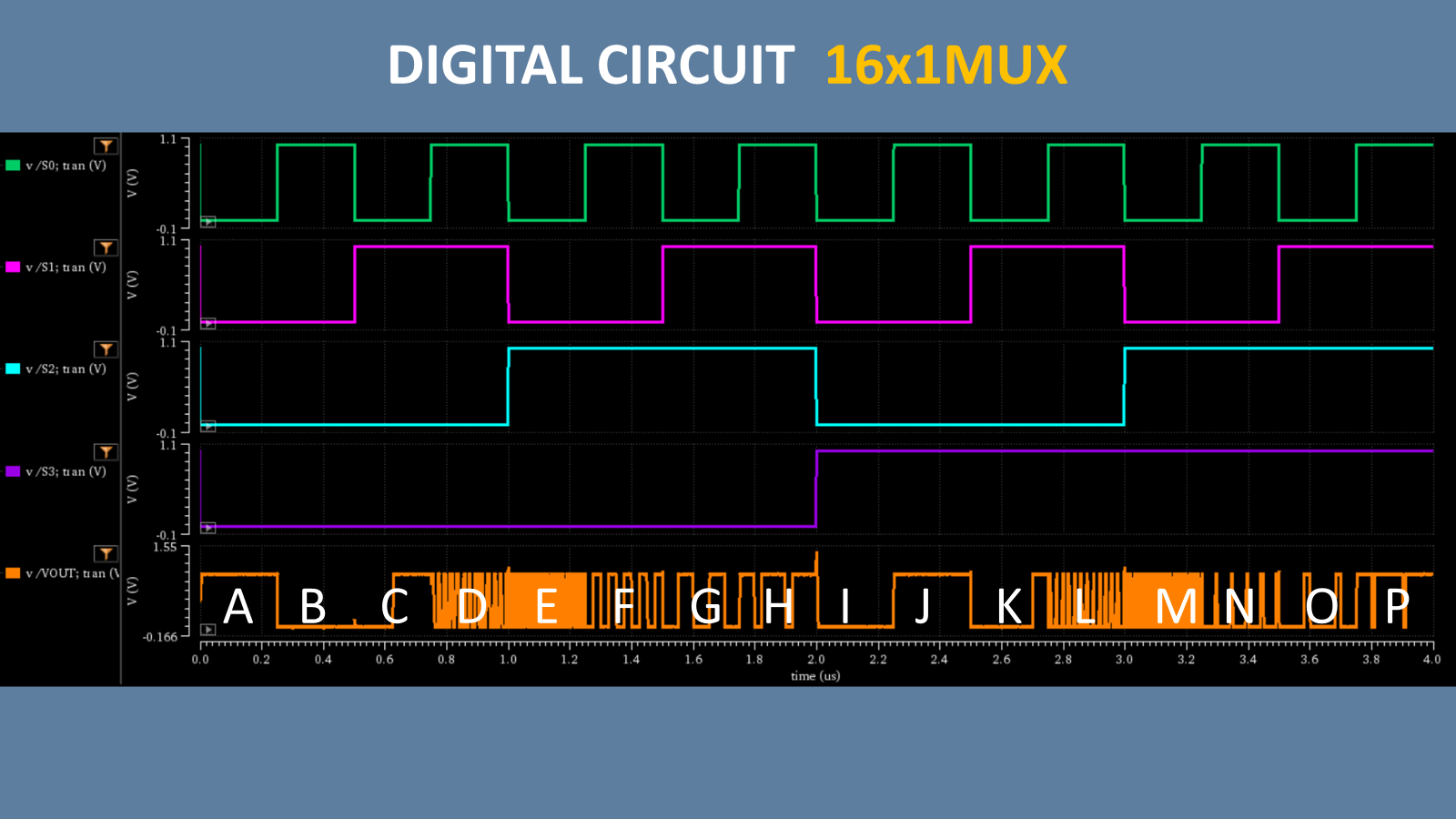

8x1 MUX / 16x1 MUX

앞서 설계했던 MUX와 같은 방식으로 만들 수 있다.

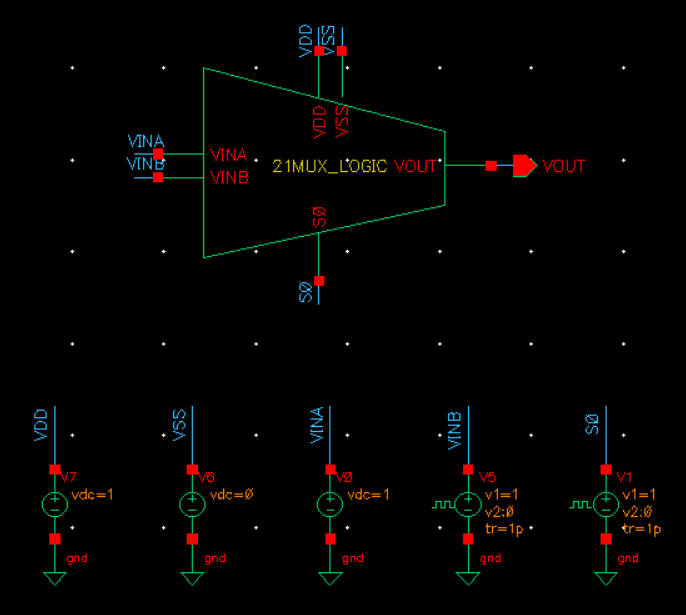

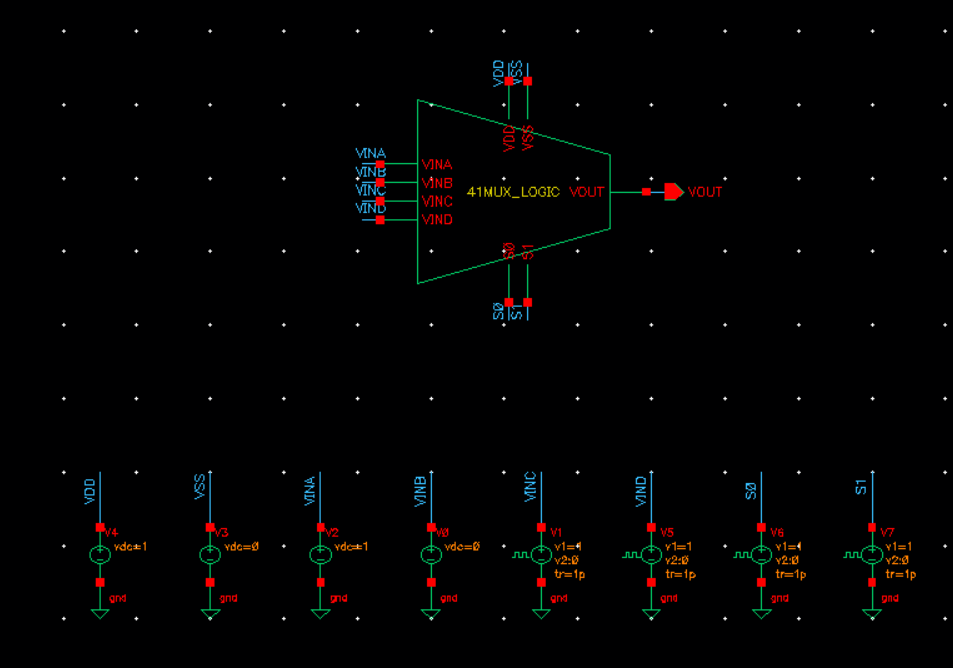

Conclusion

| Area | 2x1 MUX | 4x1 MUX | 8x1 MUX | 16x1 MUX |

|---|---|---|---|---|

| Logic | 27.1781 | 100.862 | 271.7017 | 727.3607 |

| Switch | 17.8605 | 50.451 | 125.3564 | 316.1936 |

| Ratio | 1.5217 | 1.9992 | 2.1674 | 2.3004 |

| Tr | 2x1 MUX | 4x1 MUX | 8x1 MUX | 16x1 MUX |

|---|---|---|---|---|

| Logic | 14 | 42 | 98 | 210 |

| Switch | 6 | 16 | 34 | 86 |

MUX를 설계하는데 있어 Logic과 Switch방식이 있고 두가지 방식으로 설계해본 결과 Tr과 Area에서 차이가 발생하였다. 칩을 설계하는데 있어 Power, Speed, Price를 고려하였을 때 Switch방식을 사용하는 것이 더 큰 장점을 가지는 것을 볼 수 있었다.