Full Custom IC Tema Project주제는 4bit_Shift_Register & SRAM이다.

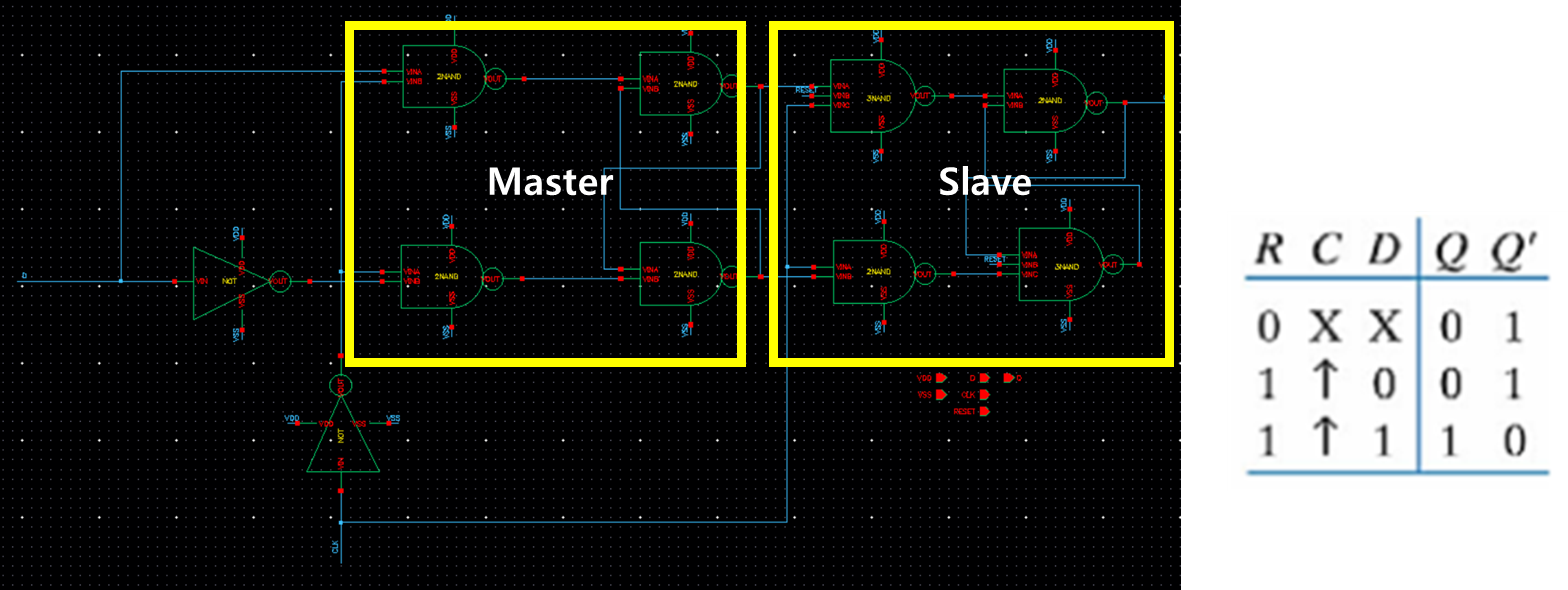

D Flip-Flop

Clk이 0일때 Master에 Data가 반영되고 Slave는 동작하지 않는다. 그리고 Clk이 1이 되면 Master에 있던 Data가 Slave에 반영되고 Master는 동작을 멈춘다.

즉, DFF는 Clk의 edge에서만 D가 Q로 반영된다.

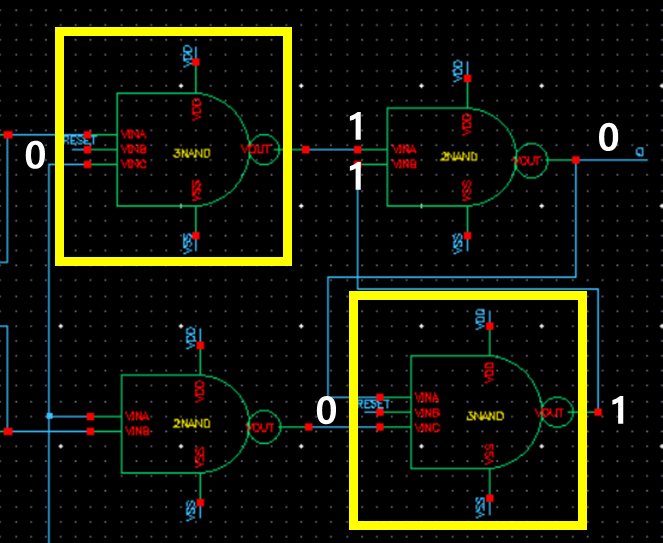

비동기식 Reset을 위해 위의 그림과 같이 3NAND 2개를 사용했다.

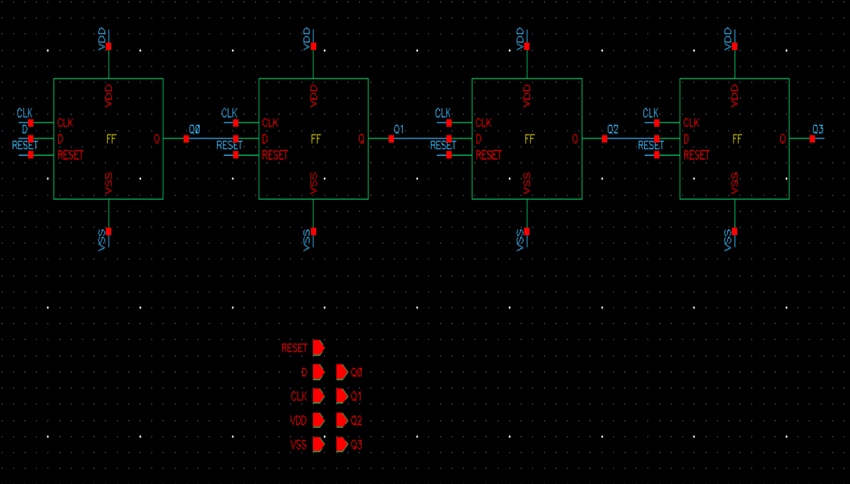

- Schematic

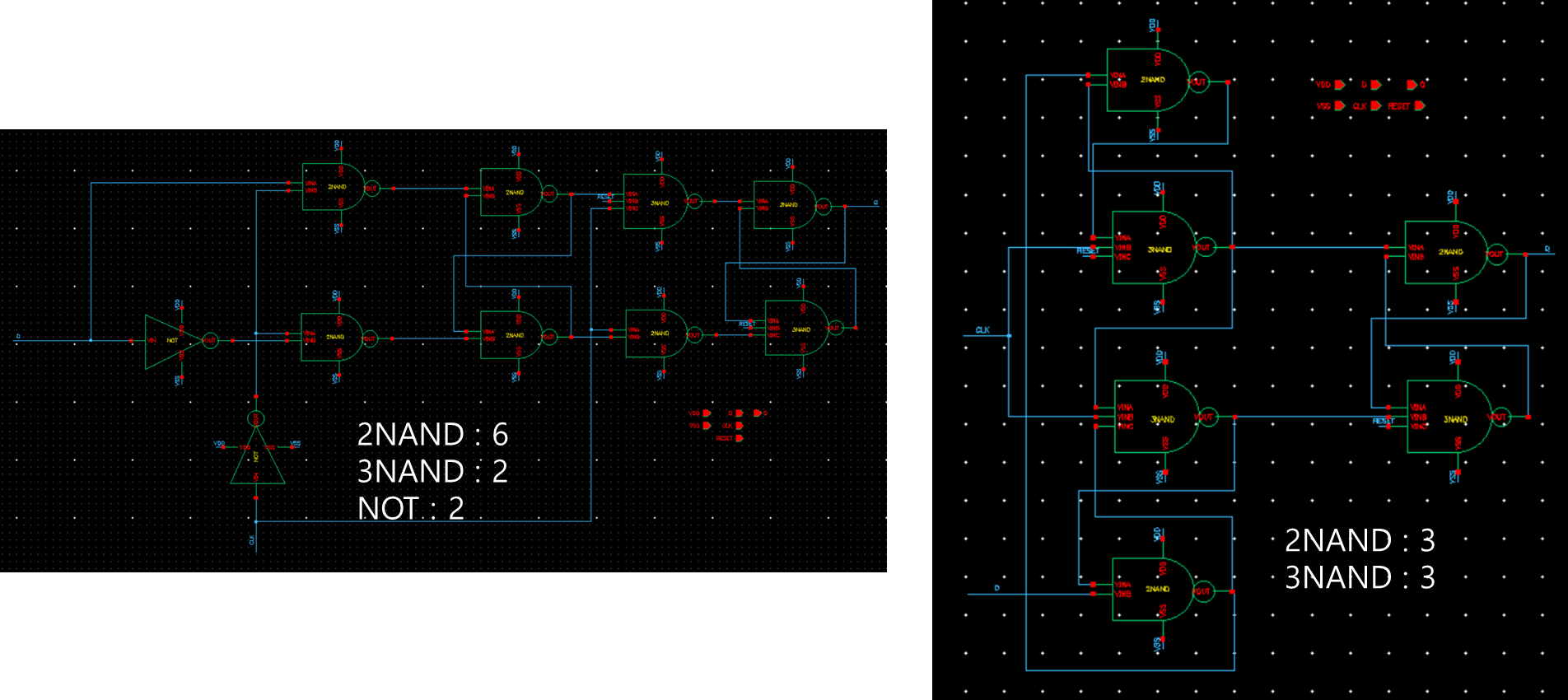

2가지 방식의 DFF를 만들었다.

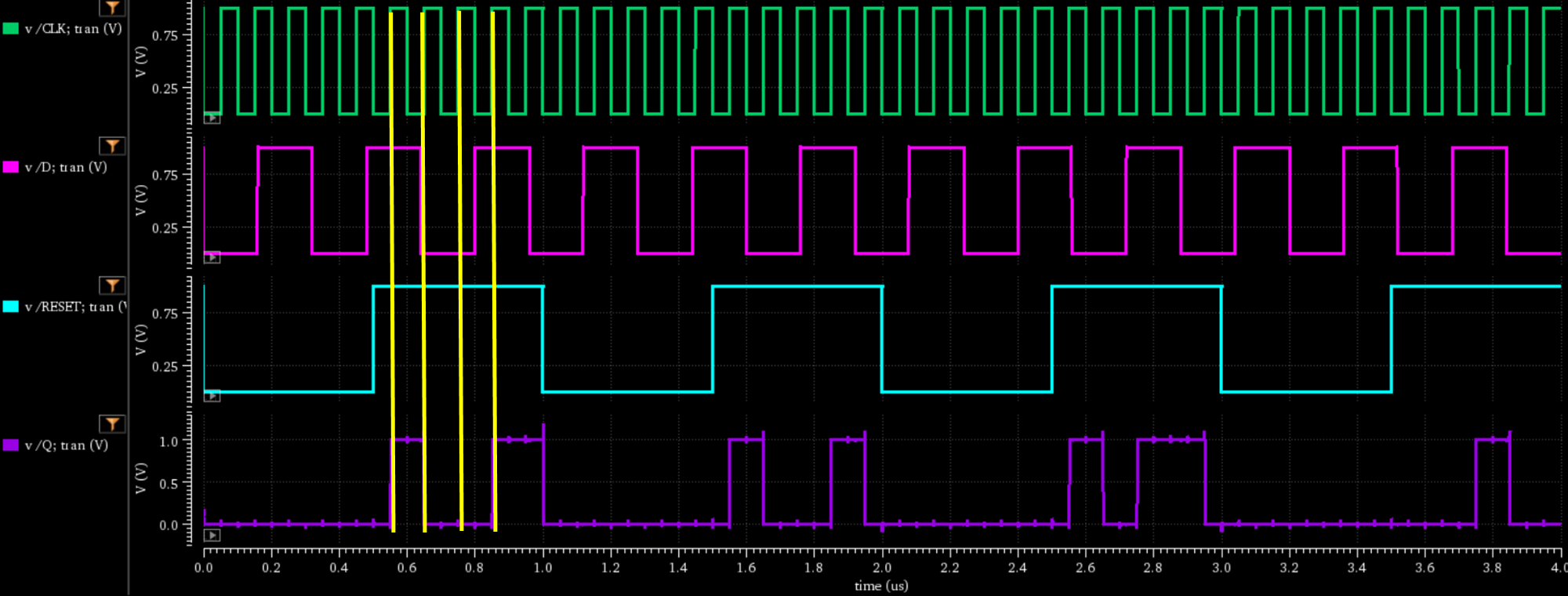

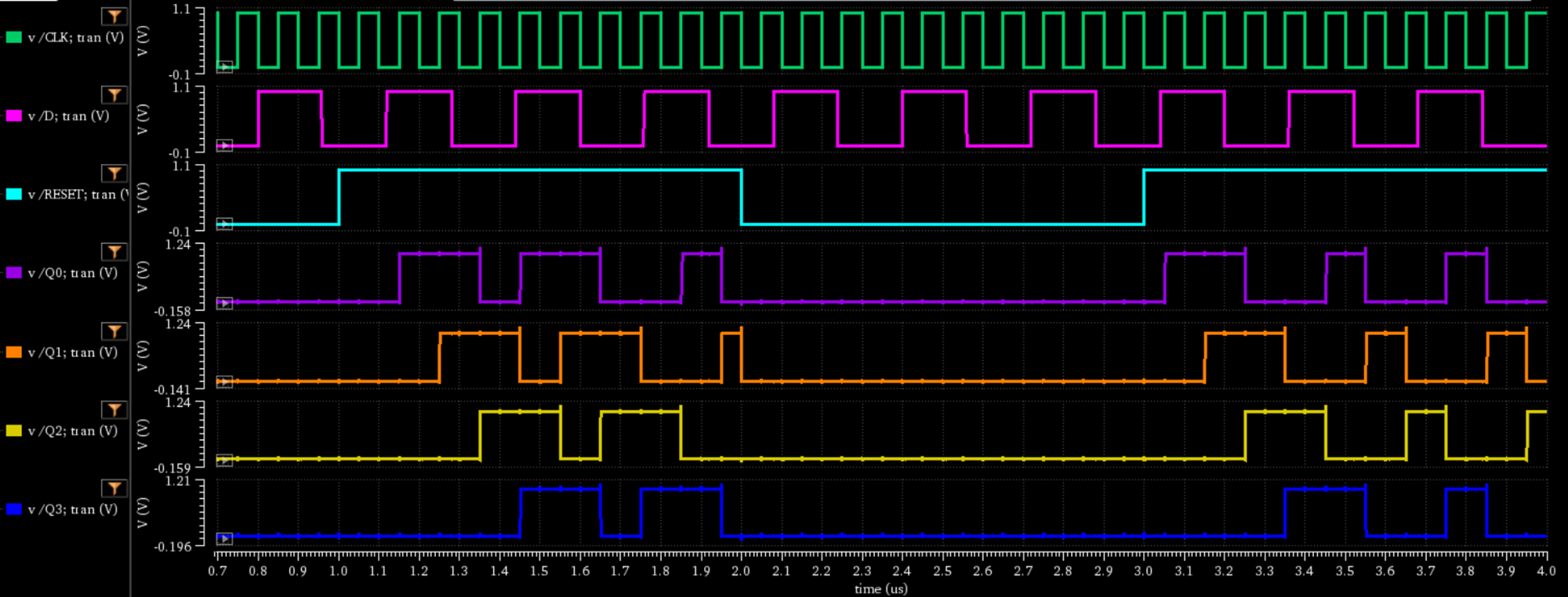

- Simulation

Positive clk edge에서 D가 Q로 반영되고 있다.

- Layout

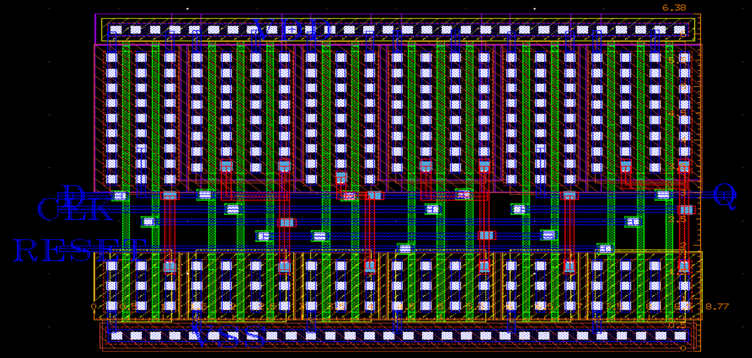

Tr : 40

Area : 83.7161

Tr : 30

Area : 55.9526

더 적은 Tr수를 가진 DFF이 더 작은 Area를 나타낸다.

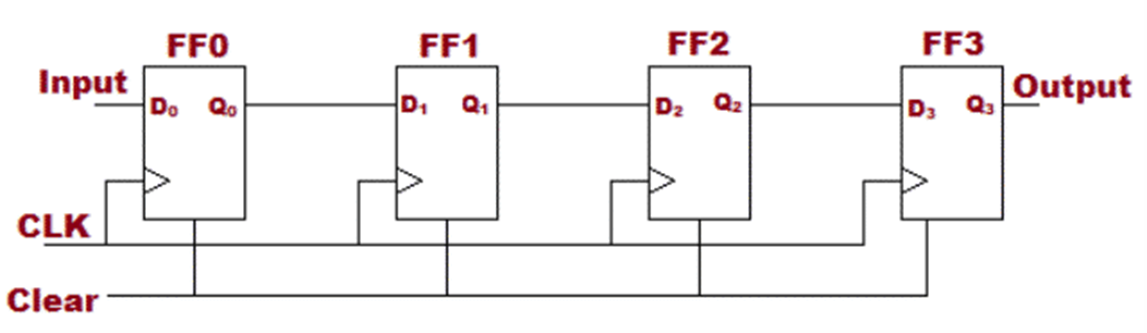

4bit Shift Register

-

Schematic

-

Simulation

-

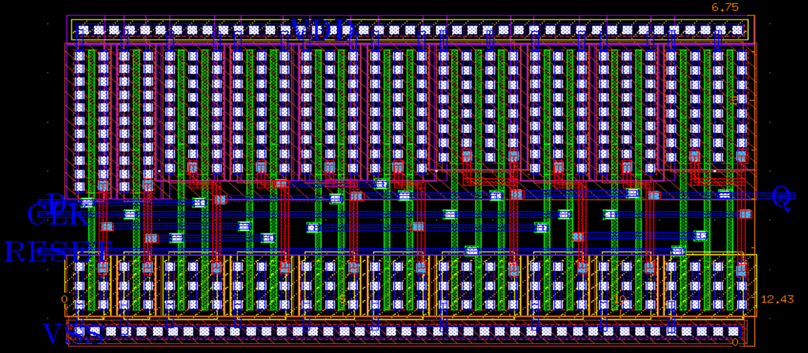

Layout

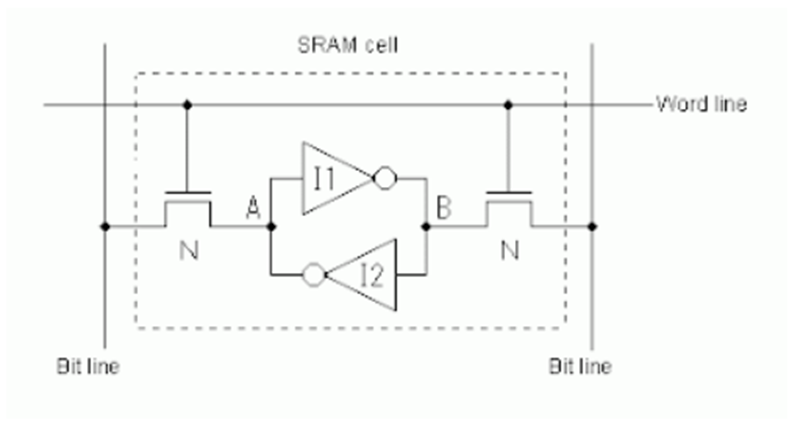

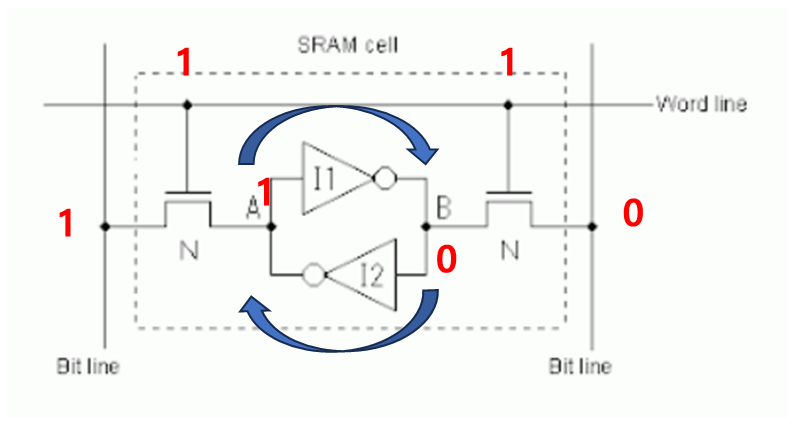

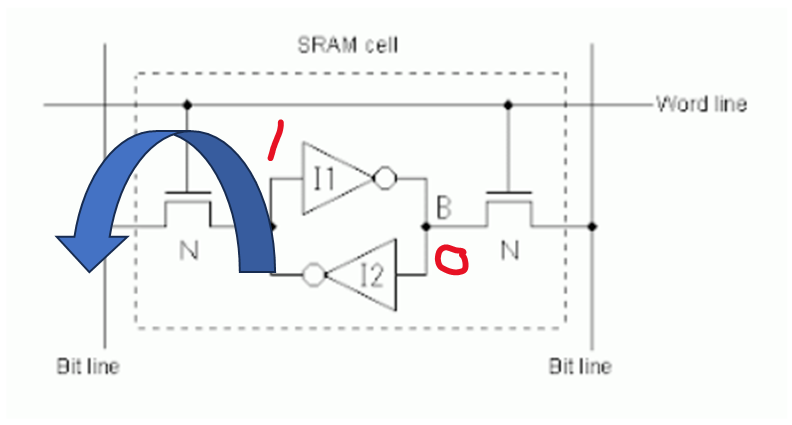

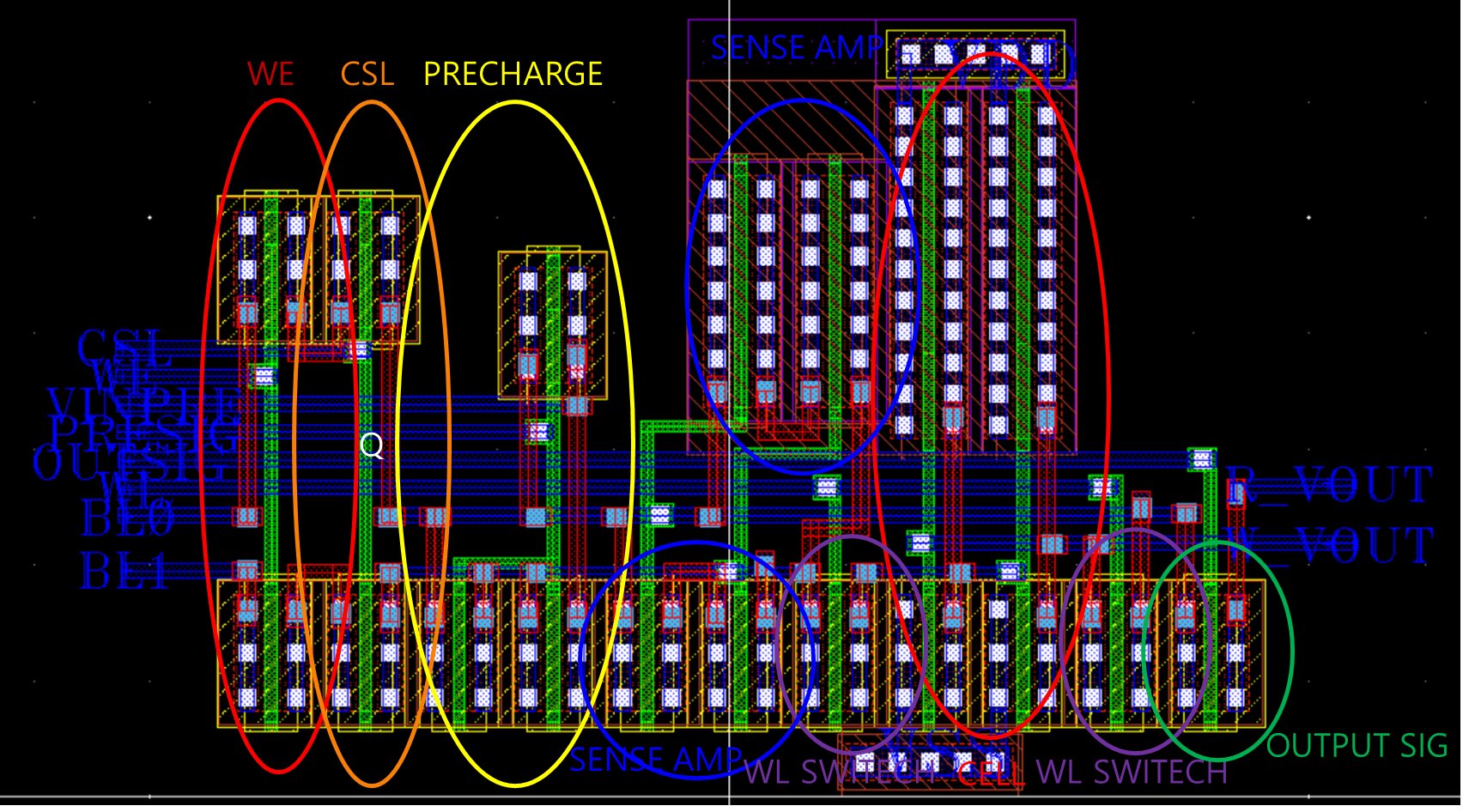

SRAM

Inverter의 Regeneration특징으로 DRAM의 Dynamic한 Leakage특성과 달리 SRAM은 Cross-Coupled Inverter Cell에 Data를 견고하게(Static) 저장할 수 있다.

Bit line에 data를 준비하고 Word line이 On이 되면 Bit line에 있던 data가 cell로 write된다.

cell에 hold된 data를 읽기위해 word line을 On하면 Bit line을 통해 cell의 data를 읽을 수 있다.

-

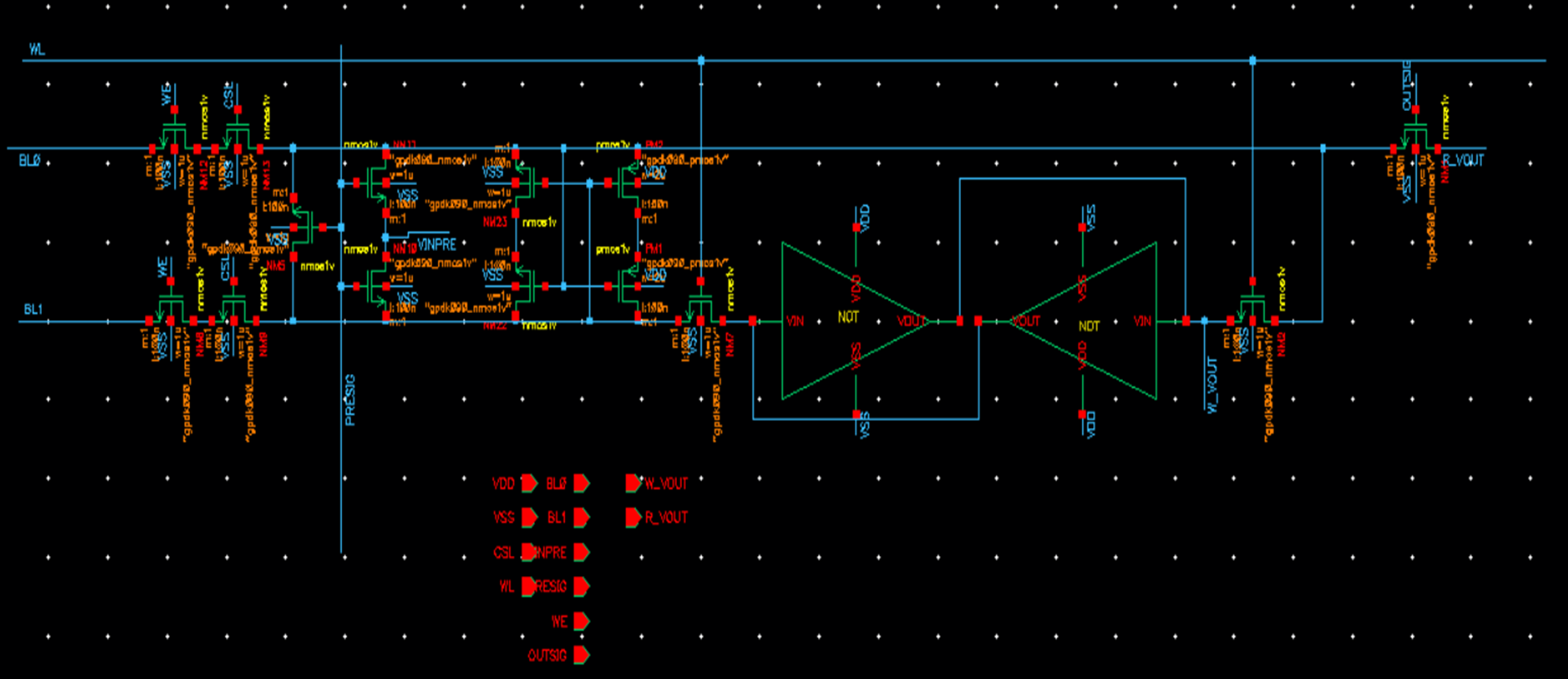

Schematic

-

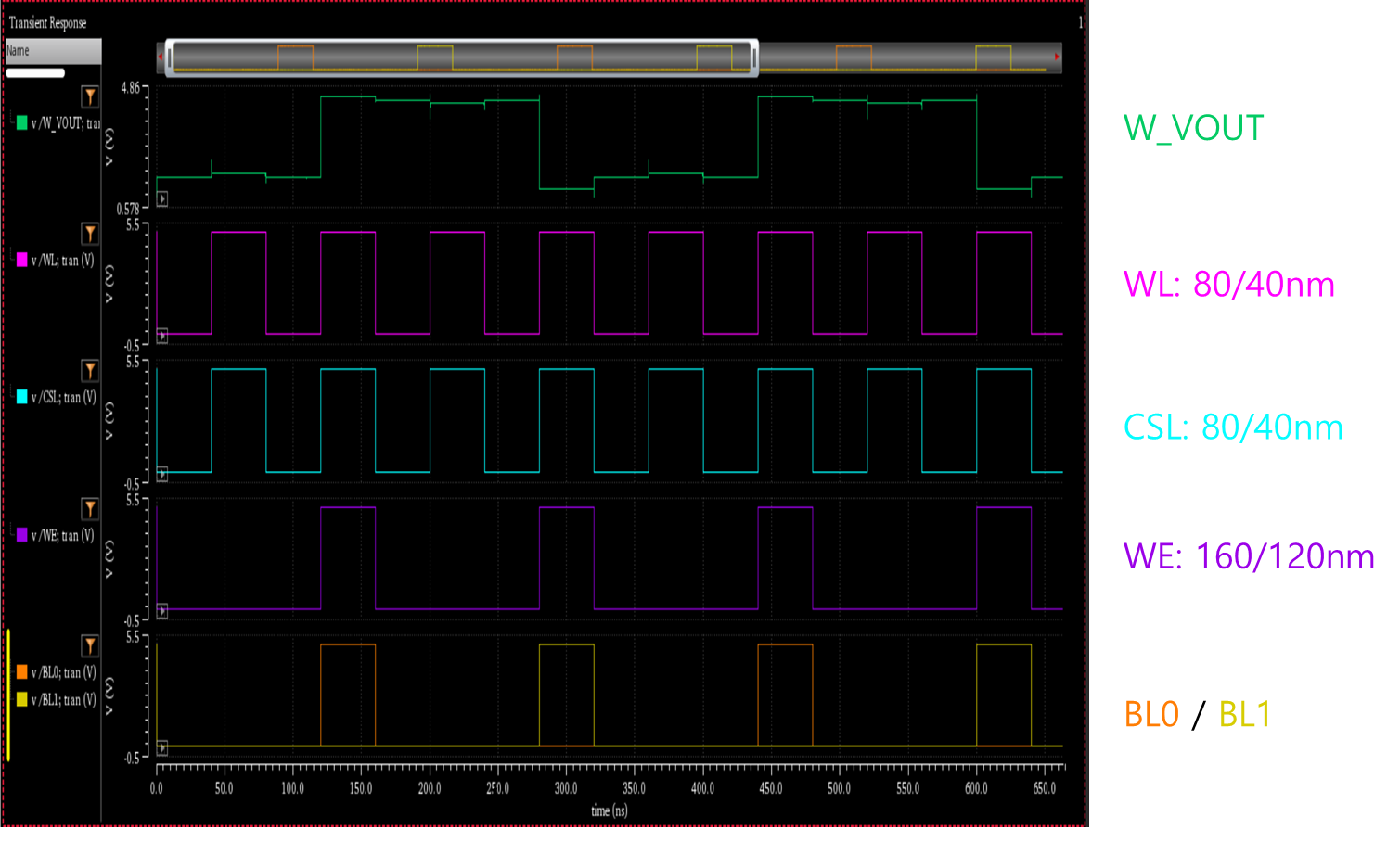

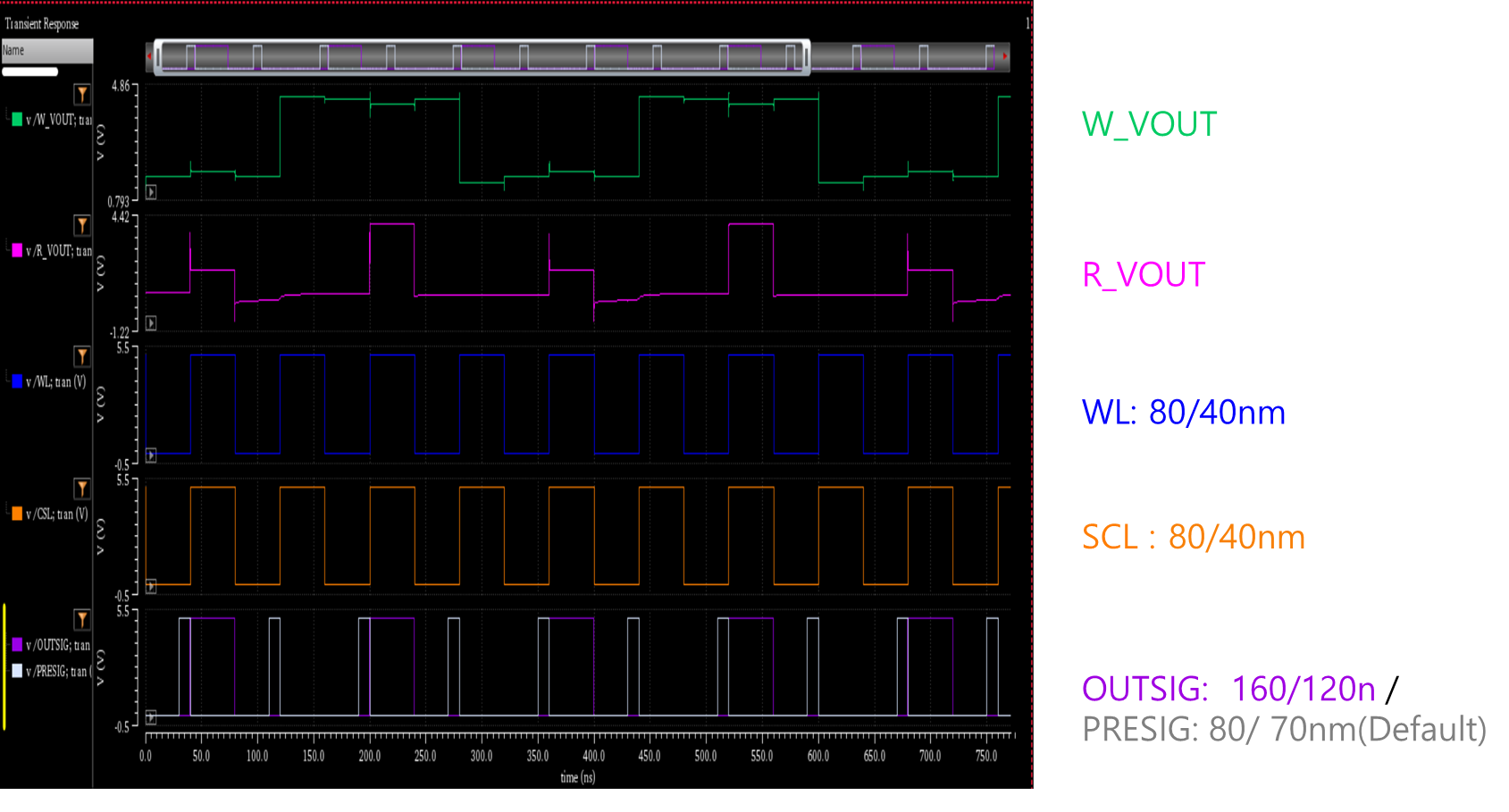

Simulation

- Layout

응@애 나 잘 몰?루