Embedded Recipes 2. ARM Inside

ARM 아키텍쳐 찍먹해보기

ARM 프로세서 기본구조

Mode

동작 모드

- ARM Mode: 32 bit 기본

- Thumb Mode: 16bit 모드

- 예전 시스템 호환되게하는 목적으로 만들었음

User Mode

- 어느 모드를 쓰던 취향대로 사용하면됨

- Normal 모드 (일반모드)

- User - Privileged 모드 (특권모드)

- System

- FIQ

- IRQ

- Supervisor

- Abor

- Undef - 특권모드일때만 동작할 수 있는 상황이 온다.

- 이때 SWI를 이용하여 특권모드로 진입(Supervisor)

- 특권모드에 들어오기만 하면 특권모드 내에서 아무 모드로 변경이 가능하다

ARM Register와 Context

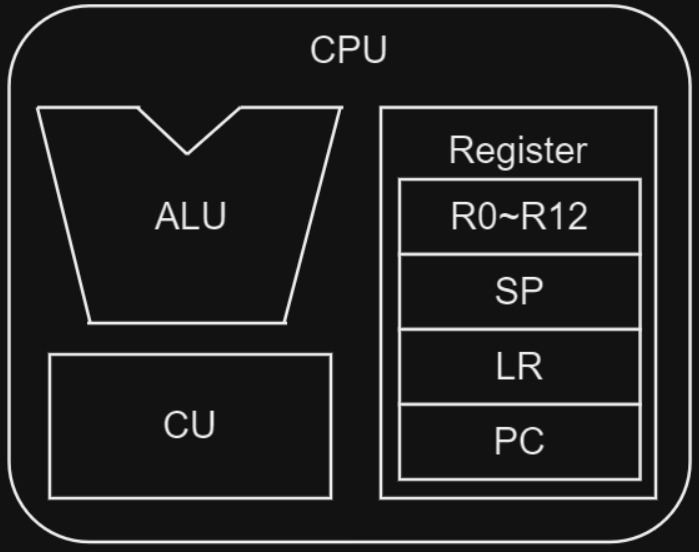

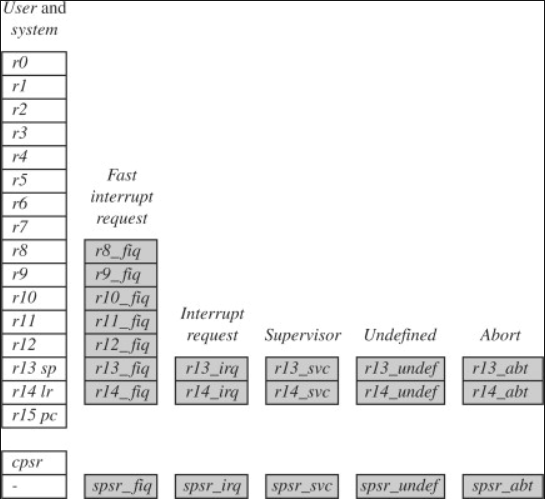

CPU의 레지스터

- General 레지스터

- R0~R7, CPSR, PC

- 어느 모드여도 공통적으로 사용

- Thumb와 ARM 전부 사용하는 레지스터

- ARM에서는 R0~R12 다씀

- - 특수 레지스터

- 위의 것을 제외한 모든것 - R0~R12: 데이터를 담는 레지스터

- R13: SP

- R14: LR

- R15: PC

- CPSR

- SPSR

- 왜 System Mode나 Normal 모드에선 SPSR을 안쓰냐?

- Exception 등을 통한 CTX Switch를 하여 변경된 Mode가 아니라서

백업PSR인 SPSR은 필요가 없음

Task: 프로그램 동작단위

Context: 실행중인 Task 내에 프로그램 동작 상태정보

- 이 레지스터 정보가 결국 프로그램 동작 상태정보

- 그래서 현재 컨택스트는 현재 레지스터 정보이다

ARM Exception과 Modes

위의 유저모드가 변경되는 순간에 오는데

Exception 발생시 변경된다.

Exception이 발생하면 Exception Vector Table이라는 곳에 가서 알맞는 핸들러와 함께 동작한다.

- Vector: Handler

Interrupt는 Exception의 한 종류다

- Exception ( Inteerupt( ) )

Exception들은 어떤 상황에서 발생하는지?

- SVC mode: PoR, SWI

- IRQ mode: Interrupt

- FIQ mode: Fast Interrupt

- ABT mode: 메모리를 잘못 Access했을때

- UND mode: 메모리를 Decode 했는데 Instruction을 못하는 것이 떴을때

Mode는 PSR의 [4:0] 에서 표시됨

Exection 우선순위는 시스템을 크게 망가뜨리는 순위로 매겨져있음

- Reset

- Data Abort

- FIQ

- IRQ

- Prefetch Abort

- Undefined Instruction

- SWI

Exception이 발생하면 무조건 32 bit ARM mode로 변경된다.

mode를 잘쓰면 보안성 강화에 좋다.

Low Vector, High Vector는 뭐임?

- Low Vector

- 아래 주소에 Vector table 두는것

- NOR는 부트로딩을 자체메모리에서 해서 Vector table을 0x00에 둘 수 있음. - Hig Vector

- 0x00 보다 위의 주소에 Vetor table을 두는것

- NAND는 부트로딩 후 RAM에서 동작을 하기 때문에 0x00에 Vector table을 둘수없음

- 그래서 보통 NAND + SRAM 조합으로 설계할때 사용

ARM-Thumb. PCS.

ARM 아키텍쳐에서 레지스터를 사용하는 Standard가 있는데 이게 PCS다.

PCS: Procedure Call Standard

- APCS: ARM PCS

- TPCS: Thumb PCS

- ATPCS: ARM Thumb PCS

- AAPCS: PCS for ARM Architecture (현재 버전)

각 레지스터의 쓰임새를 알아가기전 3가지 용어를 설명해본다.

- Arguement: 파라미터

- Result: 리턴 값

- Scratch: 연습장

R0~ R3(Argument, Result, Scratch)

- 파라미터, 리턴값, 연습장으로 사용됨

- 함수설계시 이 Standard로 인해 파라미터 4개를 넘기지 않아야하는 이유이다.

- 넘어가면 파라미터를 Stack으로 넘겨사용하기때문에 처리가 느려지고 복잡해진다.

R4~R11 (Variable)

- Stack에 Back 하고 끝나기전 복구 시켜줘야함

R12~R15(특수 레지스터)

- R12: IP. 모드변경시 Vaneer를 통해 잠깐 주소 임시 저장소로 활용됨.

- R13 부터는SP, LR, PC

ARM의 Interrupt

Interrupt 가 발생하면 CPU내에 HW로 (GIC나 VIC와 같은 Interrupt Controller)를 통해 처리함.

- Interrupt 발생

- GIC내에 Distributor를 통해 우선순위 체크

- GIC내에 CPU Interface로 CPU와 통신 및 정보 전달

- CPU는 GIC에 Ack를 보내고 CPSR을 확인하여 알맞는 Interrupt 모드로 진입

- Exception Vector Table에서 핸들링

Interrupt Nest

- 인터럽트도 중첩되어 사용되는 경우가 대다수다

- NVIC 라는걸 설계해서 사용하는데, 인터럽트에 각 우선순위를 매겨 사용한다.

ARM SoC

SoC는 용도에 맞게 IP 블럭의 조합을 맞춰 설계된다.

- IP: Intellecture Property

- 지적재산권? 보다는 UART, I2C같은 블럭을 말함 (설계자산)

AMBA

- MCU 버스 아키텍쳐

- IP간 통신 버스 규격이라 보면 됨

- AHB: 빠른 버스

- APB: Periperal 버스 (느린버스)

- ASB: AHB이전에 쓰던 빠른버스

- 브릿지: 속도가 다른 버스간 연결해주는 친구

- AHB <---> 브릿지 <---> APB - Arbiter: 버스시스템의 교통정리를 담당함

- Master가 Arbiter에게 Slave 주소에 대한 Req를 보냄

- Arbiter는 Grant로 허락

- Master가 Decoder를 통해 Slave와 통신