5.1 기억장치의 분류와 특성

기억장치 액세스 : CPU가 어떤 정보를 기억장치에 쓰거나 기억장치로부터 읽는 동작

종류로는 순차적 액세스, 액세스할 위치 근처로 이동한 후 순차적 검색을 통하여 최종 위쳉 도달하는 직접 액세스, 주소에 의해 직접 기억장소를 찾아가기에 어떤 장소든 액세스하는 시간이 동일한 임의 액세스, 특정 비트들을 비교하여 일치하는 내용을 액세스하는 연관 액세스가 있다.

특성

- 기억장치를 설계할 때는 용량과 액세스 속도를 고려해야 한다.

- 주기억장치의 전송단위는 단어(word) 단위 이고, 보조저장장치의 단위는 블록(512byte or 1K byte)단위 이다.

- 주소지정 단위는 주소가 지정된 각 기억 장소 당 저장되는 데이터 길이이다.

- 주소 비트의 수 A와 주소지정 단위의 수 N은 2^A = N의 관계를 가진다.

데이터 전송률

기억장치로부터 초당 액세스 되는 비트 수를 뜻하며,

계산식은 (1 ÷ 액세스 시간) x (한 번에 읽혀지는 데이터 비트 수) 이다.

예를 들어 액세스 시간 = 100ns, 엑세스 단위 = 32비트 일때,

데이터 전송률 = (1 ÷ 100ns) x (32 ÷ 8) = 40Mbytes/sec 이다.

5.2 계층적 기억장치시스템

기억장치 계층

상위층으로 갈수록 비트당 가격이 높아지고, 용량은 감소하며, 액세스 시간이 짧아지고, CPU에 의한 액세스 빈도는 상승한다. 반면 하위 계층으로 내려갈수록 용량은 더 커지고, 비트당 가격은 떨어지며, 지역성의 원리로 인하여 액세스 빈도는 더 낮아진다.

지역성의 원리

- 기억장치의 액세스가 몇몇 특정 영역에 집중되는 현상(첫 번째 계층에 더 많은 액세스)

- 지역성의 원리가 적용되는 경우, 평균 기억장치 액세스 시간이 단축됨

캐시 메모리

주기억장치의 액세스 속도가 CPU에 비하여 현저히 느리기 때문에 주기억장치로부터 데이터를 읽어오는 동안에 CPU가 오랫동안 기다려야 하므로, 그에 따른 성능 저하를 줄이기 위하여 CPU와 주기억장치 사이에 설치 하는 고속의 반도체 기억장치

2-단계 계층적 기억장치

ex) ML1 액세스 시간 = 10ns, ML2 액세스 시간 = 100ns이고, 액세스할 정보가 첫번째 계층 기억장치에 있을 확률= 50%라면...

평균 기억장치 액세스 시간 : (0.5 x 10ns) + (0.5 x 100ns) = 55ns

5.3 반도체 기억장치

5.3.1 RAM(Random Access Memory)

- 임의 액세스 방식

- 반도체 직접회로 기억장치

- 데이터 읽기/쓰기 모두 가능

- 휘발성

DRAM

- 캐패시터에 전하를 충전하는 방식으로 데이터를 저장하는 기억 소자들로 구성 → 집적 밀도가 높다.

- 데이터의 저장 상태를 유지하기 위하여 주기적인 재충전 필요

- 가격이 싸서 용량이 큰 주기억장치로 사용

SRAM

- 기억 소자로서 플립-플롭을 이용 → 집적 밀도가 낮다

- 전력이 공급되는 동안에는 재충전 없이도 데이터 계속 유지 가능

- 가격이 비싸고, 높은 속도가 필요한 캐시 메모리에 사용

용량에 따른 주소 비트 수

ex) 8Kbit RAM

- 1K x 8비트, 주소 = 10비트

- 2K x 4비트, 주소 = 11비트

- 8K x 1비트, 주소 = 13비트

즉 1K = 1024이므로 → 2^10 → 10비트가 필요하고, 2k = 2^1 2^10 → 11비트가 필요하며, 8k = 2^3 2^10 → 13비트가 필요하다.

5.3.2 ROM(Read Only Memory)

- 영구 저장이 가능한 반도체 기억장치

- 읽는 것만 가능, 쓰는 것은 불가능

- 시스템 초기화 및 진단 프로그램, 자주 사용하는 서브루틴, 제어 유니트의 마이크로프로그램등을 저장하는데 사용한다.

5.4 기억장치 모듈의 설계

병렬 접속

- 기억장치 칩의 데이터 I/O 비트 수가 단어 길이보다 적은 경우 사용

- 단어의 길이 = N비트, 기억 장치 칩의 비트 수 = B 라면, N/B개의 칩들 병렬 접속

ex) 단어의 길이가 8비트, 16x4비트 칩들을 이용하여 설계...

모듈 용량 = (16 x 4) x 2개 = 16x8비트 = 16바이트(1바이트 = 8비트)

직렬 접속

- 필요한 기억 장소의 수가 각 기억장치 칩의 기억장소 수보다 많은 경우 사용

ex) 두 개의 16×4비트 칩들을 이용한 32×4비트 기억장치 모듈의 설계

모듈 용량 = 2개 x (16 x 4) = 32x4비트

5.5 캐시 기억장치

CPU와 주기억장치의 속도 차이로 인한 CPU 대기 시간을 최소화 시키기 위하여 CPU와 주기억장치 사이에 설치하는 고속 반도체 기억장치. 주기억장치 (DRAM)보다 액세스 속도가 더 높은 칩(SRAM) 사용하며, 가격및제한된공간때문에 용량이 적다.

적중률 : 캐시에 적중되는 정도(H)

H = 캐시에 적중되는 횟수/전체 기억장치 액세스 횟수캐시의 미스율 = (1 - H)

평균 기억장치 액세스 시간(Ta)

Ta = H x 캐시 액세스 시간(Tc) + 캐시 미스율 x 주기억장치 액세스 시간(Tm)

주기억장치와 캐시의 조직

블록 : 주기억장치로부터 동시에 인출되는 정보들의 그룹

주기억장치의 용량이 2^n 단어, 블록 = K 단어 일 때, 블록의 수는 2^n/K 개

라인 : 캐시에서 각 블록이 저장되는 장소

태그 : 라인에 적재된 블록을 구분해주는 정보

5.5.3 사상 방식

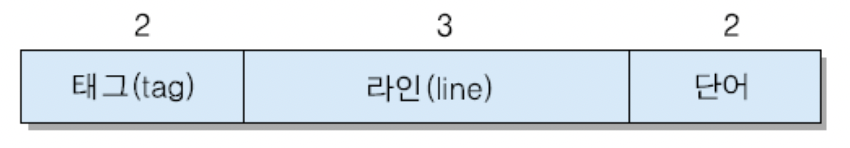

직접 사상

- 각 주기억장치의 블록이 지정된 하나의 캐시라인으로만 적재되는 방식

ex)

주기억장치 용량 = 128바이트 = (2^7) → 주기억장치 주소 = 7비트

블록 크기 = 4바이트 = 2^2 → 블록 개수 = 128/4 = 32개

캐시 라인 크기 = 블록 크기 = 4바이트

캐시 용량 = 32바이트 → 캐시 라인 수 = 32/8 = 8개 = 2^3

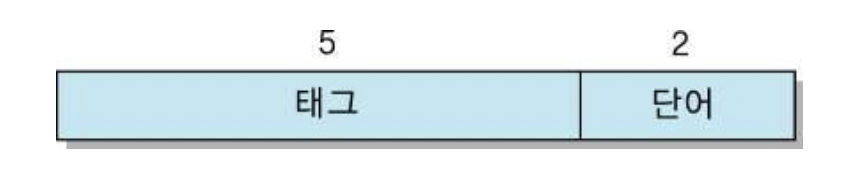

완전-연관 사상

- 주기억장치 블록이 캐시의 어떤 라인으로든 적재 가능

- 태그 필드 = 주기억장치 블록 번호

세트-연관 사상

- 직접 사상과 완전-연관 사상의 조합

- 주기억장치 블록 그룹이 하나의 캐시 세트를 공유하며, 그 세트에는 두 개 이상의 라인들이 적재될 수 있음

5.5.6 다중 캐시

온-칩 캐시 : 캐시 액세스 시간을 단축시키기 위하여 CPU칩 내에 포함시킨 캐시

계층적 캐시

온-칩캐시를 1차(L1)캐시로 사용하고,칩 외부에 더 큰 용량의2 차(L2) 캐시를 설치하는 방식

2-단계 캐시 시스템의 평균 기억장치 액세스 시간 :

Ta = H1 x TL1 + (H2 - H1) x TL2 + (1 - H2) x Tm

만약 H2가 L1에서 미스된 액세스들에 대한 L2의 적중률이라면,

Ta = H1 x TL1 +(1-H1)H2 x TL2 +{1-H1 - (1-H1)H2} x Tm