7.1 시스템 버스

- 컴퓨터시스템의 구성 요소들(CPU, 기억장치, I/O 장치들)을 상호 연결해주는 중심 통로

- 데이터 버스는 양방향 전송이 가능하며, 주소버스는 단방향 전송만 가능하다.

버스 대역폭

- 버스의 속도를 나타내는 척도로서, 단위 시간당 전송할 수 있는 데이터 양을 나타내며, 버스 클록의 주기에 의해 결정.

- 버스클록의 주기 = 50ns(클럭 주파수가 20MHz), 데이터 버스의 폭 = 64비트(8바이트)라면,

버스 대역폭은 8 byte / (50 × 10^-9 sec) = 160Mbytes/sec

7.2 버스 중재

7.3.1 병렬 중재 방식

- 각 버스 마스터들이 독립적인 버스 요구 신호를 발생하고, 별도 의 버스 승인 신호를 받기에 버스 마스터들의 수와 같은 개수의 버스 요구 선 및 승인신호 선 필요

중앙집중식 고정-우선순위 중재방식

- 모든 버스마스터들이 하나의 버스 중재기에 접속

- 중재기와 가까울수록 우선순위

분산식 고정-우선순위 방식

- 모든 버스마스터들이 중재기를 한개씩 보유

- 각 중재기는 더 높은 우선순위를 가진 버스 마스터의 요구 신호들을 받아서 검사하여, 버스 사용 요구를 하지 않 은 경우에만 자신의 버스 마스터로 버스 승인 신호 발생

- 승인 신호를 받은 버스마스터는 BBUSY신호를 검사 후 사용 시작

가변 우선순위 방식

- 시스템의 상태(또는조건)에 따라 각 버스마스터들의 우선 순위를 계속 변화시키는 방식

- 중재 회로가 복잡하다는 단점이 있으나. 모든 마스터들이 공정하게 버스를 사용할 수 있게 해준다.

- FIFO알고리즘을 사용하는 동등 우선순위 방식, 임의 우선순위 방식, 최소-최근 사용 방식이 있다.

7.3.2 직렬 중재 방식

- 버스 요구와 승인 신호선이 각각 한개씩만 존재하며,각 신호선을 버스 마스터들 간에 직렬로 접속하는 방식

중앙집중식 직렬 중재 방식

- 하나의 버스 사용승인 신호선(BGNT)이 데이지-체인 형태로 모든 버스 마스터들을 직렬로 연결

- 우선 순위는 버스승인 신호선이 연결된 순서대로 결정

- 만약 버스사용을 요구하지않은 상태라면, 승인 신호를 다음에 연결된 마스터로 통과

분산식 직렬 중재 방식

- 데이지-체인 버스 승인 신호선으로 버스 중재기들을 순환형으로 접속

- DBGNT 신호를 받은 마스터가 버스요구를 하지않은 상태라면, 그 신호를 우측의 다음 중재기로 통과

- 어느 한지점에만 결점이 생겨도, 시스템 전체에 영향

7.3.3 풀링 방식

버스 사용을 원하는 마스터가 있는지를 버스 중재기가 주기적으로 검사하여 사용 승인 여부를 결정

7.3 I/O 장치의 접속

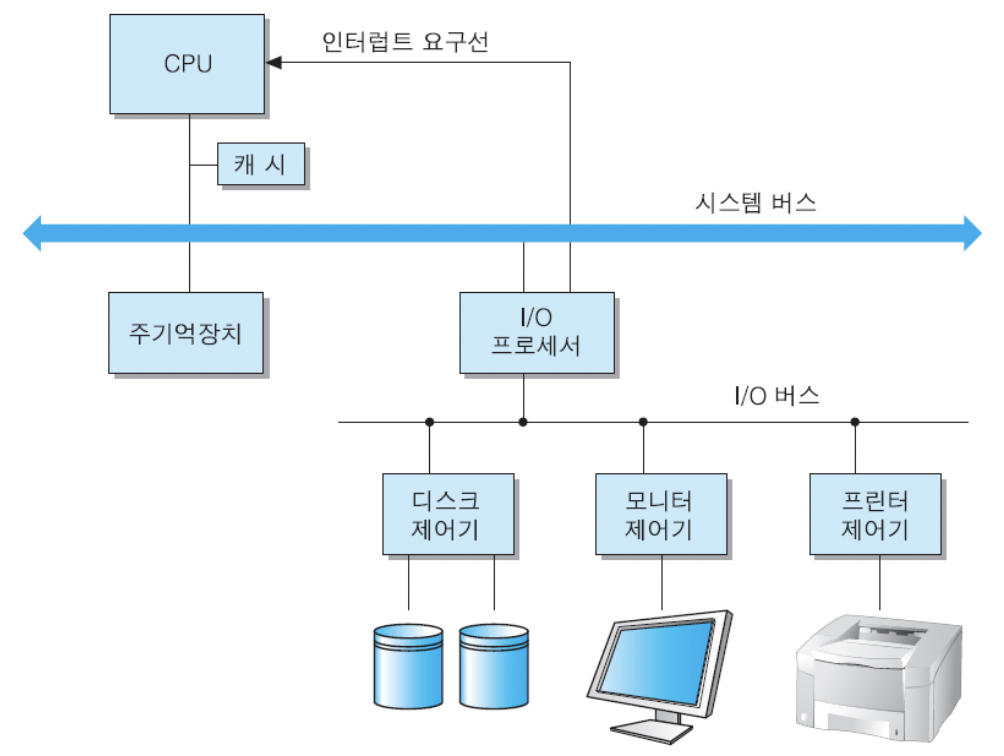

- I/O장치는 그 종류가 다양해 CPU에 모든 제어회로를 포함시킬 수 없고, 데이터 전송 속도와 데이터 형식의 길이가 서로 다르기에 시스템 버스에 직접 접속되지 못한다. 이에 I/O제어기를 사용해야만 한다.

프로그램을 이용한 I/O

- CPU가 반복적으로 I/O 장치의 상태를 검사하면서 I/O 동작을 처리하는 방식

- 간단하다는 장점이 있으나, CPU가 I/O동작에 직접 관여해야 하므로, 그 동안에 다른일을 하 지 못함

기억장치-사상 I/O 주소 지정 방법

- 기억장치 주소 영역의 일부분을 I/O 제어기 내의 레지스터들의 주소로 할당하는 방식

- LOAD 명령어 등 프로그래밍 명령어를 사용할 수 있으며, 별도의 I/O 제어신호가 필요 없다.

- ex) 주소 비트 = 10비트, 전체 기억장소 수 = 1024 일 때

0 ~ 511번지 : 기억장치에 할당, 512 ~ 1023번지(I/O 장치들에 할당)

분리형 I/O 주소 지정 방법

- I/O 장치 주소공간을 기억장치 주소 공간과는 별도로 할당 하는 방식

- 별도의 I/O 명령어를 사용하고, 별도의 제어 신호가 필요하다.

- ex) 주소 비트 = 10비트일 때

기억장치와 I/O장치 각각 1024개씩 할당

7.4 인터럽트를 이용한 I/O

- 인터럽트 메커 니즘을 이용함으로써, I/O 동작이 진행되는 동안에 CPU가 다른 작업을 처리할 수 있도록 하는 방식

- 각 I/O 제어기와 CPU 사이에 별도의 인터럽트 요구선(INTR)과 인터럽트 확인선(INTA)을 접속하는 방법인 다중-인터럽트 방식, CPU로부터 발생되는 INTA 출력선을 I/O 제어기들에 직렬로 접속해 AIn 입력 값에 따라 결정하는 데이지-체인 방식, CPU가 모든 I/O 제어기들에 접속된 TEST I/O 선을 이용 하여 인터럽트를 요구한 장치를 검사하는 소프트웨어 풀링 방식이 있다.

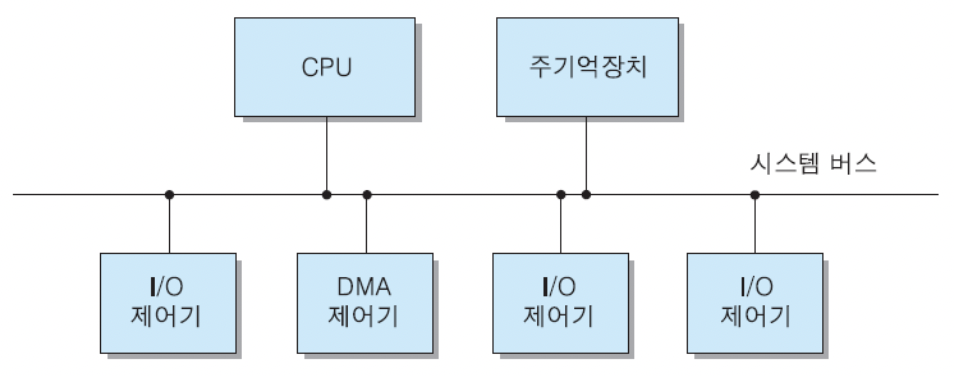

7.5 직접기억장치액세스(Direct Memory Access)

- CPU의 개입 없이 I/O 장치와 기억장치 사이에 데이터를 전송하는 방식

- CPU가 주기억장치를 액세스하지 않는 시간 동안에 시스템 버스를 사용하여 주기억장치와 I/O 장치 간에 데이터 전송

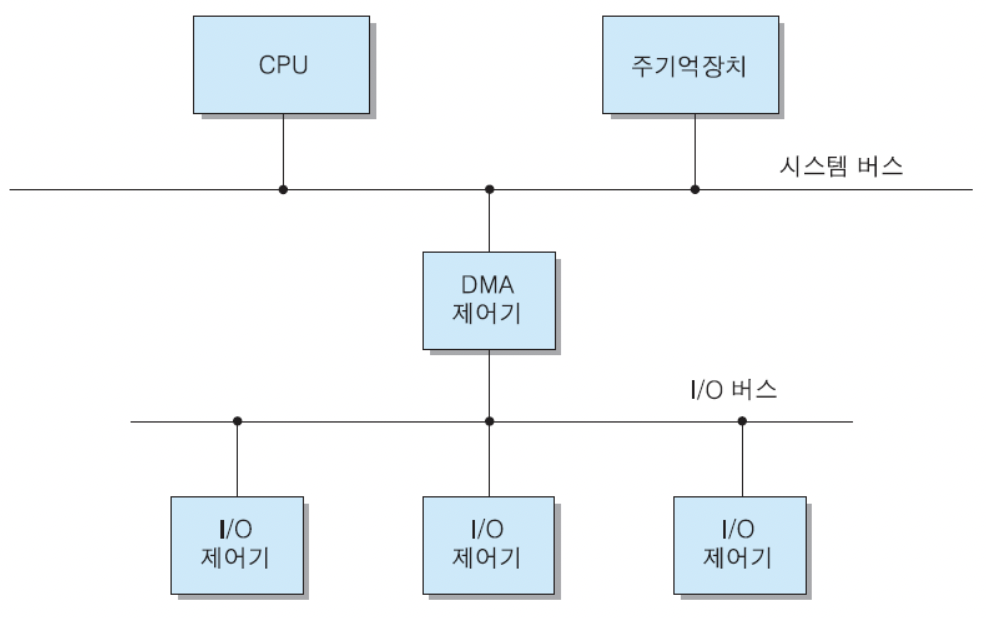

I/O + DMA

하지만 DMA는 각 데이터 전송 때마다 시스템버스를 두 번씩사 용한다는 단점이 있고, 이는 버스 사용량 증가로 인한 시스템 성능 저하문제를 발생시킨다. 이를 해결하기 위해 I/O 장치들을 DMA 제어기에 접속시켜 DMA 제어기가 주기억장치를 액세스 할 때만 시스템 버스 사용하도록 한다.

하지만 I/O는 복잡하기에 DMA제어기로만 지원하는 데는 한계가 있고, 이에 IOP(I/O Processor)를 사용한다.