지난 이야기

지난 포스트는 Q, Qb의 성질을 이용한 JK filpflop과 전가산기 4개를 연결한 4가산기를 설계했었다. verilog도 또한 virtuoso와 궤를 같이하여 라이브러리를 생성해 추후 더 큰 규모의 작품을 설계하는 것에 사용할 예정이다.

MUX(multiplexer)

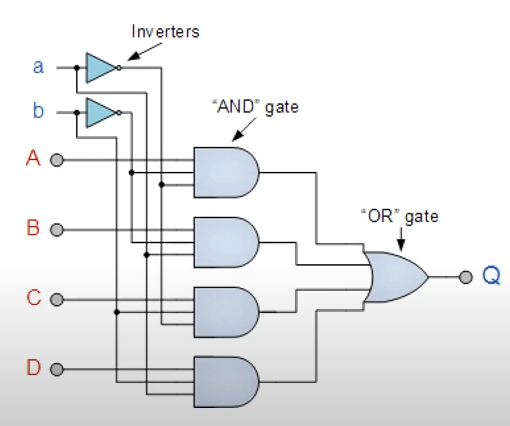

멀티 플렉서, MUX는 encoder, decoeder는 디코더로 사용할 수 있다. 인코더는 데이터를 가공하여 1차원 낮은 규칙으로 동작하는 데이터로 변환하며, 디코더는 데이터를 다시 1차원 높이, 인코딩된 규칙을 역전시켜서 이전으로 되돌리는 역할을 한다. 멀티 플렉서에서 설계자는 input과 output, encoder 신호 3가지를 설정해야만 작동한다. 또한 인코더와 디코더의 작동 기작, 결과는 완벽히 반대이다.

| 신호 | 인코더 | 디코더 |

|---|---|---|

| input | 2^n개의 데이터를 입력 | 1개의 데이터만 입력 |

| output | 1개의 데이터 출력 | 2^n개의 데이터 출력 |

| en | log2(2^n)개의 올림 정수 갯수 NOT/wire 입력 | log2(2^n)개의 올림 정수 갯수의 NOT/wire입력 |

<표 1>

표를 토대로 디지털 논리회로를 구성해보면, 다음과 같다.

- encoder logic

- encoder logic table

| A | B | C | D | a | b | F | |

|---|---|---|---|---|---|---|---|

| X[0] | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| X[1] | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| X[2] | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| X[3] | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

<표 2>

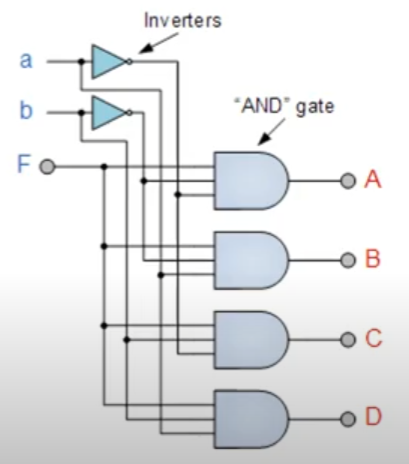

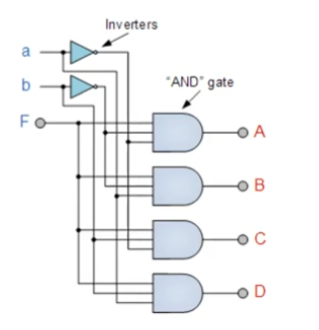

- decoder logic

- decoder logic table

| F | a | b | A | B | C | D | |

|---|---|---|---|---|---|---|---|

| X[0] | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| X[1] | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| X[2] | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| X[3] | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

<표 3>

두 논리회로에서, encoder는 입력, deconder는 출력 신호들의 배열 내 인덱스들이 모두 같은 값을 지니고 있다. 따라서, 4비트 신호로 규정하지 않아도 1비트로 충분하게 표현할 수 있으므로, ABCD는 1비트로 규정해도 무방하다.

주목해 볼 것은 바로 deconder의 부분이다. [3:0]F가 입력되었을 때, F[0] = A, F[1] = B, F[2] = C, F[3] = D로 나타난다. 즉, 포인터의 역할도 일부 가능하다고 볼 수 있다.

주의할 점은, 인코더와 디코더 모두 신호 en이 모두 같아야만 동일 데이터를 인코딩, 디코딩 가능하다는 것을 알아야만 한다. 생각해보면, 인코딩, 디코딩 도중 <표 1>에서 언급했던 것처럼 일정 규칙에 의거하여 작동하는 것을 볼 수 있다. 또한, 입력이 2^n 꼴이 아니더라도, log2(X)개의 올림만큼의 NOT/Wire 게이트를 사용하여 en신호를 준다면, 인/디코딩이 가능하다. 단, 출력은 [N-1:0]F 꼴로 출력될 것이다.

- 2x4 deconder 코드

module dec2x4(en, x, y);

input en;

input [1:0] x;

output [3:0] y;

wire w0, w1;

not n0 (w0, x[0]);

not n1 (w1, x[1]);

and a0 (y[0], en, w0, w1);

and a1 (y[1], en, x[0], w1);

and a2 (y[2], en, w0, x[1]);

and a3 (y[3], en, x[0], x[1]);

endmodule- 2x4 deconder testbench

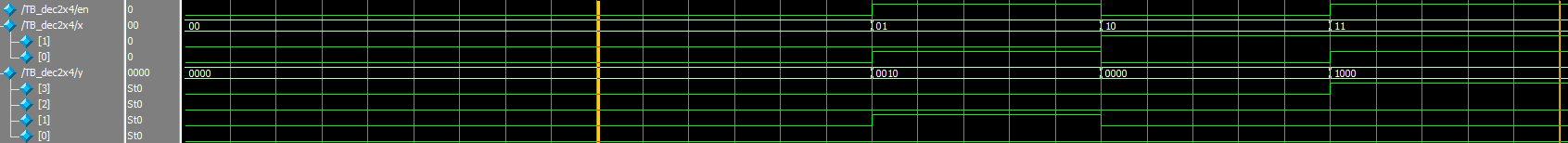

`timescale 1ns/1ps

module TB_dec2x4;

reg en = 1'b0;

reg [1:0] x = 2'b00;

wire [3:0] y;

//wire w0, w1;

dec2x4 inst_dec2x4(.en(en), .x(x), .y(y));

initial begin

#10;

x = 2'b00; en = 1'b0; #5;

x = 2'b01; en = 1'b1; #5;

x = 2'b10; en = 1'b0; #5;

x = 2'b11; en = 1'b1;

end

endmodule

이 그래프는 2X4 디코더이다. en 신호, 즉 인코딩된 2비트 신호가 5ns마다 들어올 때, 디코더 [1:0]x가 해석하면서 [3:0]y의 신호를 발생시키는 코드이다.

그래프를 분석해 보면, en = 4d'0101 가 입력되었을 때, y[1], y[3] = 1, 나머지는 0인 [3:0] y = 4'b0101이 출력됨을 알 수 있다.